## MIXED SIGNAL CIRCUIT DESIGN ORAL NOTES

This work is licensed under Creative Commons CC-BY-NC-SA-4.0

## Guide to these notes:

- If you payed for these notes, you've been scammed. I always give my notes for free

- I tried to explain and justify every step of each question, I hope you can follow my reasonings. If there's something that's "taken for granted", it means it was discussed in previous courses (i.e. fundamentals of electronics or analog circuit design)

- Even though the oral hasn't a list of questions to be asked, I made one. It was handy to me.

- PDFs contain typos so beware of that!

- Tip: do not go straight to the point during the oral. When you're asked a question give context. It does not make sense to start talking about the circuit implementation of a BGR if you first didn't explain what principle (positive/negative temperature coefficient combination) is behind that. It also does not make sense to explain how to design a Common Mode Feedback circuit if you don't know why it's there (i.e. fully differential circuits simply DO NOT WORK without that, CMF isn't used just to reduce the common mode gain, that's just a pleasant consequence). This will also help you structuring the oral

- if my writing isn't clear, well, I'm sorry C: hope it helps anyway. Also, I speak maccheroni and I'm well aware of the English mistakes I made. My priority was to have a clear understanding of the topics.

- At some point the index number of a question in the scanned document does not reflect the one of the table of contents. Nevermind, use bookmarks and the real pages!

If you're having any issue with this document just send an email to giacomo.tombolan@mail.polimi.it

## LIST OF QUESTIONS

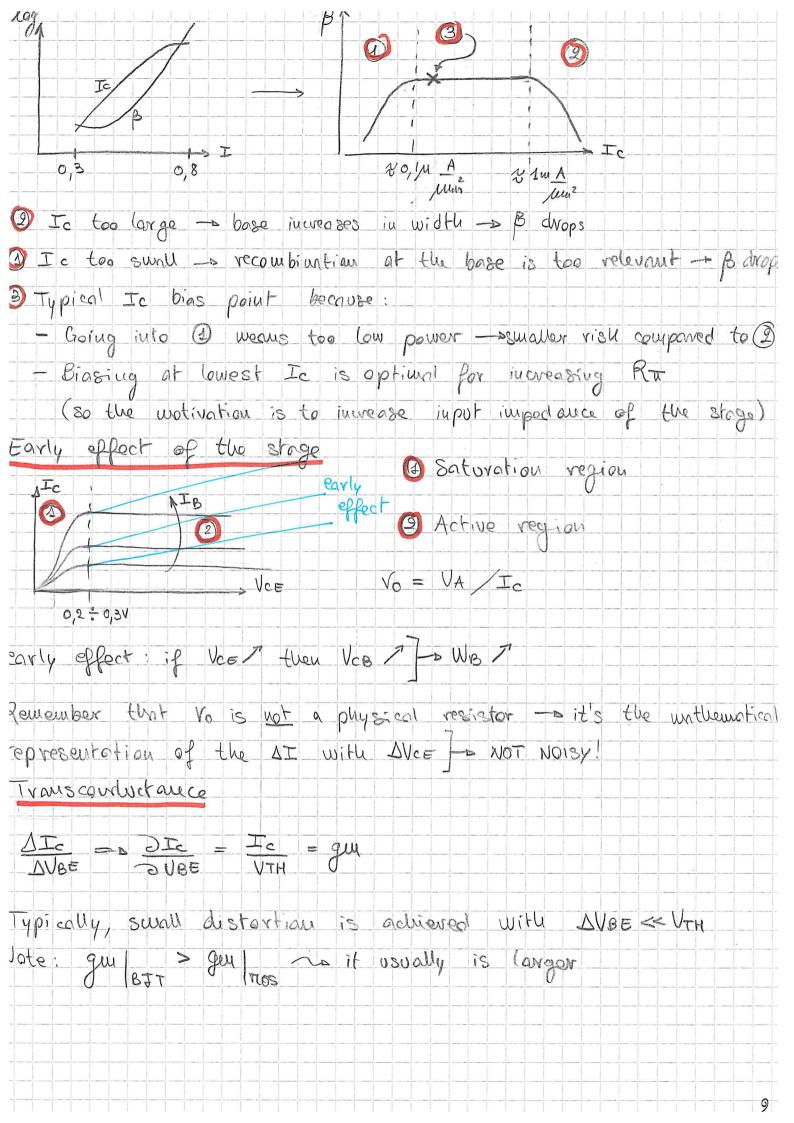

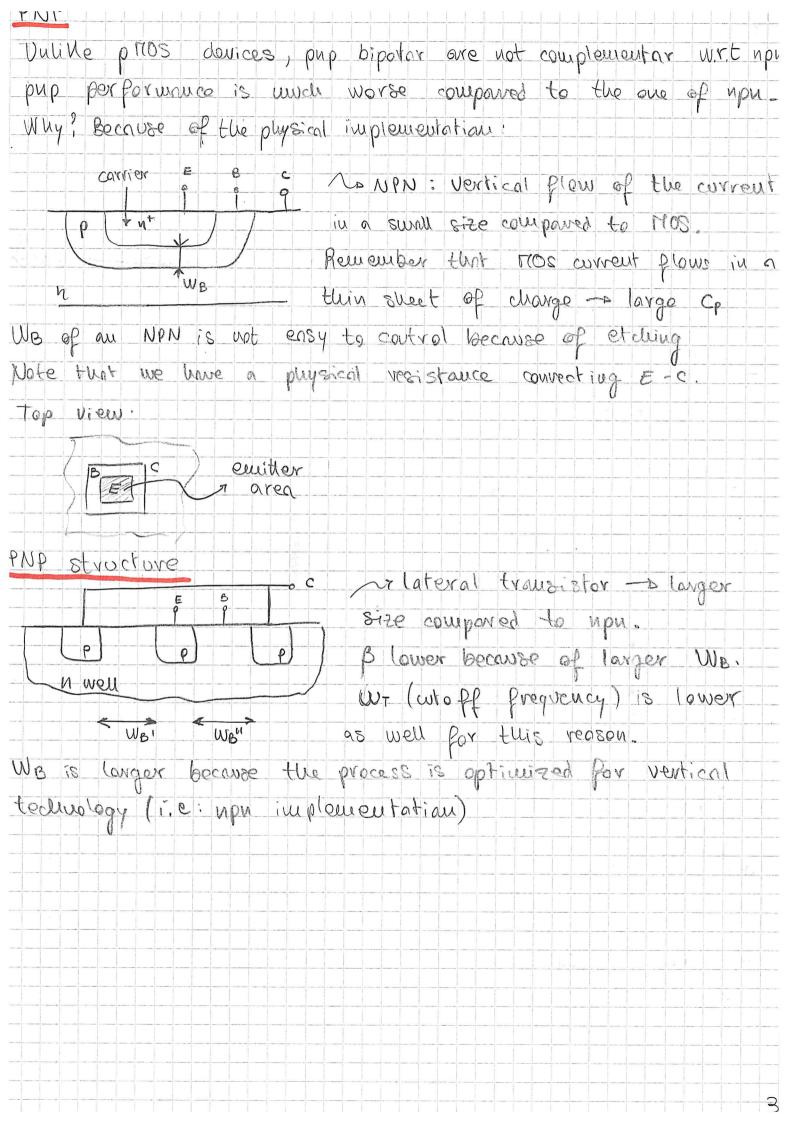

- 1. Review of BJT devices: npn, pnp transconductance, early effect and physical implementation

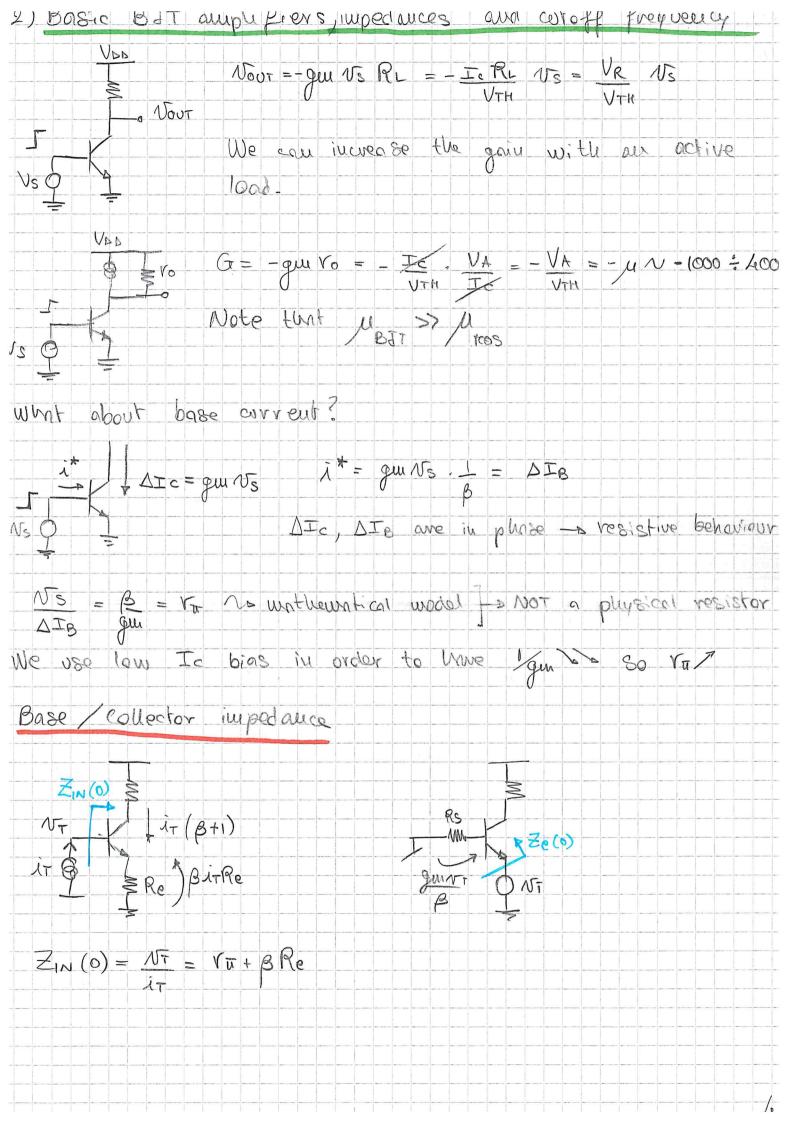

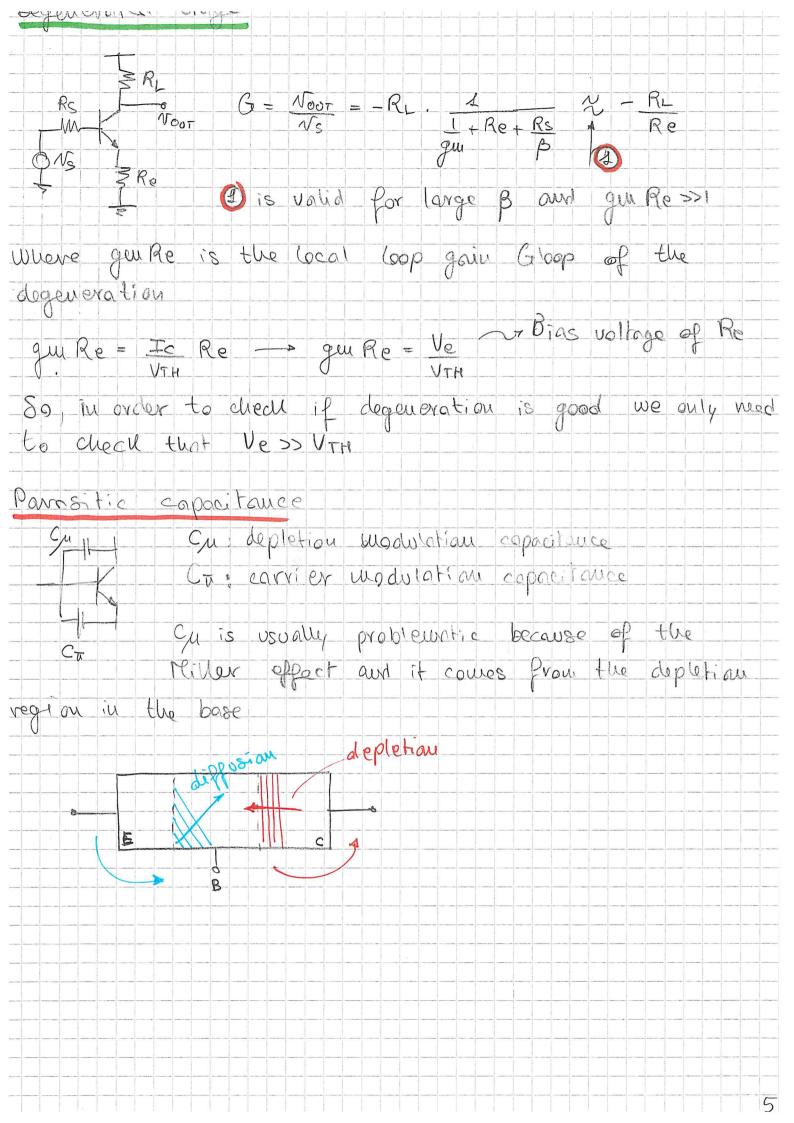

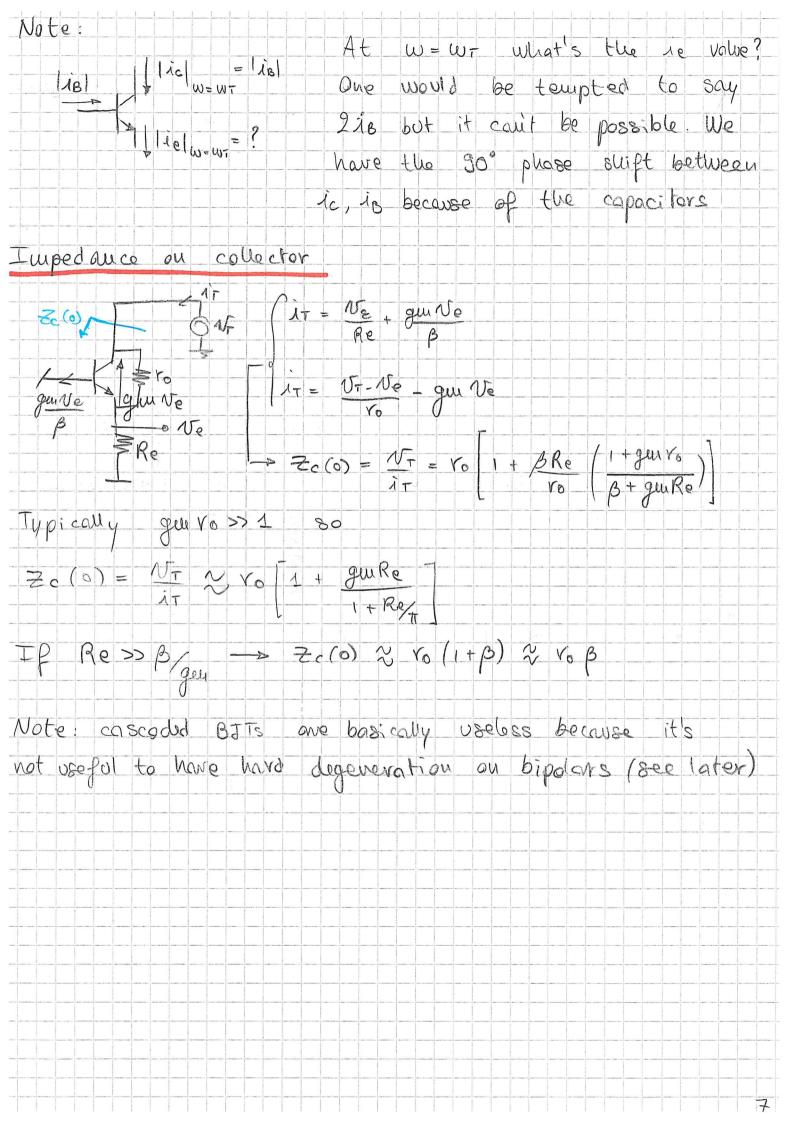

- 2. Basic BJT amplifiers, equivalent impedances and cutoff frequency for bipolar devices

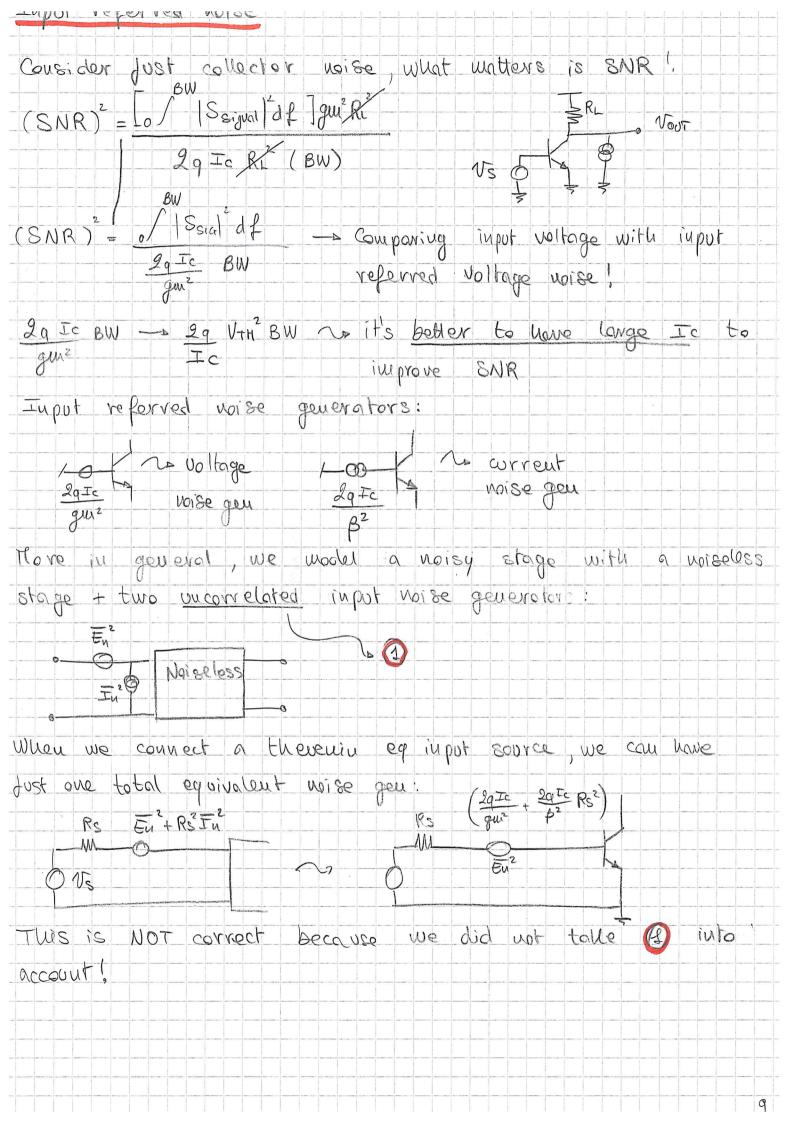

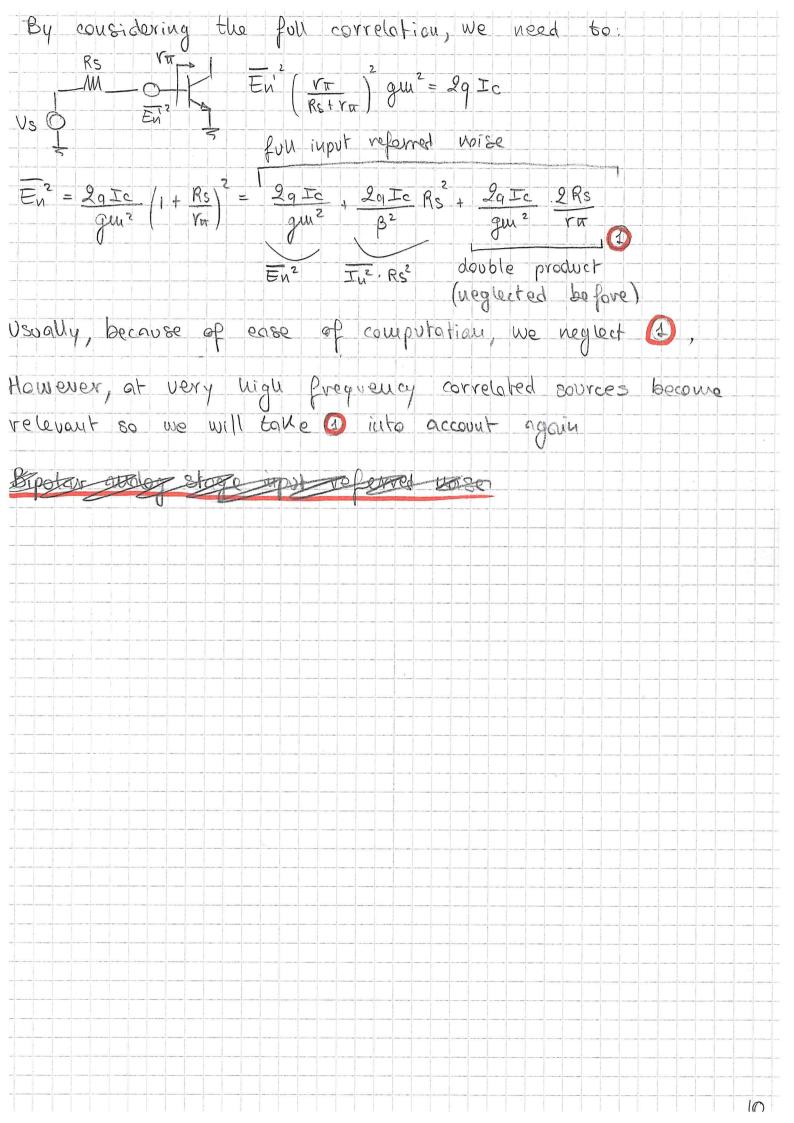

- 3. Noise in bipolar analog stages: input referred noise and correlation between input current and voltage noise sources

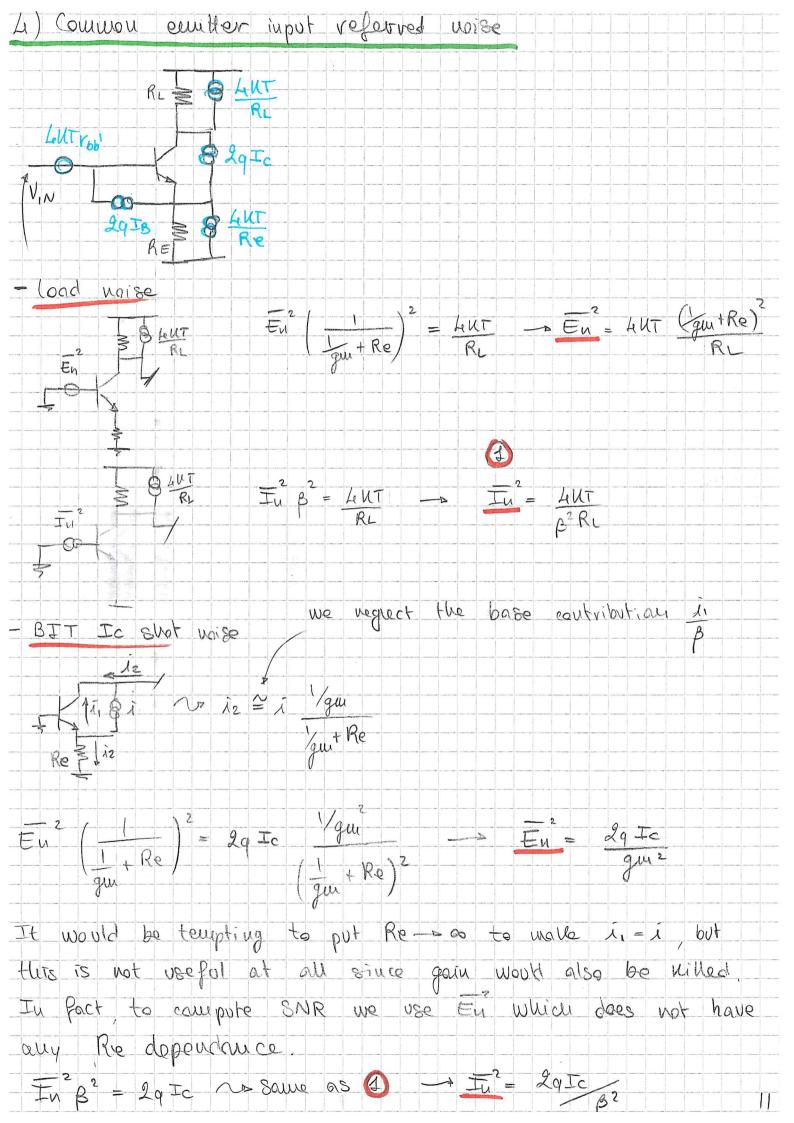

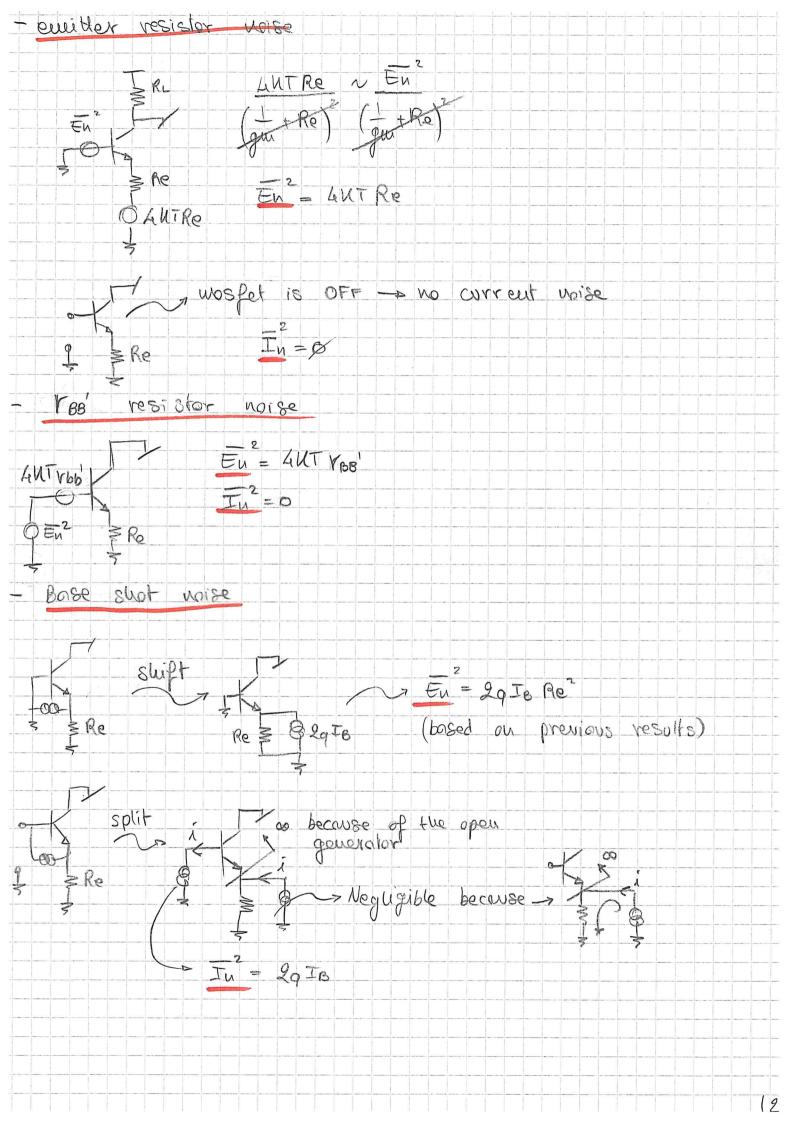

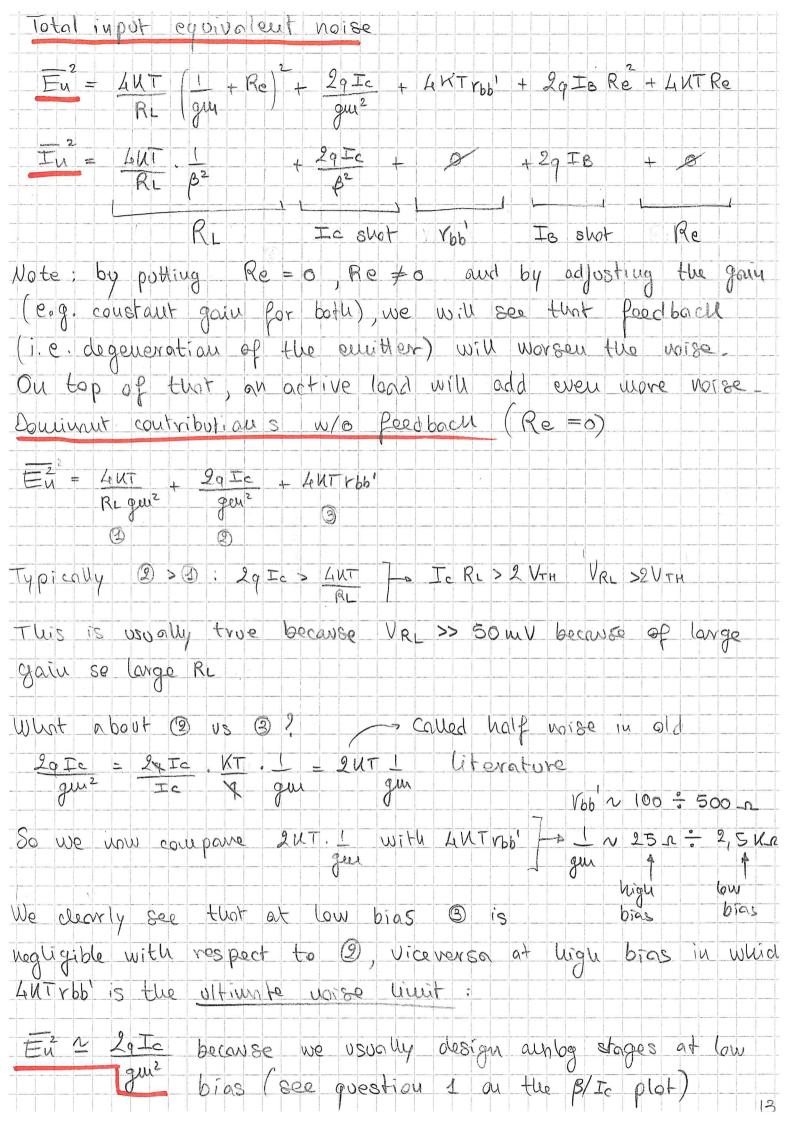

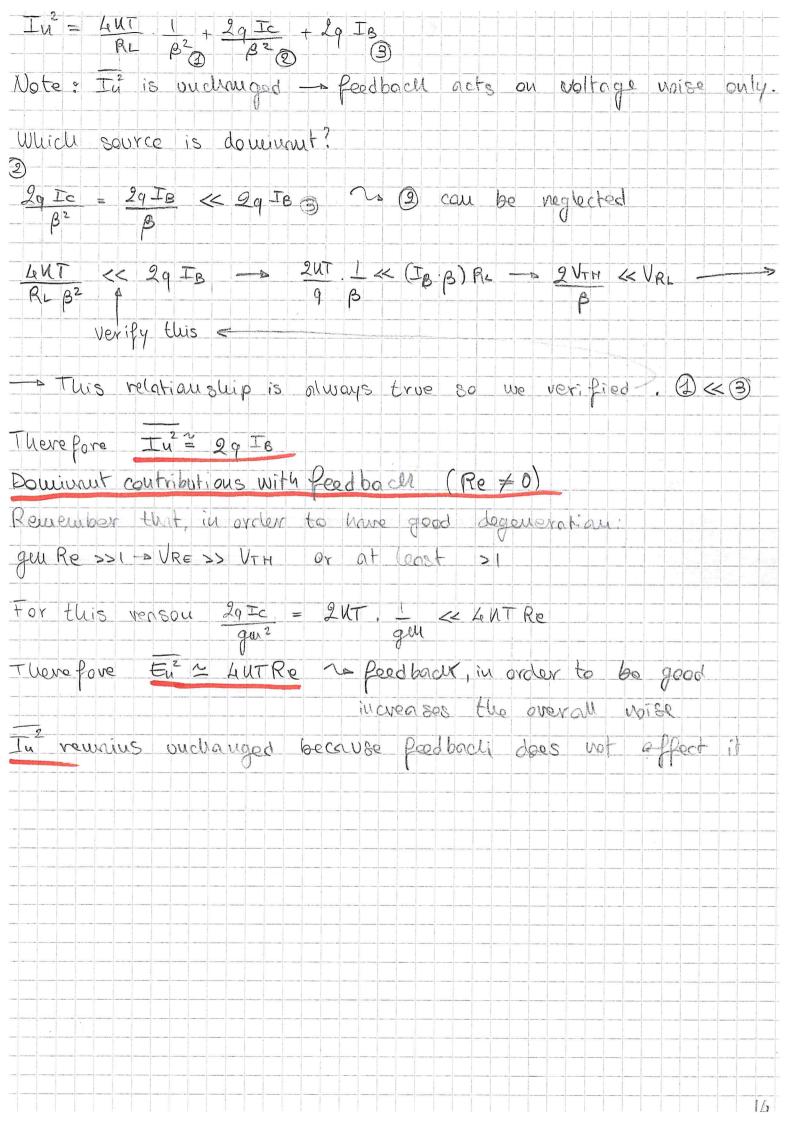

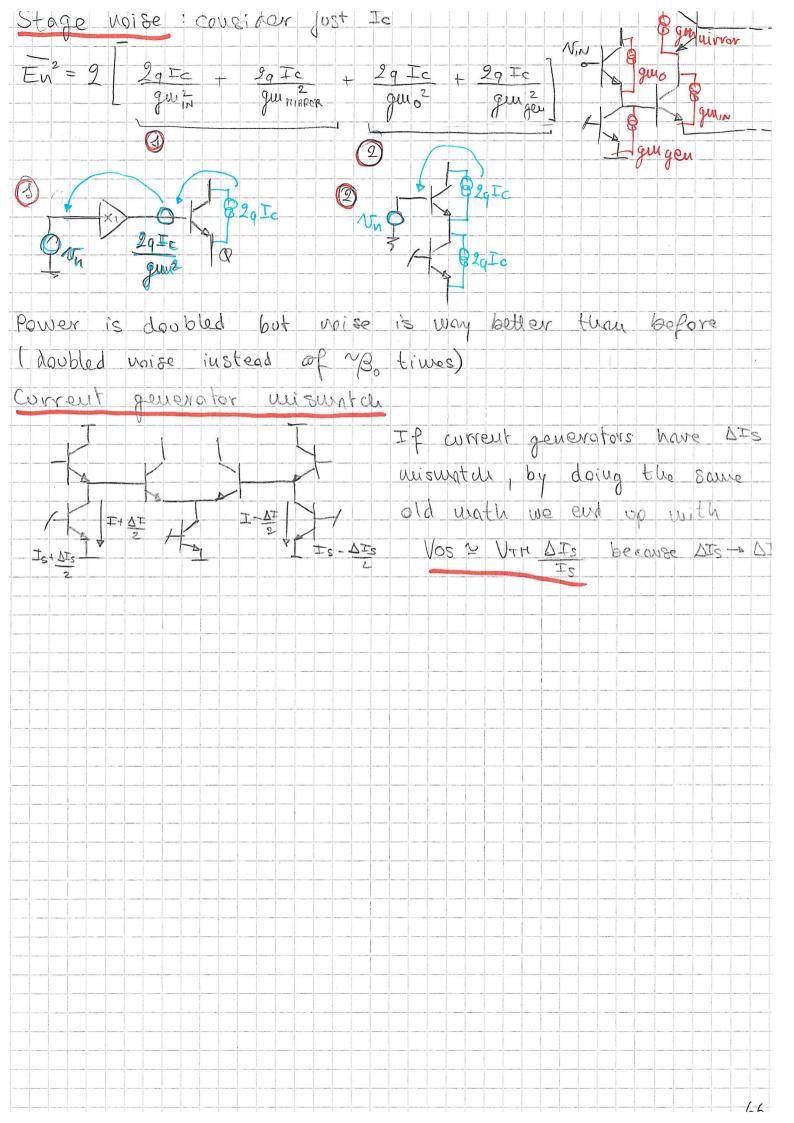

- 4. Common emitter input referred noise

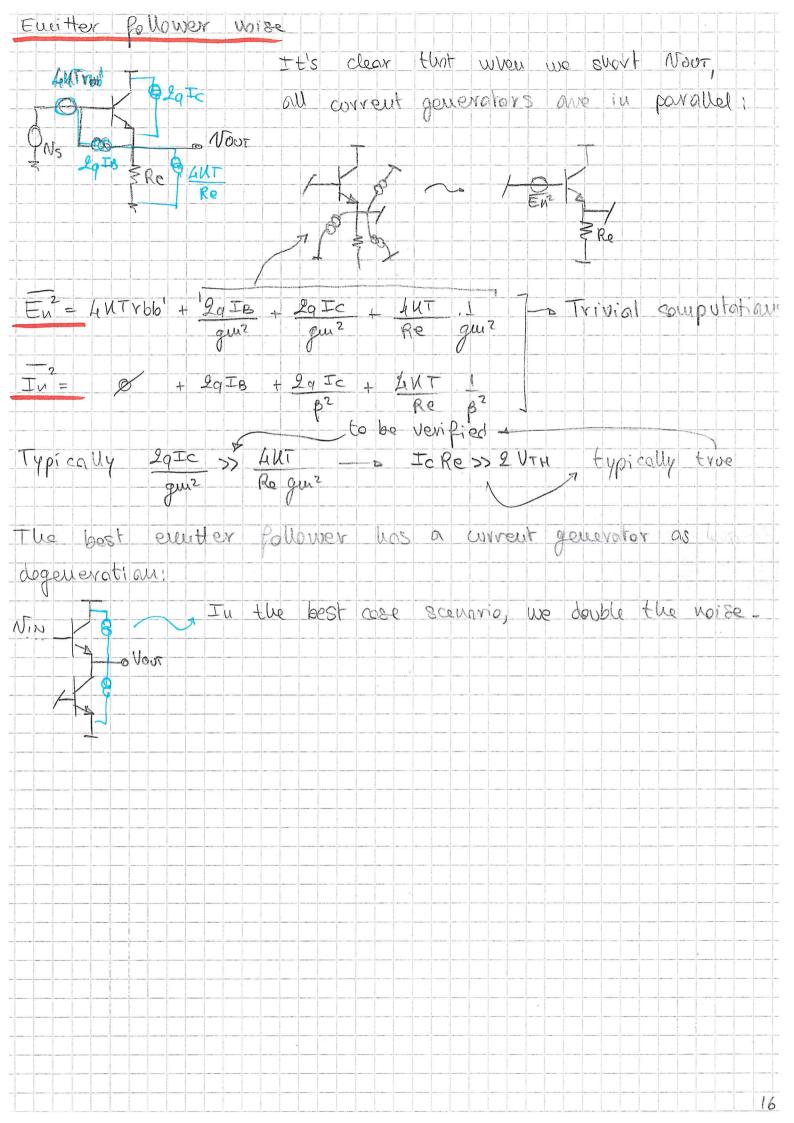

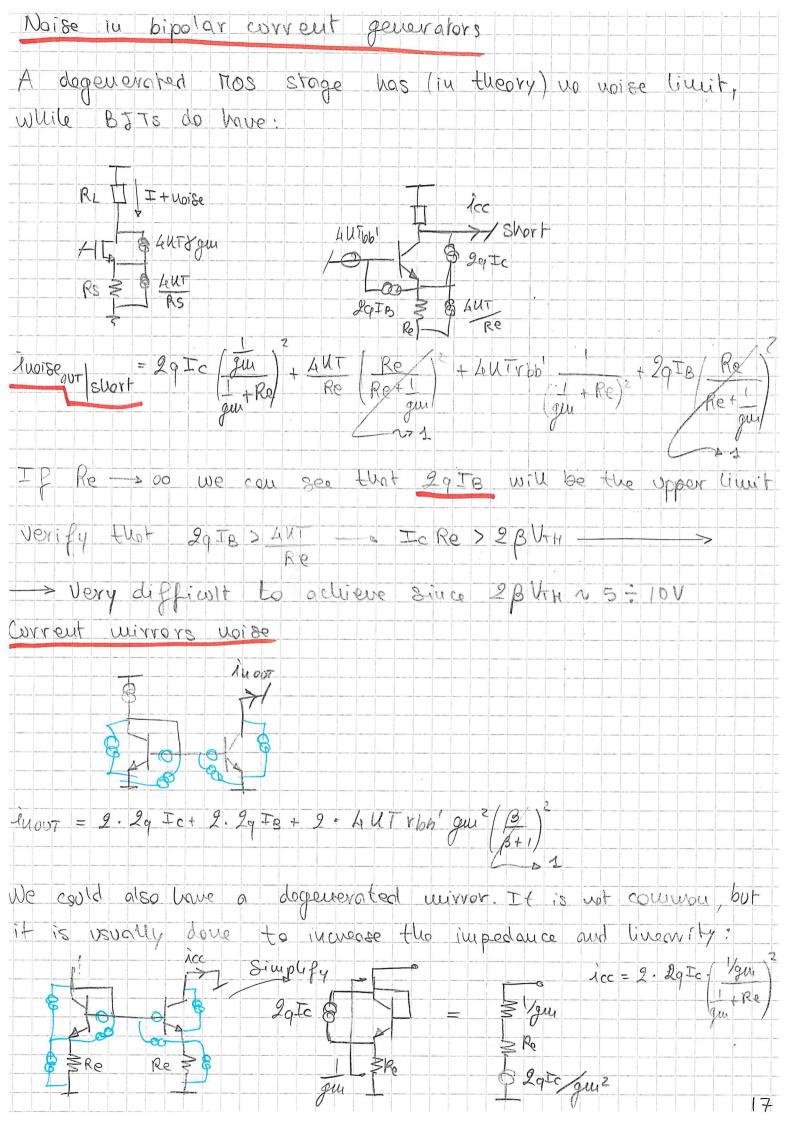

- 5. Noise of an active load, emitter follower, current generator, current mirror

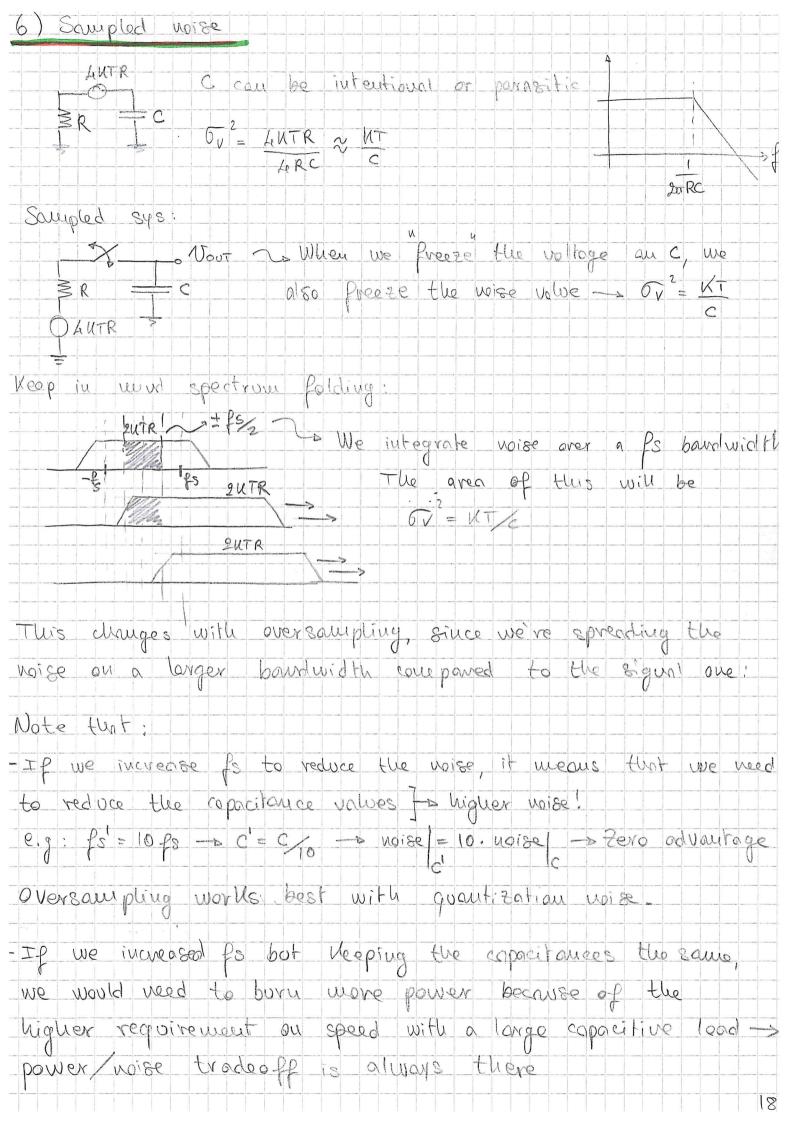

- 6. Sampled noise

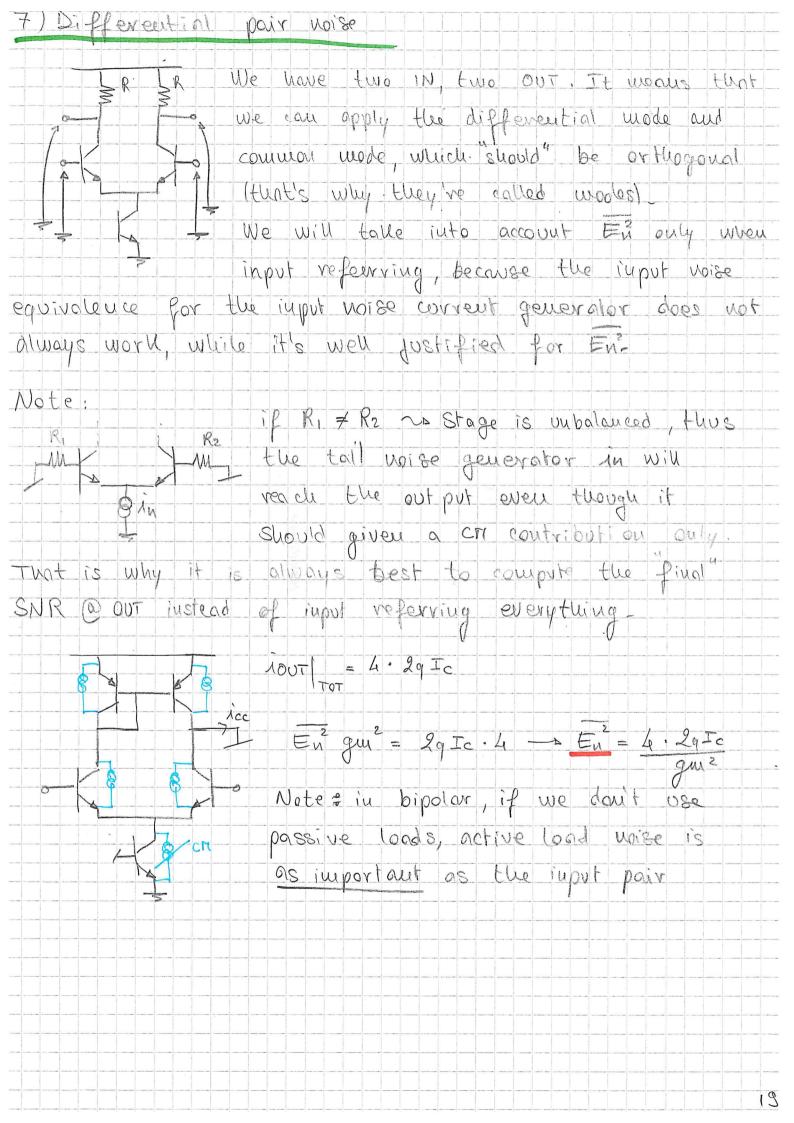

- 7. Differential pair noise

- 8. Offset: introduction and matching issues

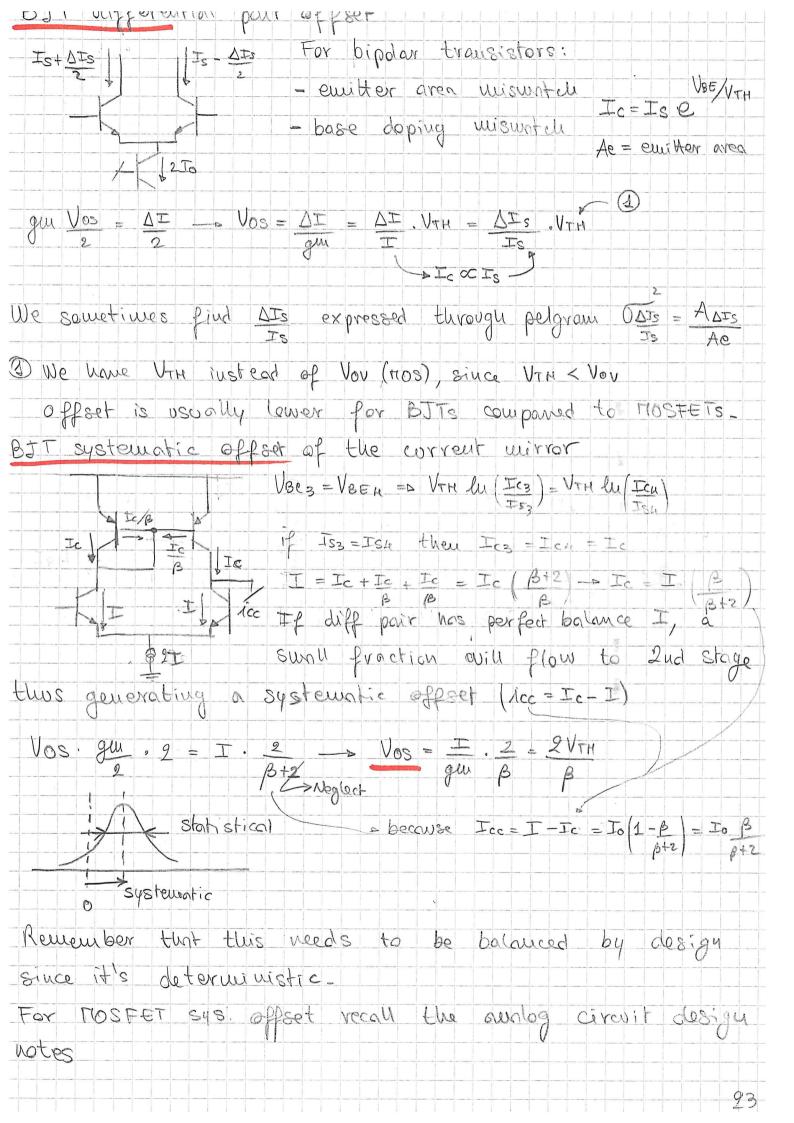

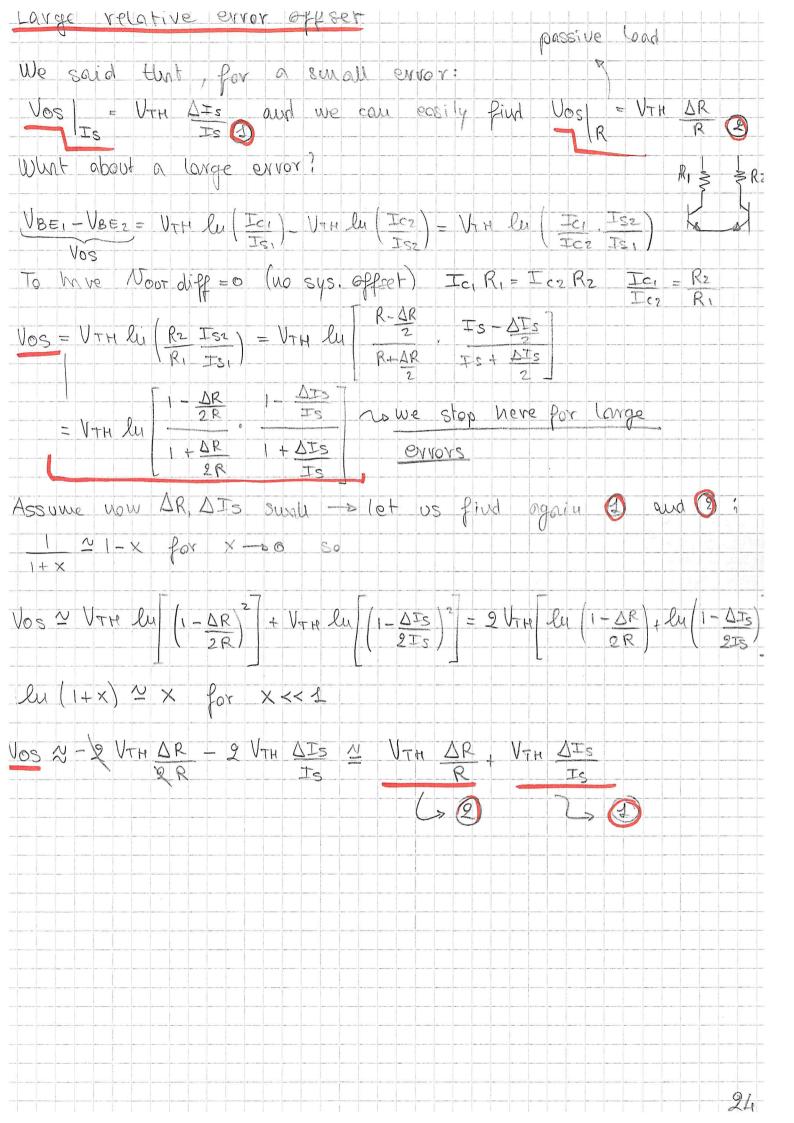

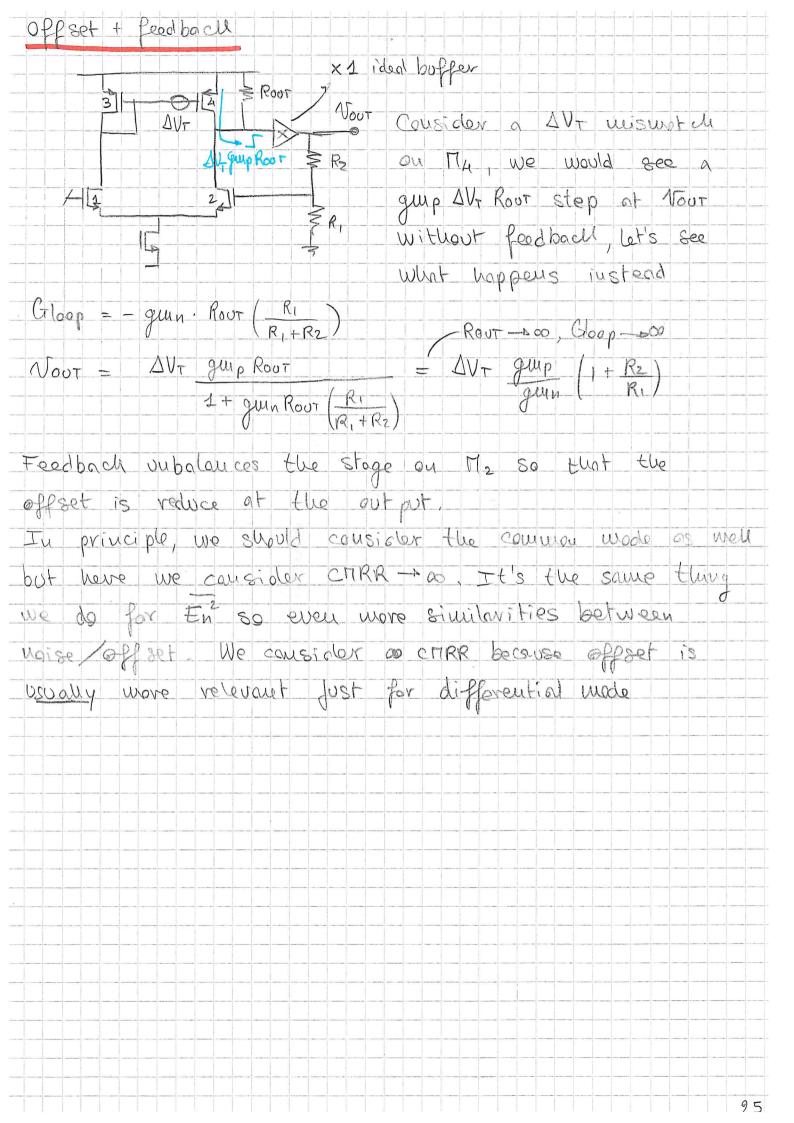

- 9. Offset in a differential pair, feedback effect on a current mismatch

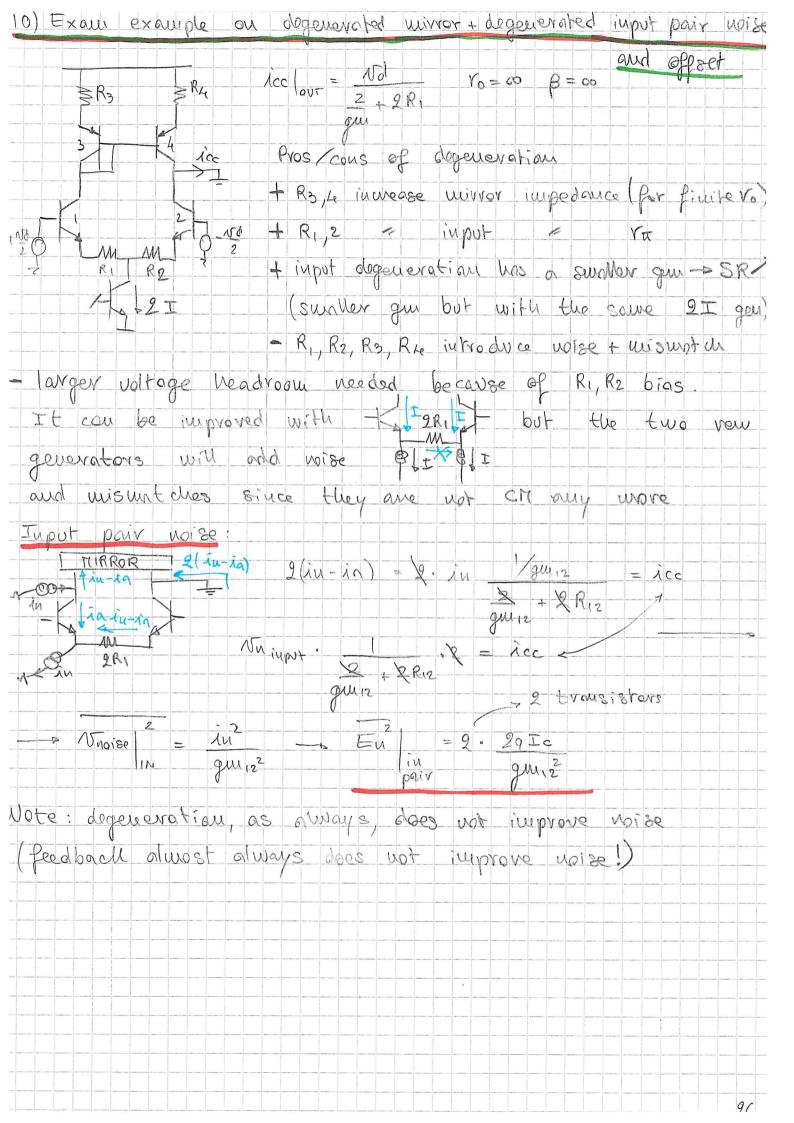

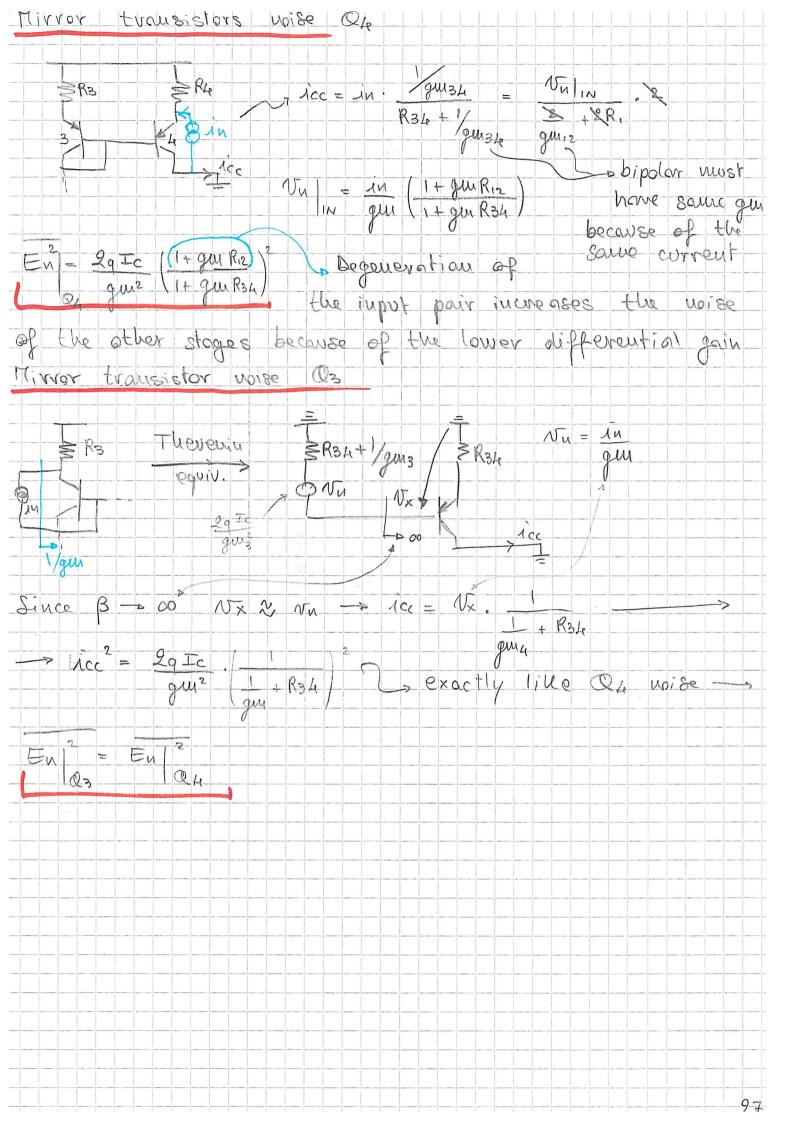

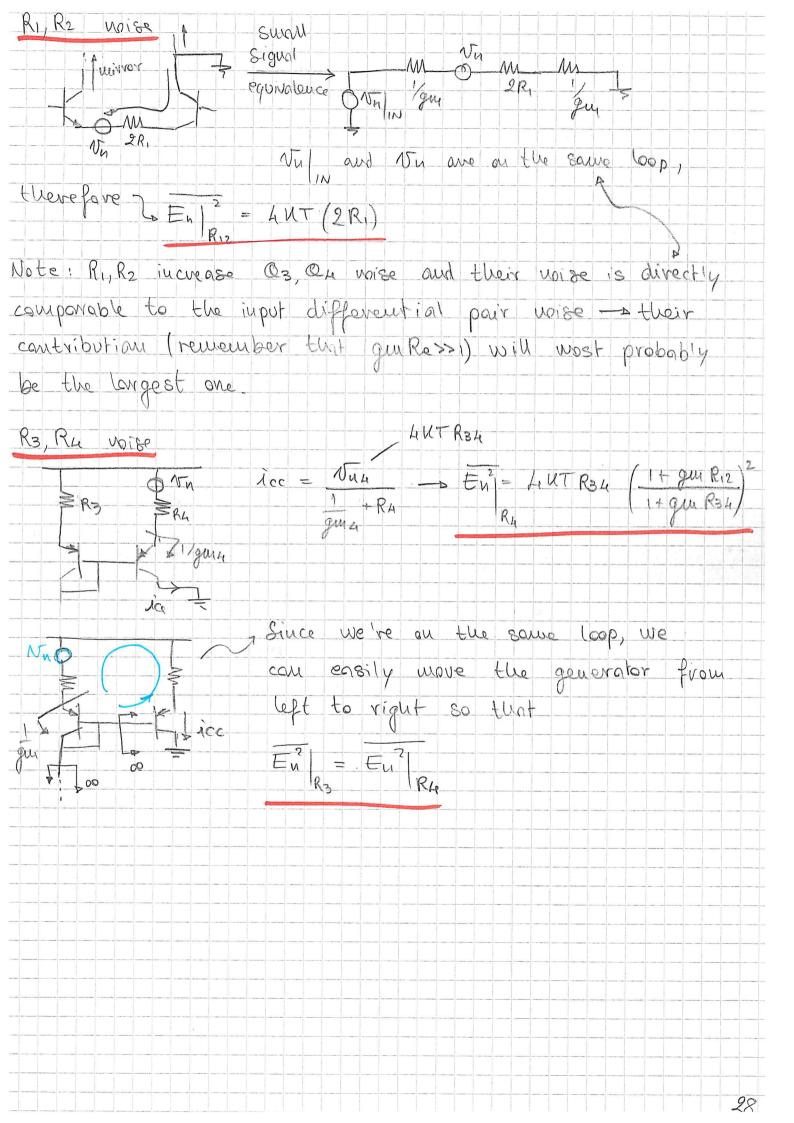

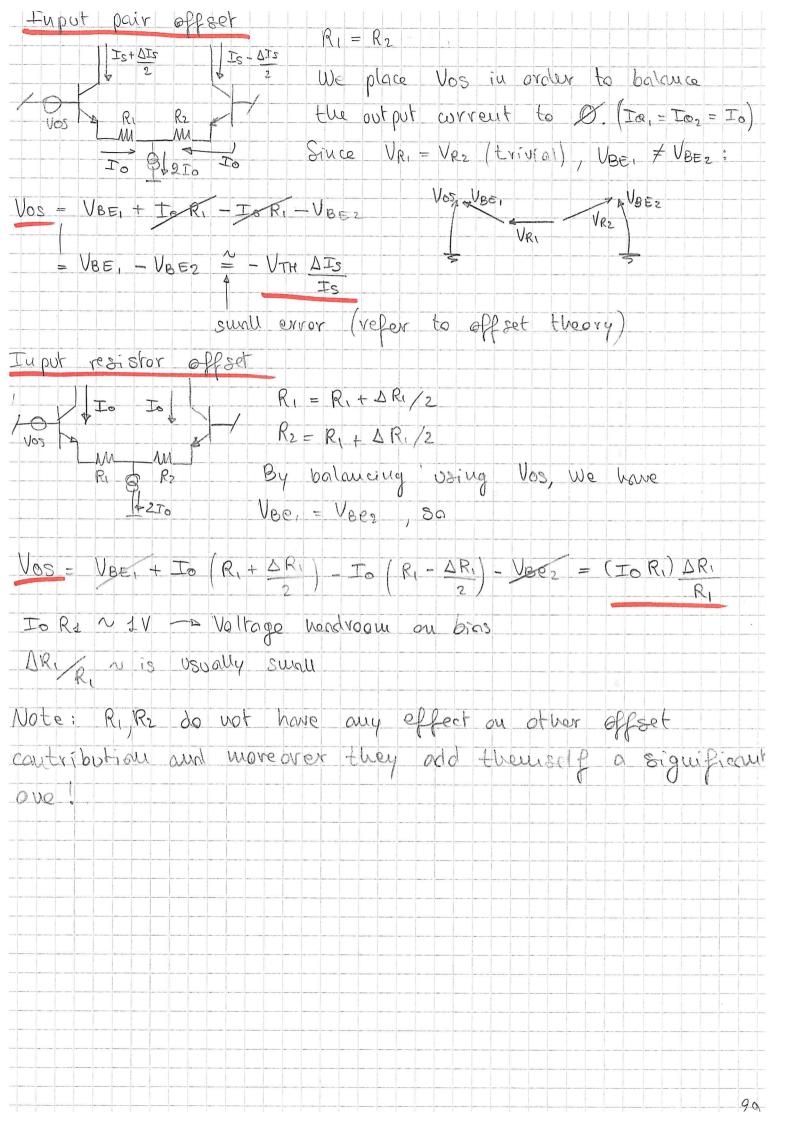

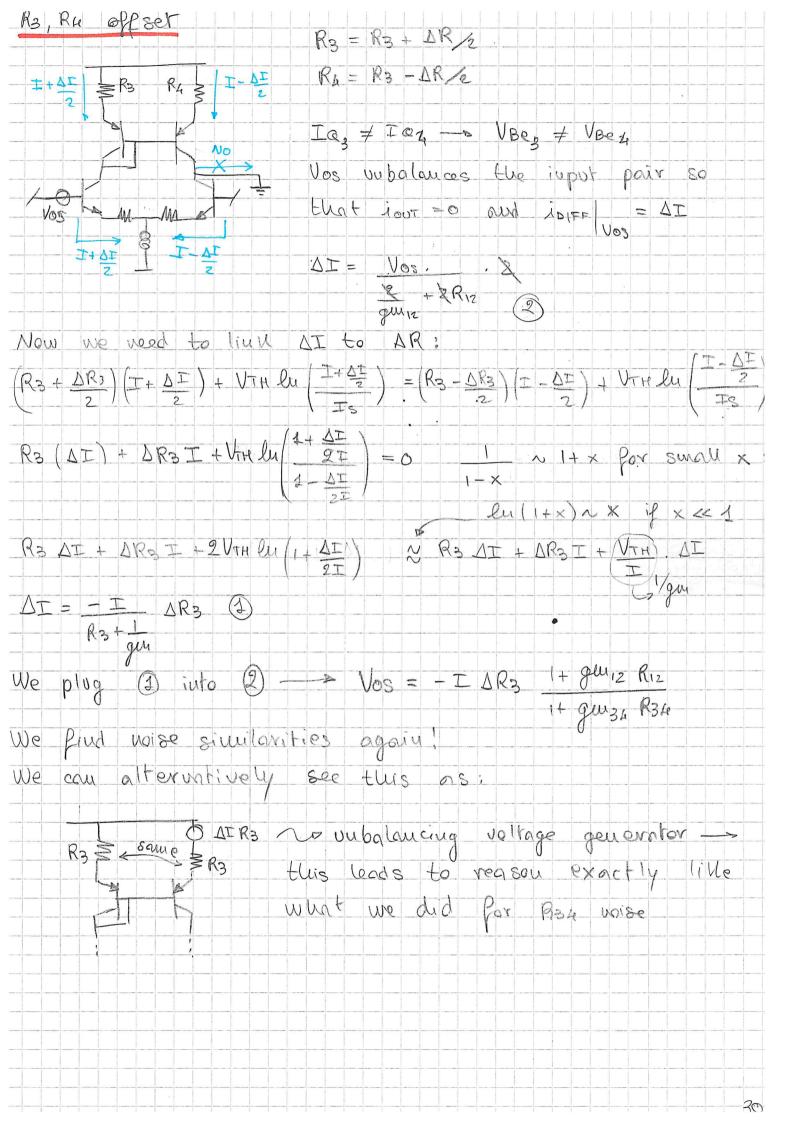

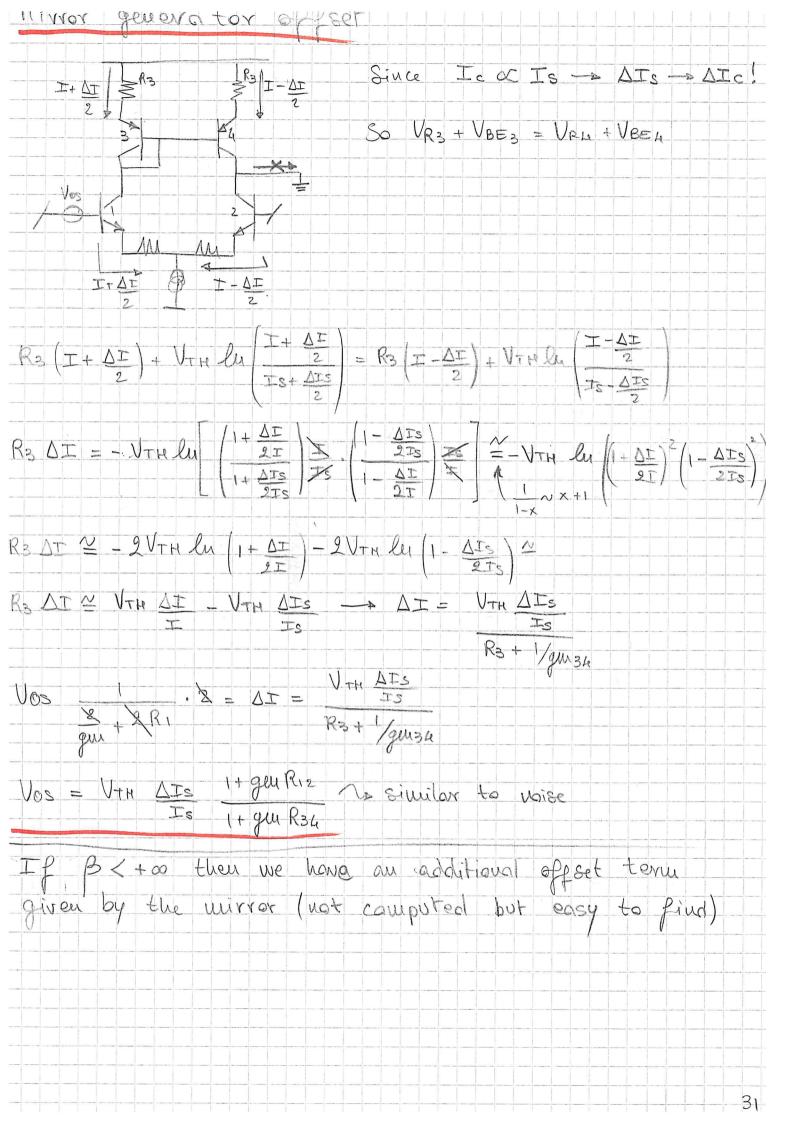

- 10. Exam example: degenerated mirror, degenerated input pair noise and offset analysis

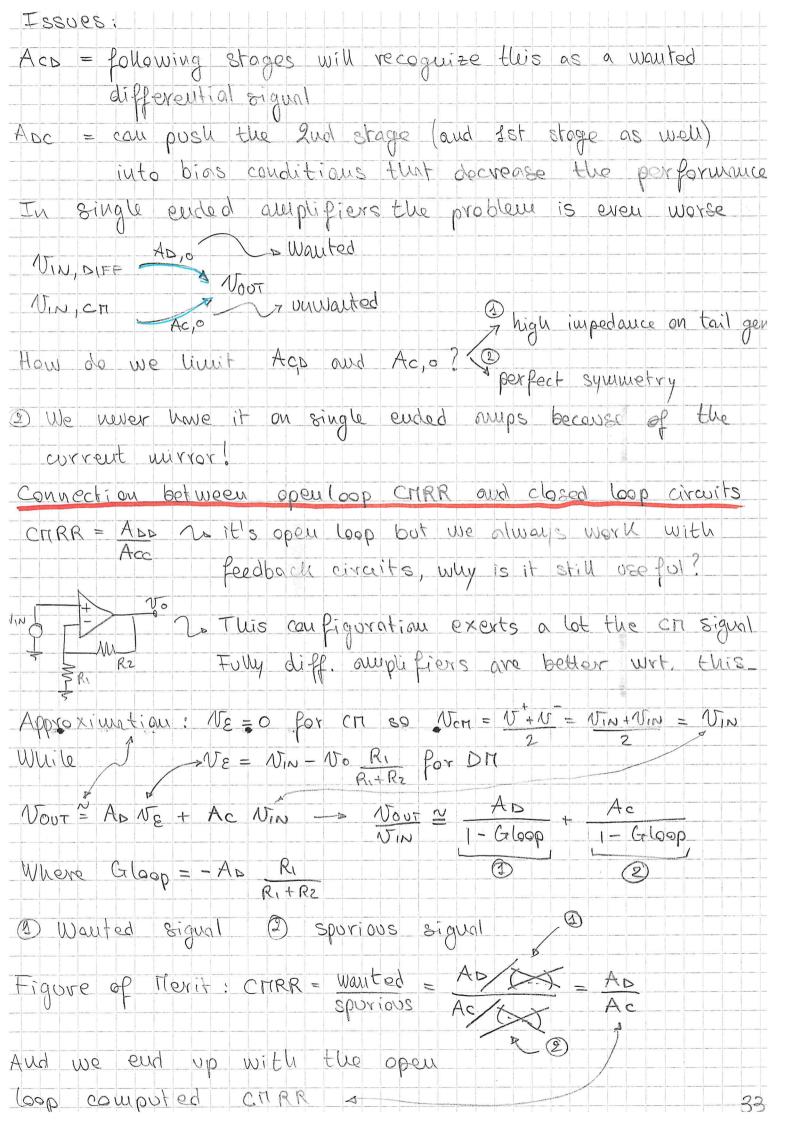

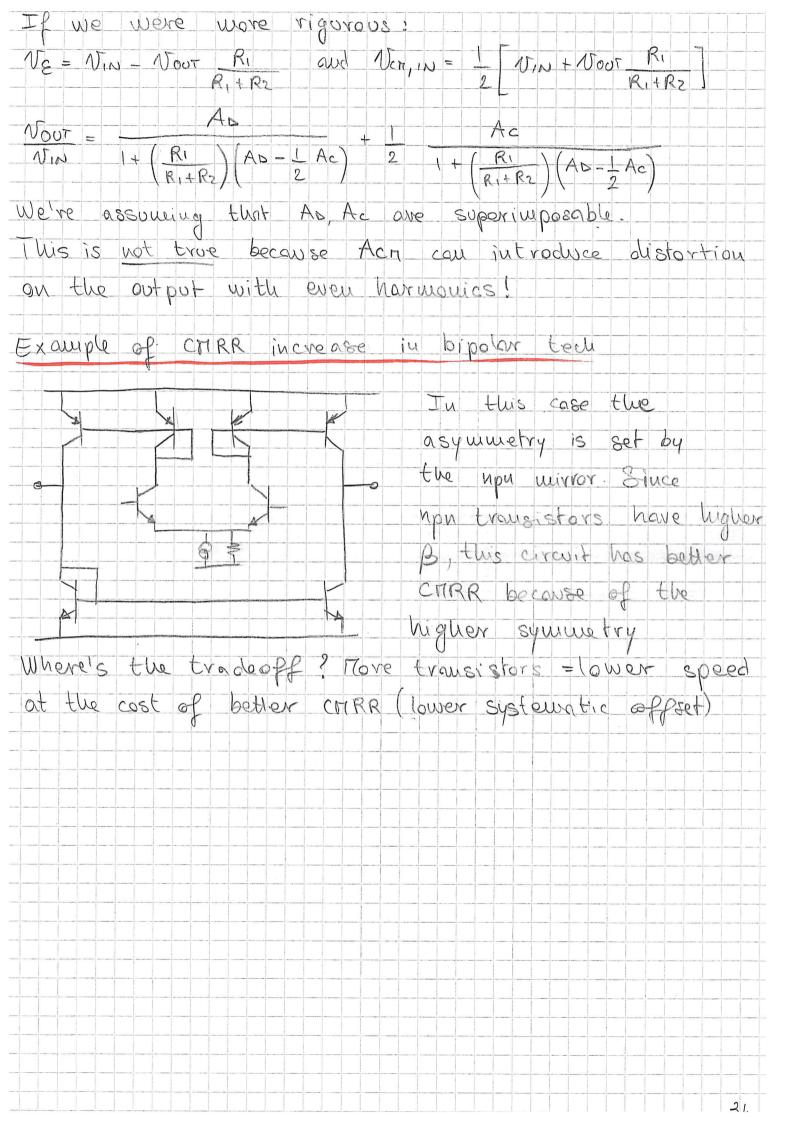

- 11. CMRR In fully differential amplifiers

- 12. CMRR rule of thumb for computation

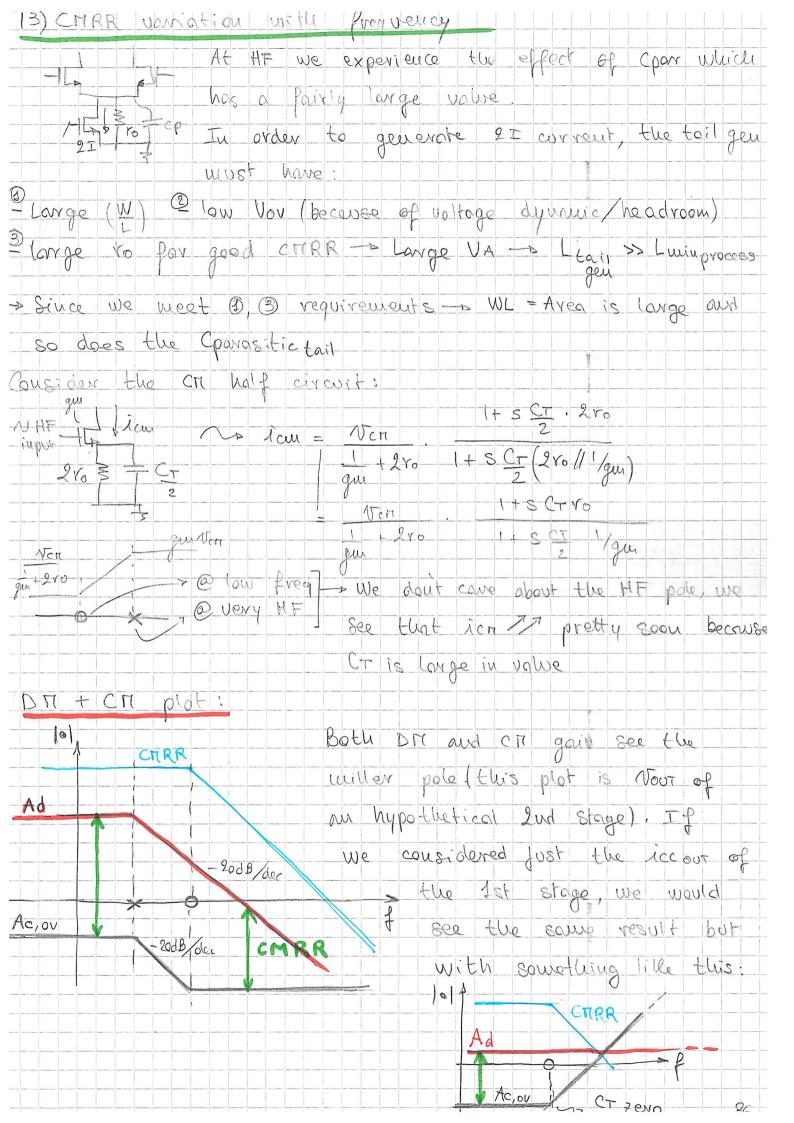

- 13. CMRR variation in frequency

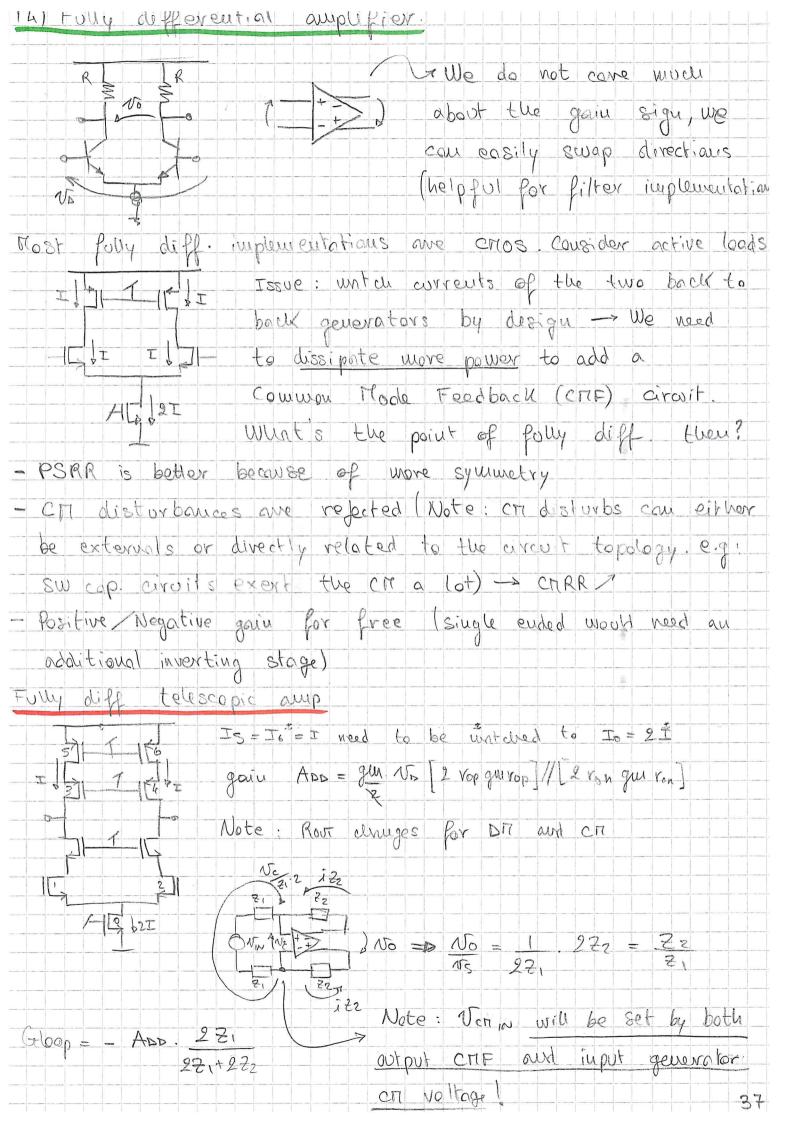

- 14. Fully differential amplifiers

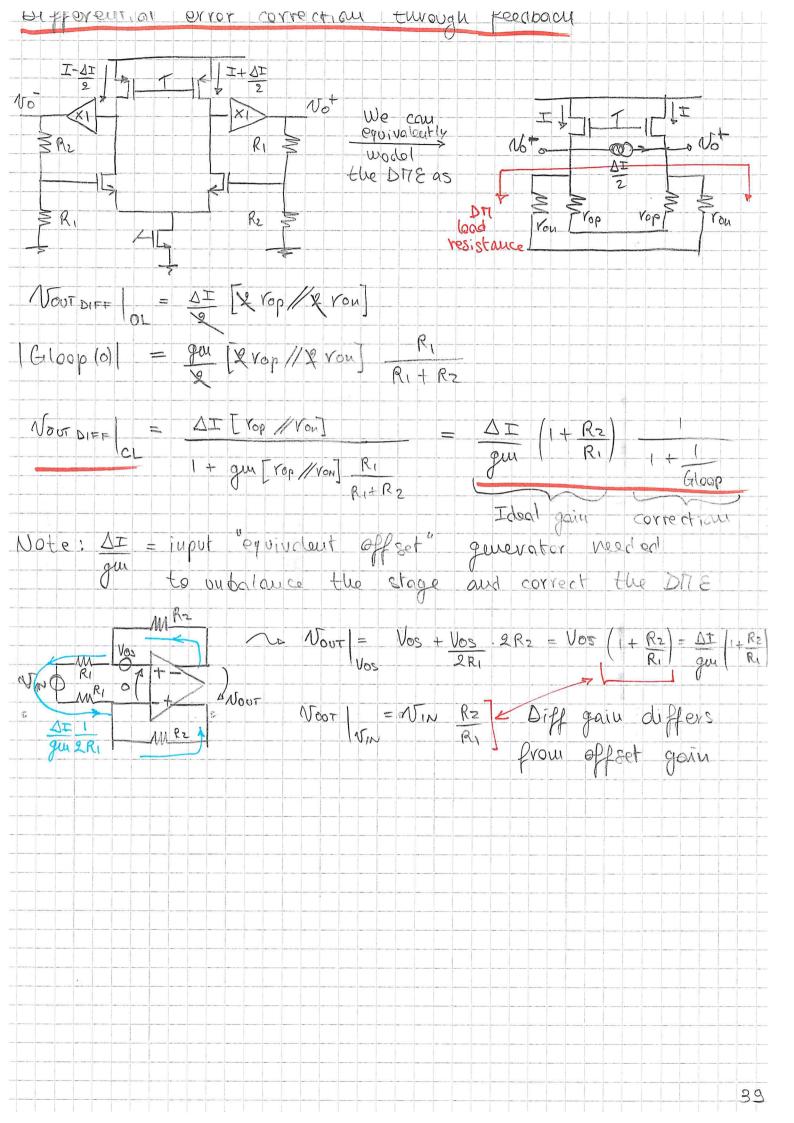

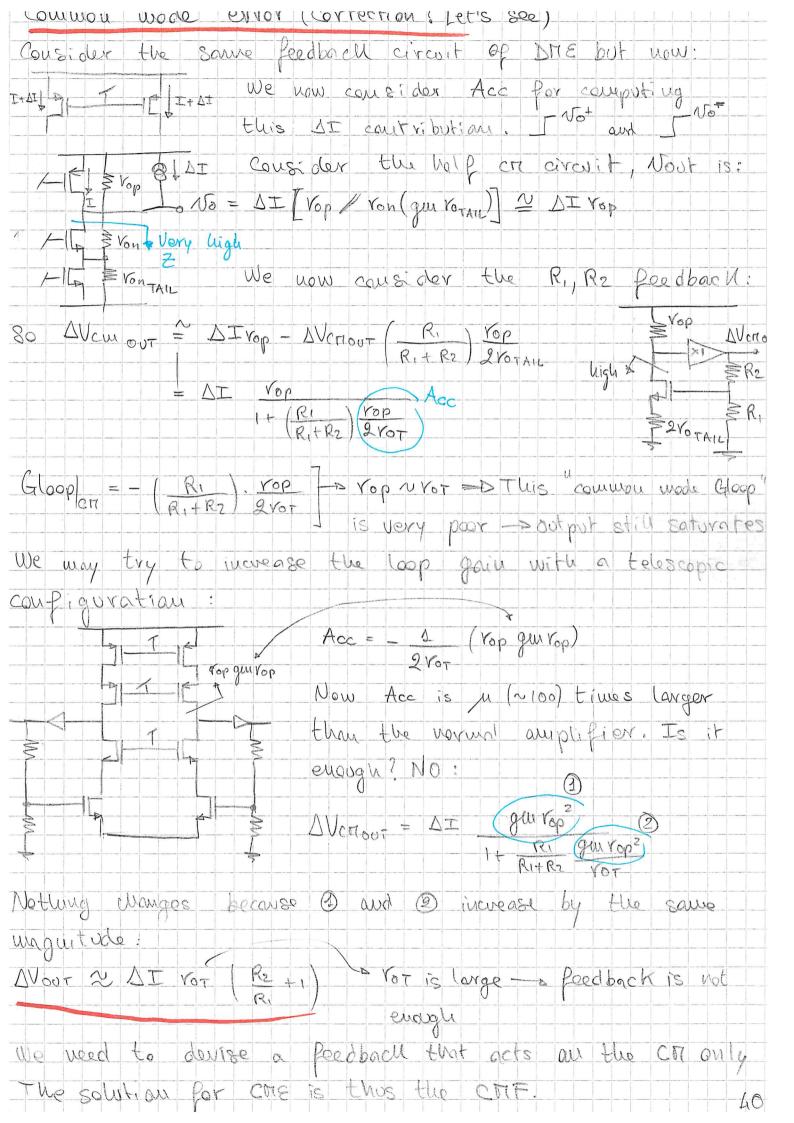

- 15. Differential an Common mode errors in current bias of fully differential amplifier

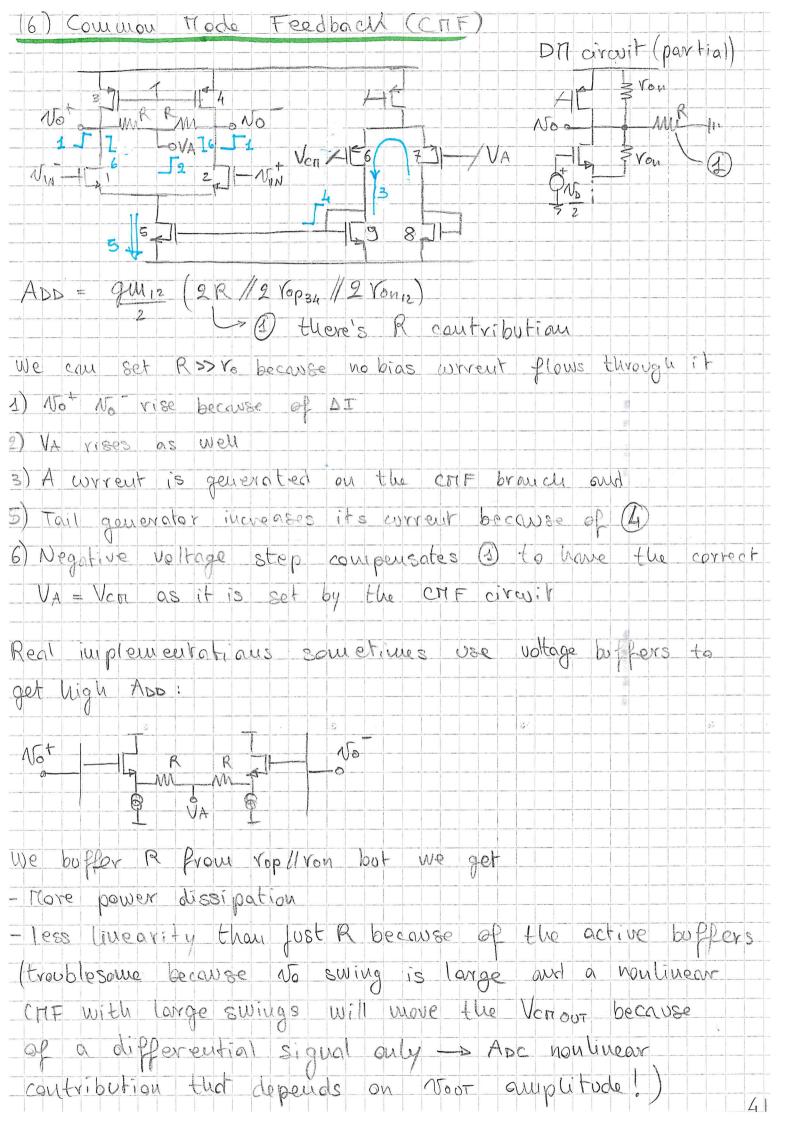

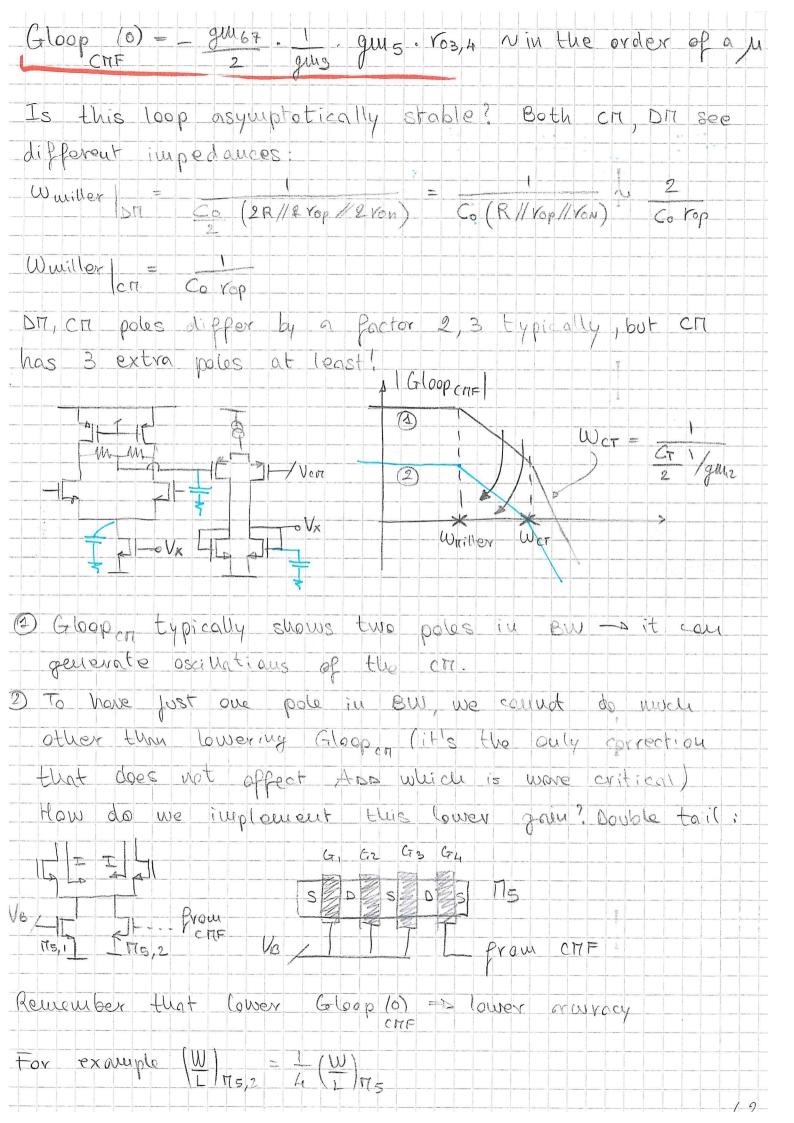

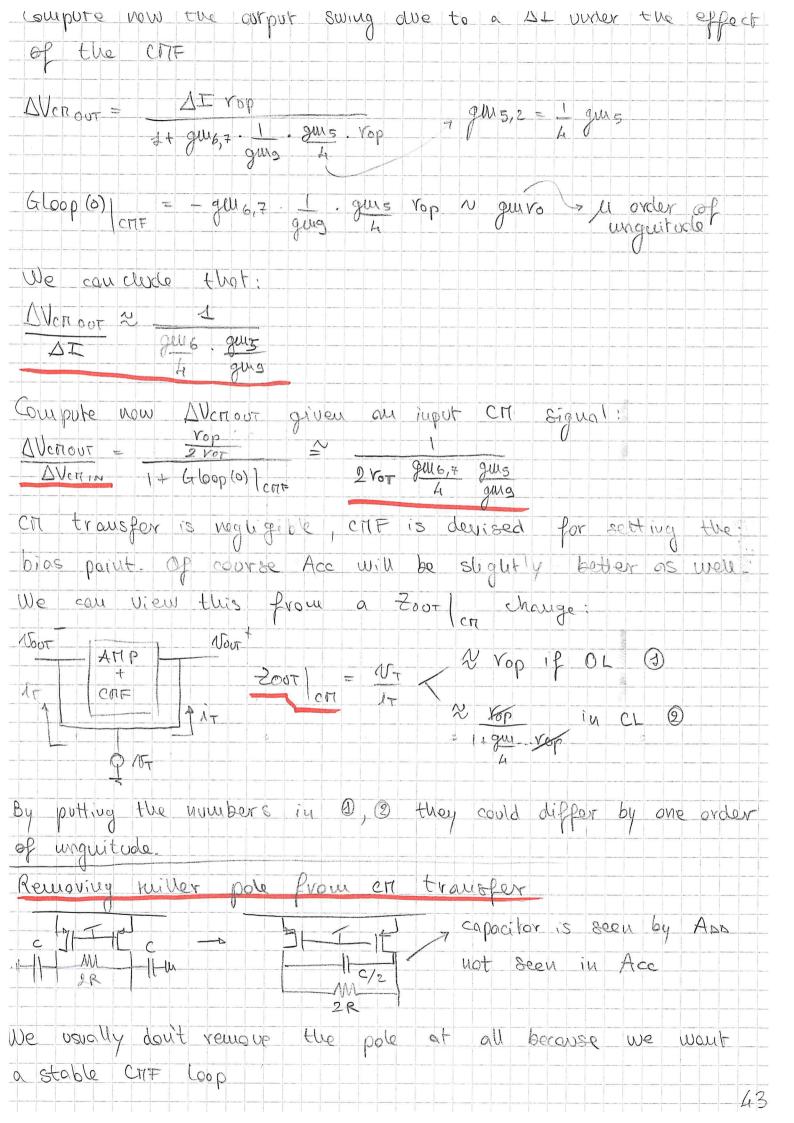

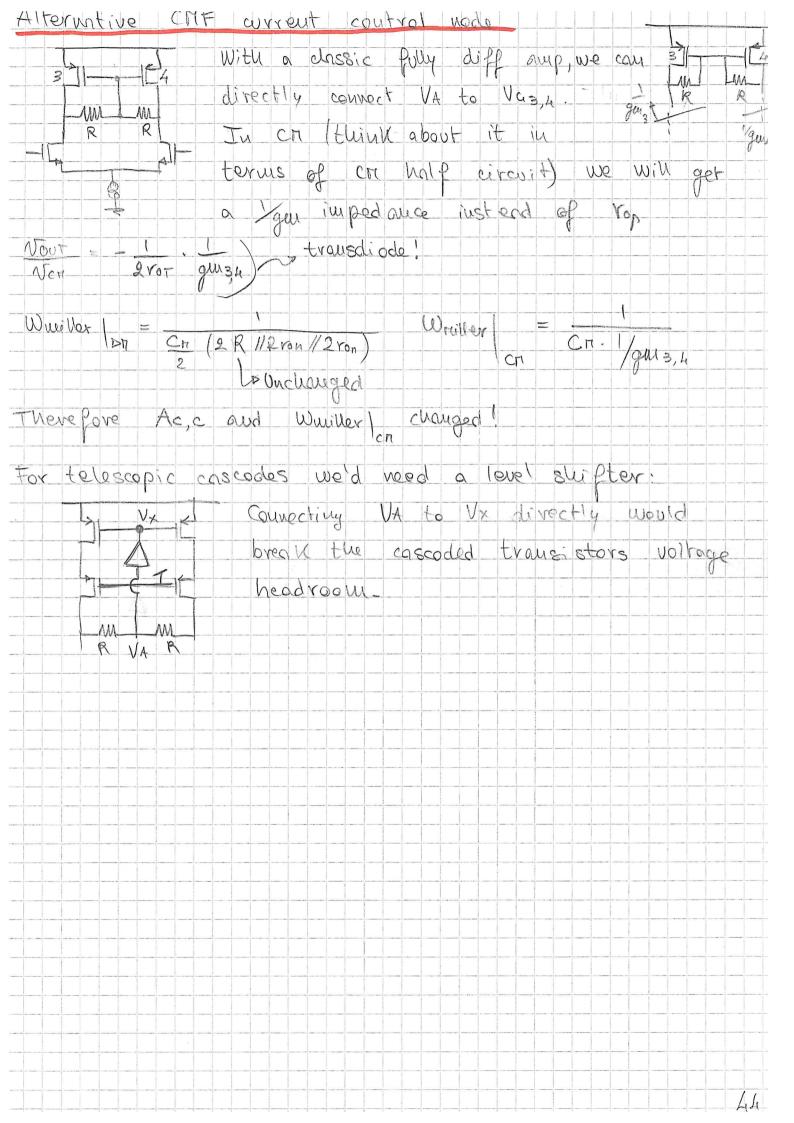

- 16. Common Mode Feedback (CMF): DC analysis, poles and common mode resistance effect, simple CMF circuits examples

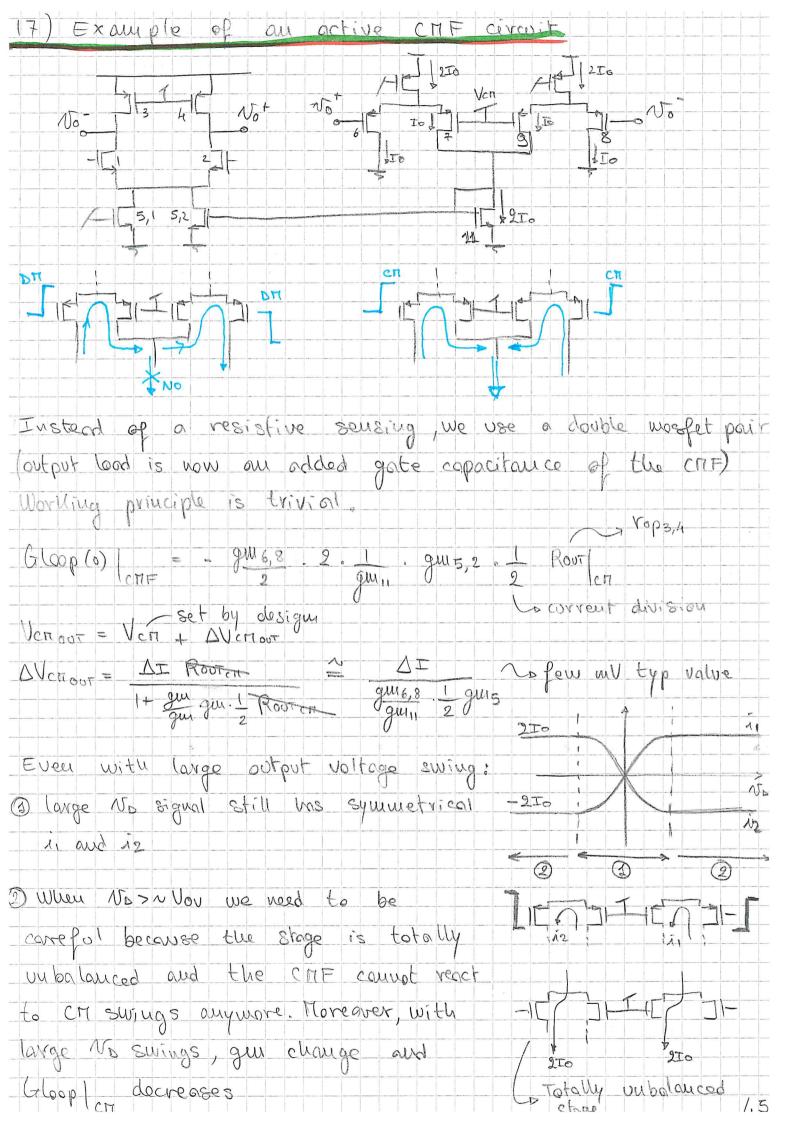

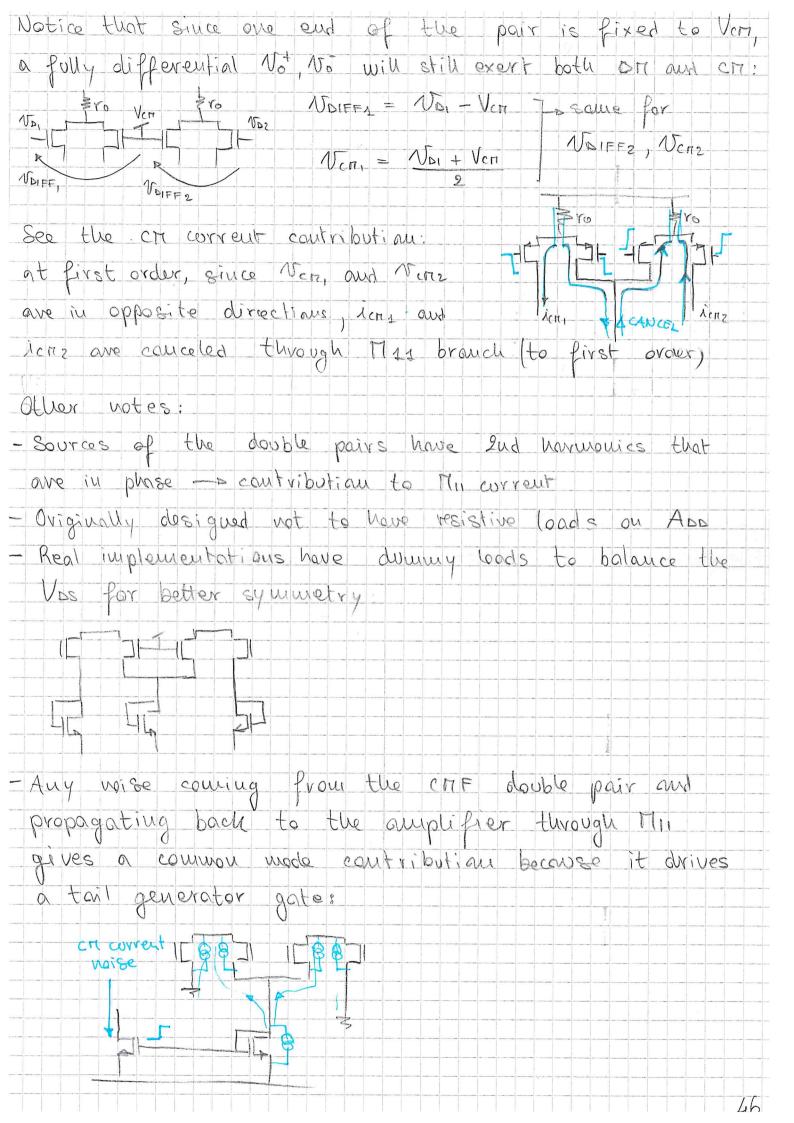

- 17. Example of an active CMF with a double differential pair

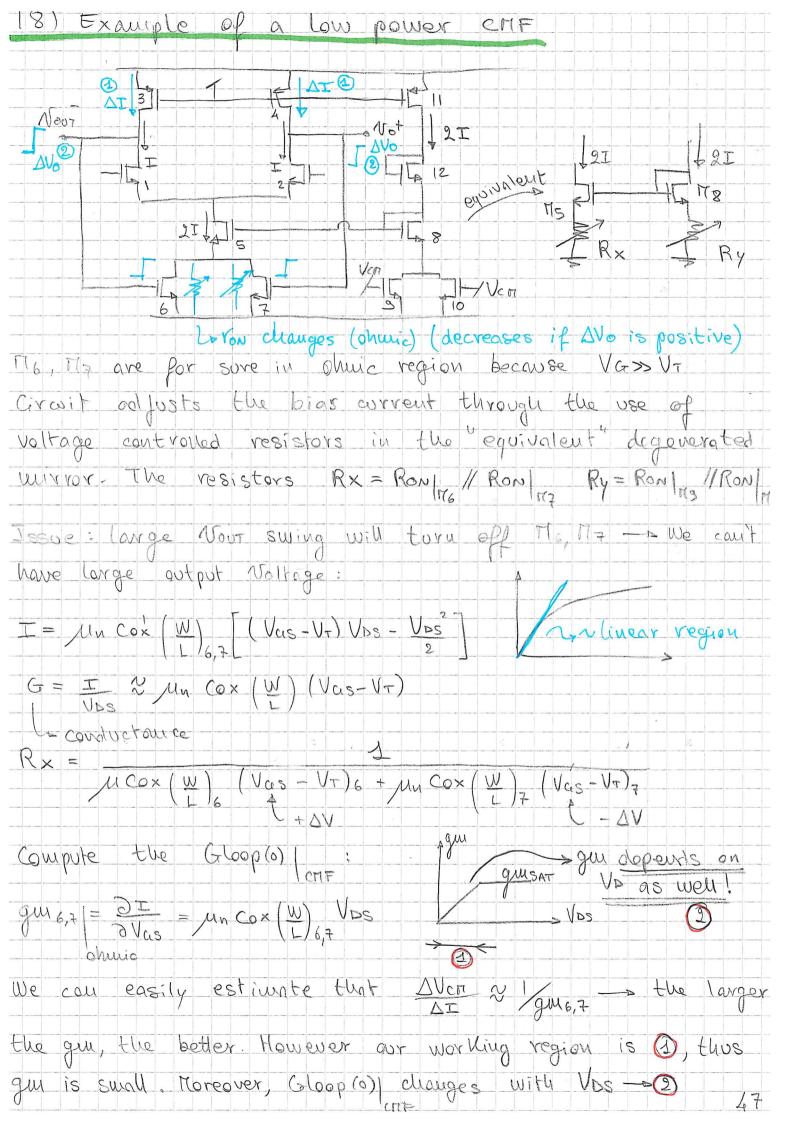

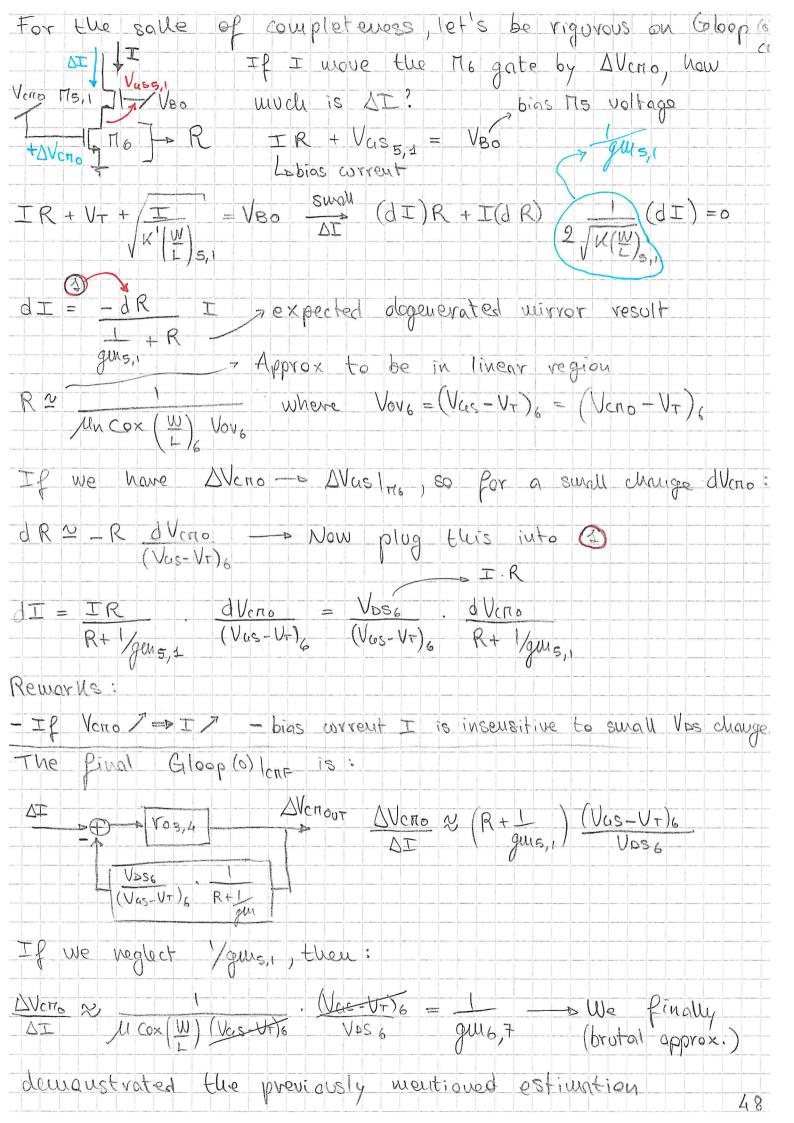

- 18. Example of a low power CMF

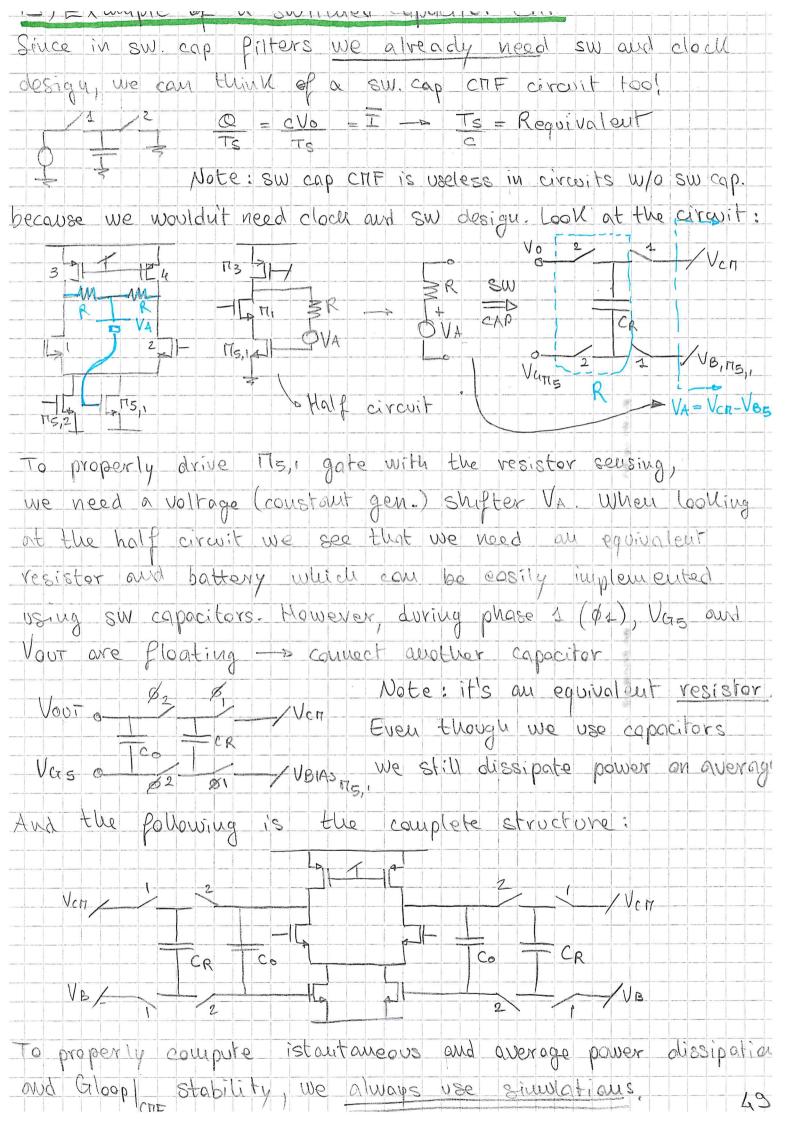

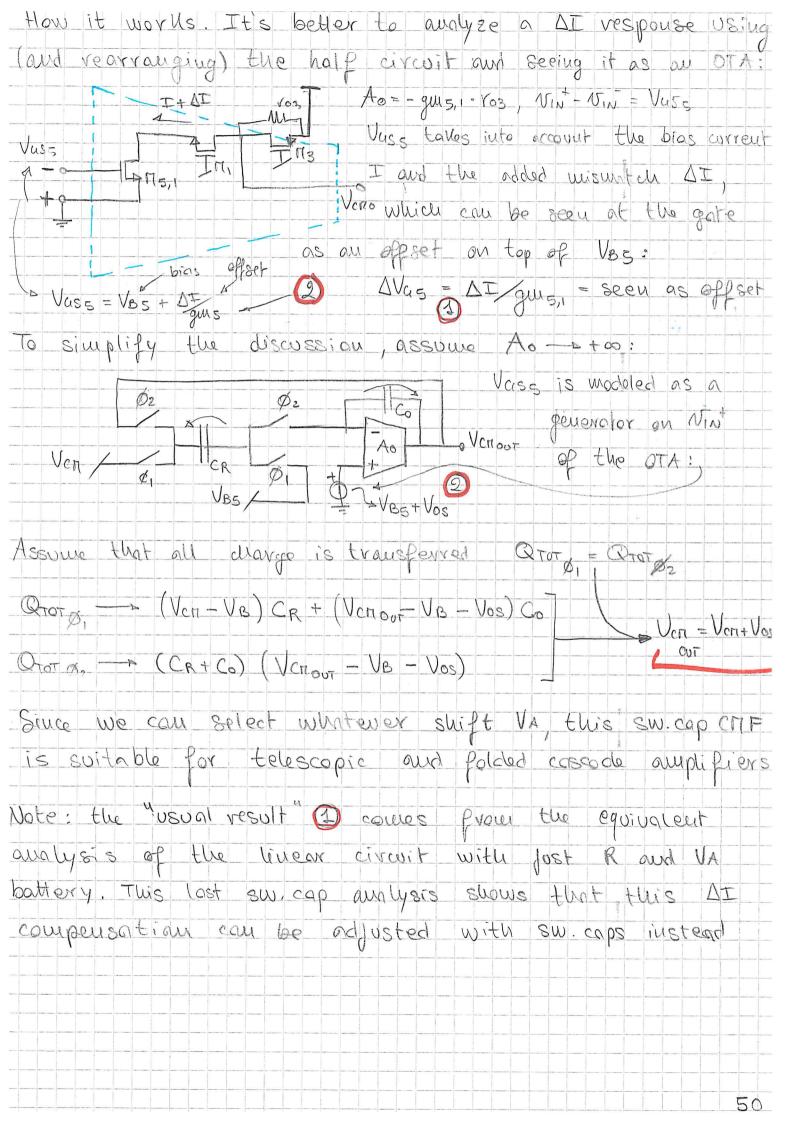

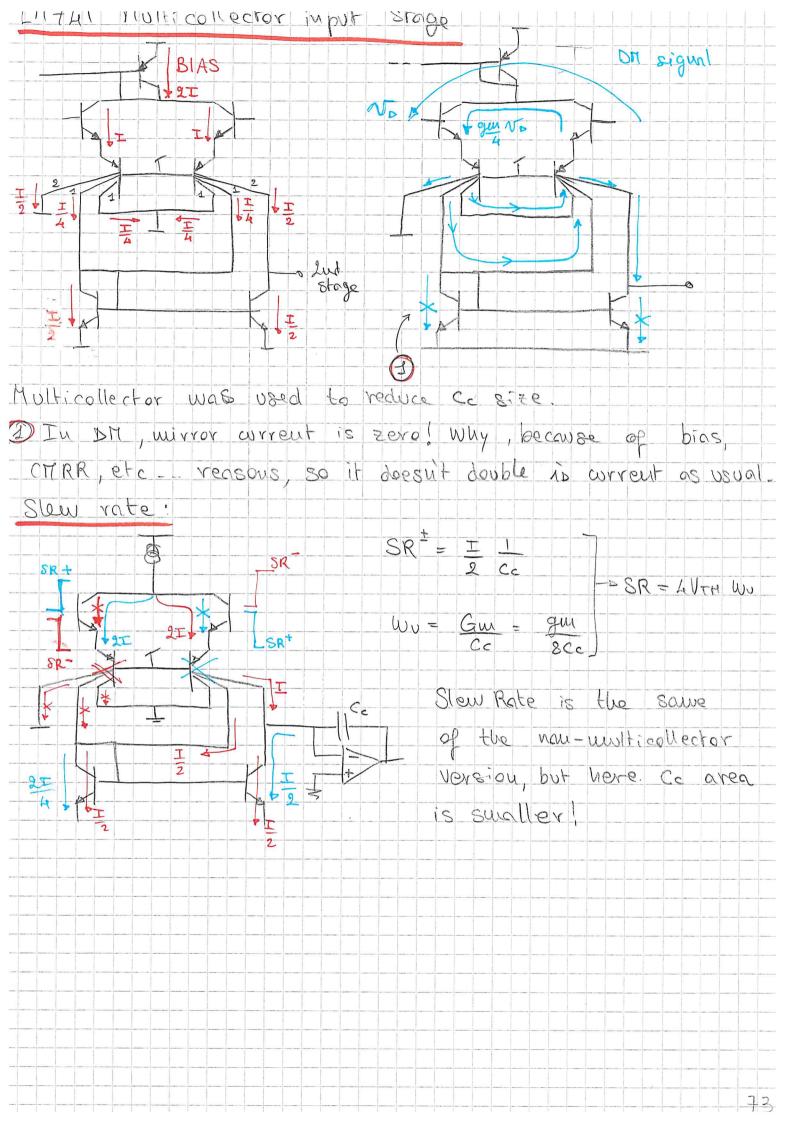

- 19. Example of a switched capacitor CMF

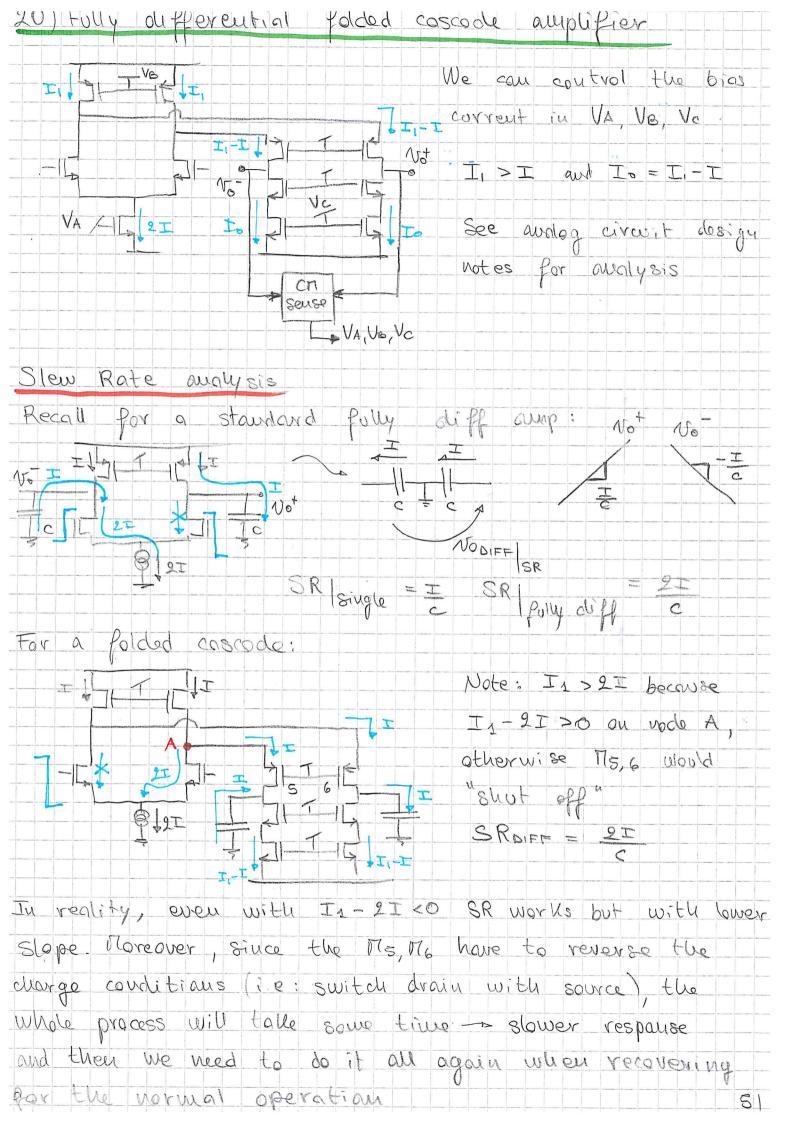

- 20. Fully differential folded cascode amplifier: slew rate analysis

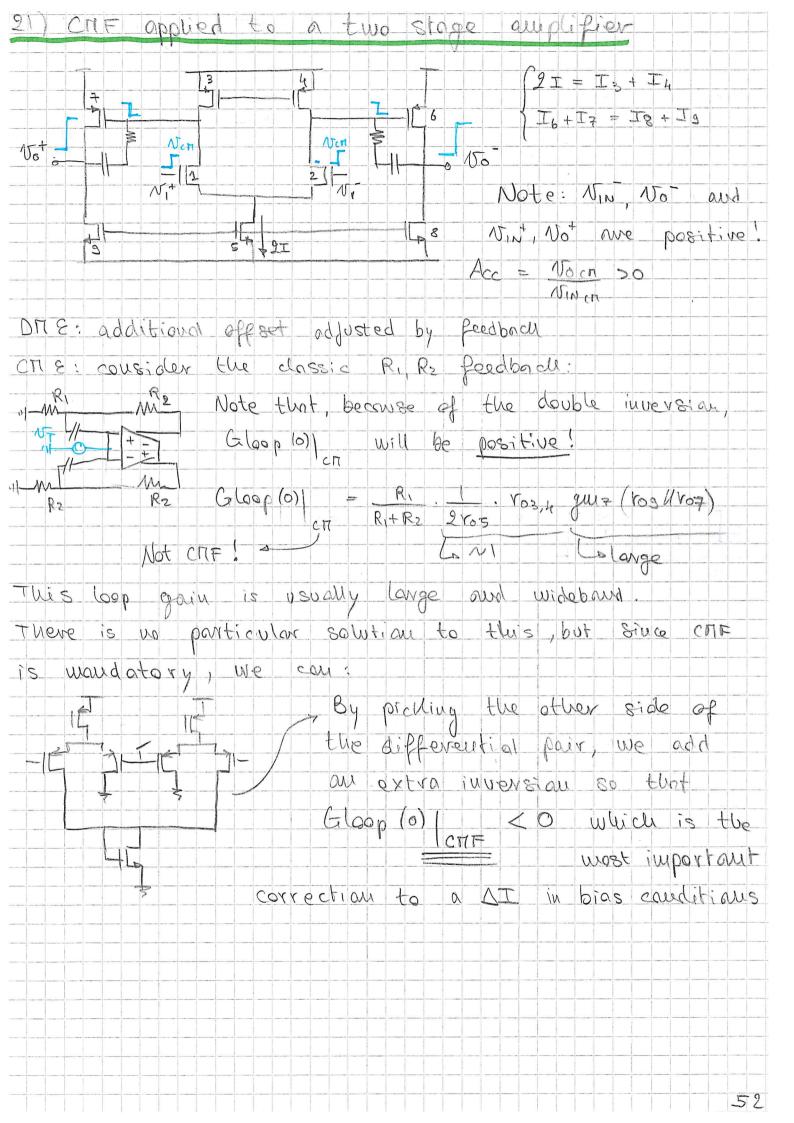

- 21. CMF applied to a two stage amplifier

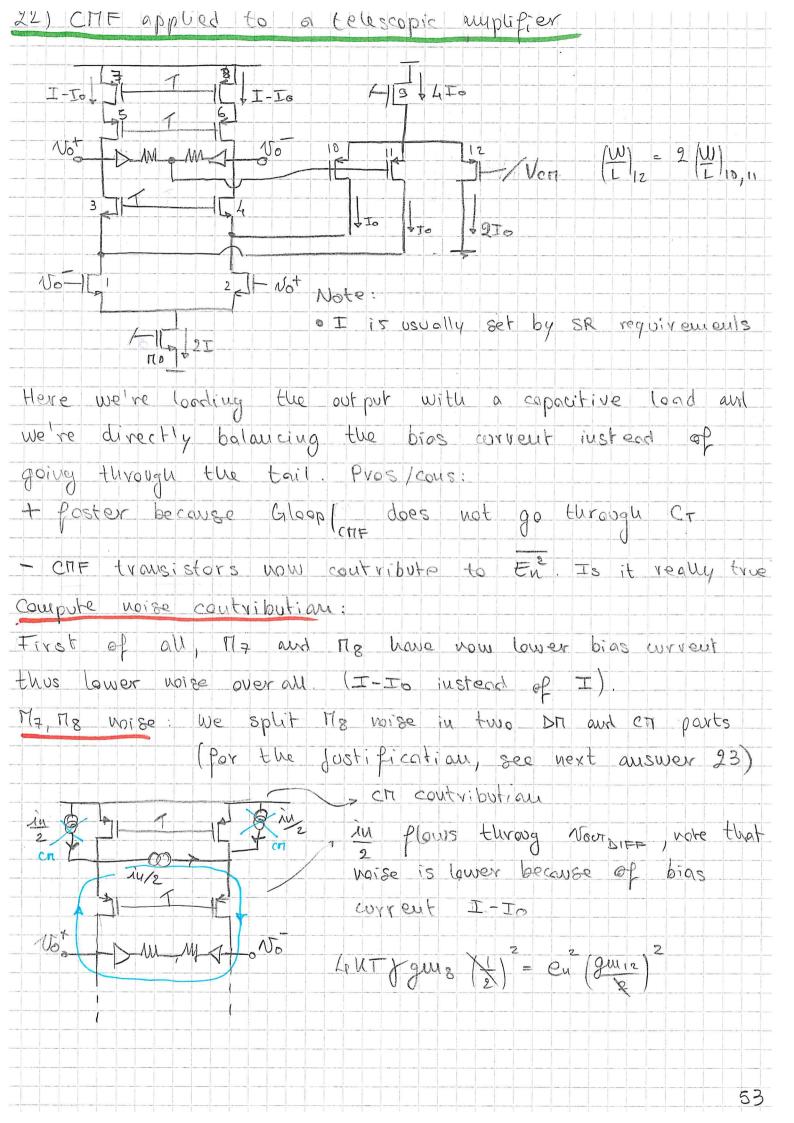

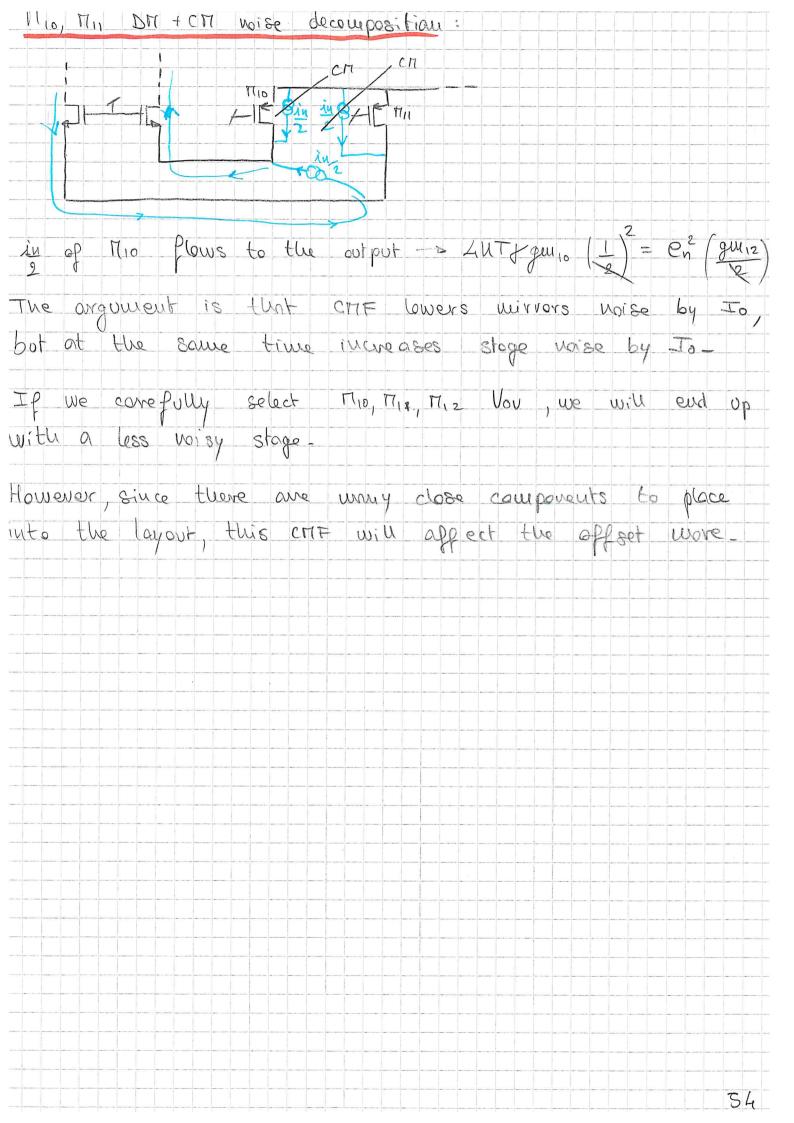

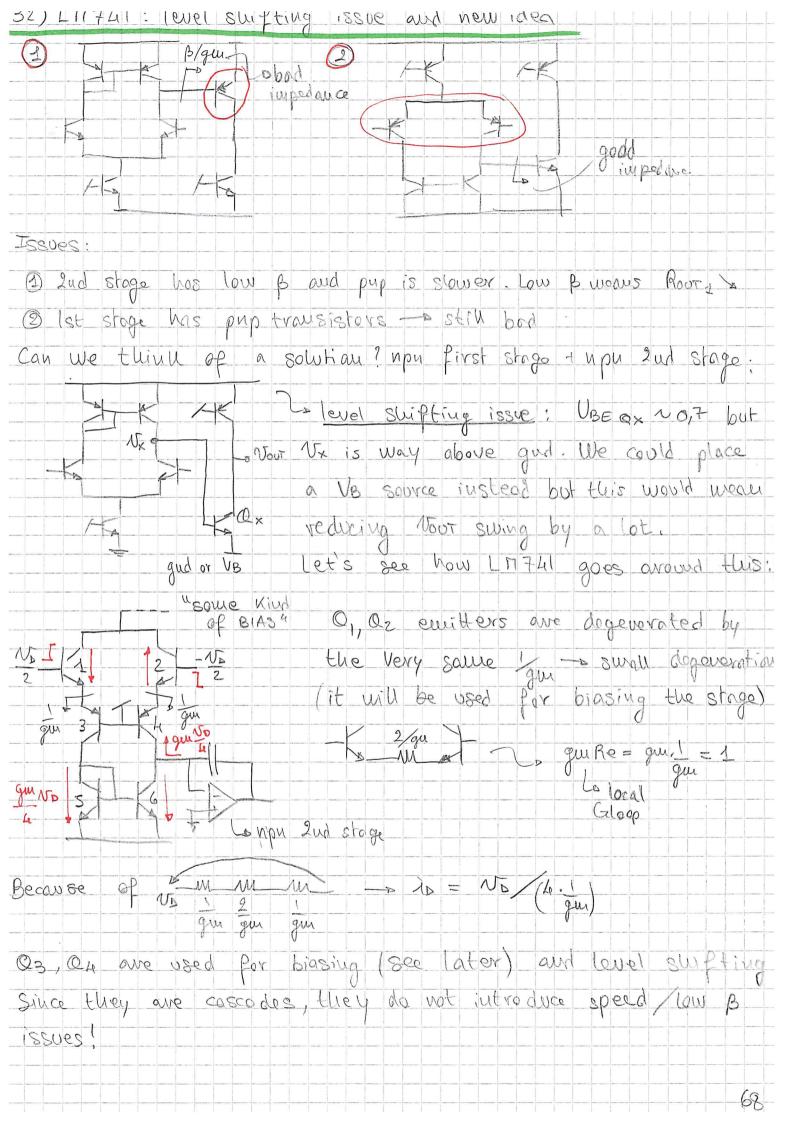

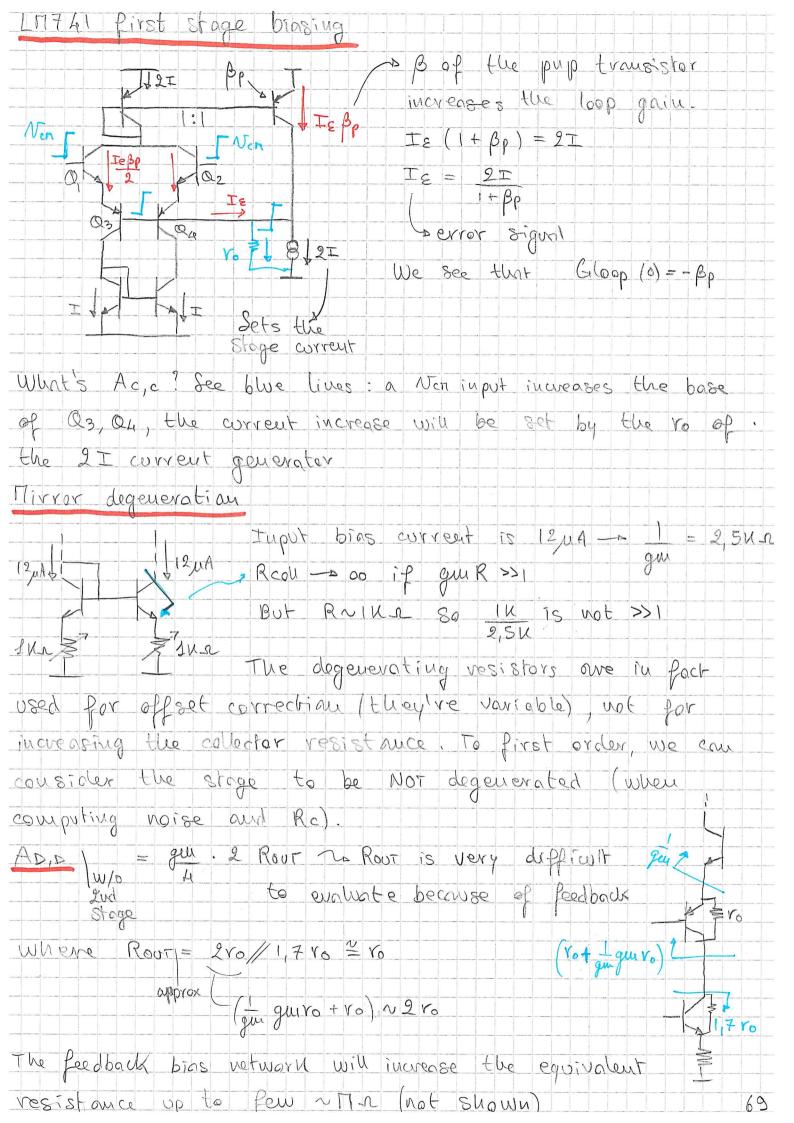

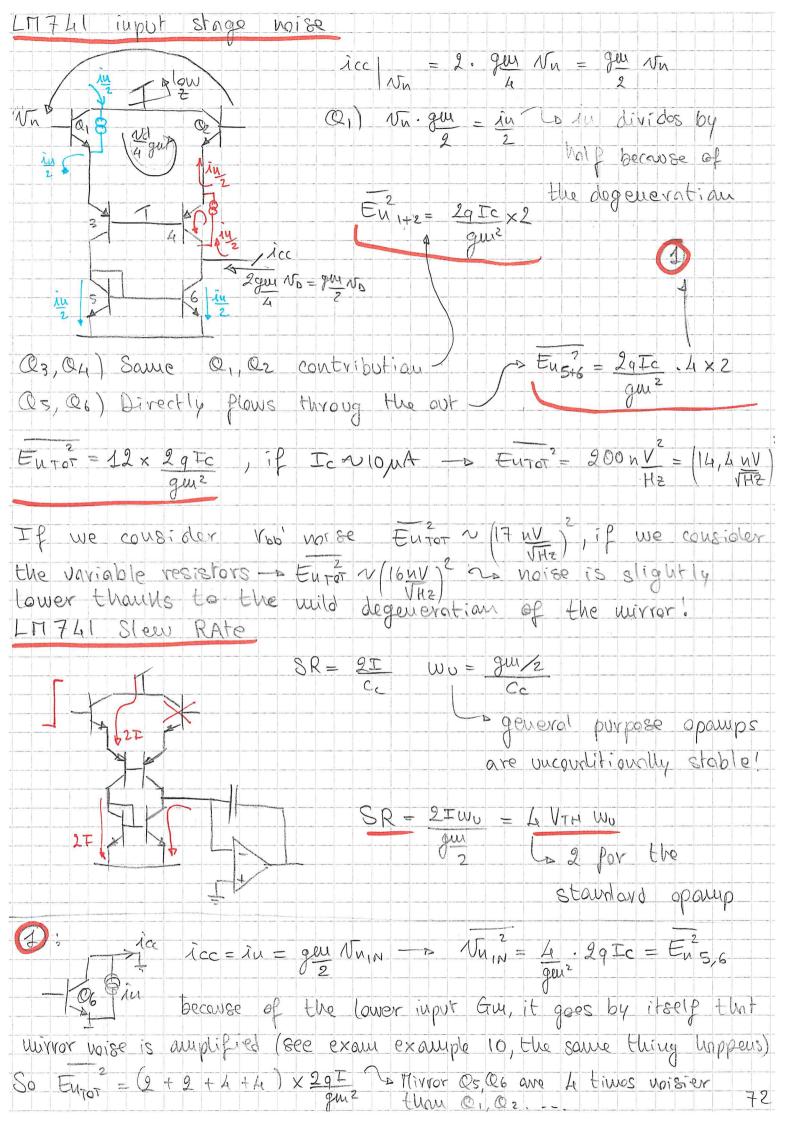

- 22. CMF applied to a telescopic amplifier

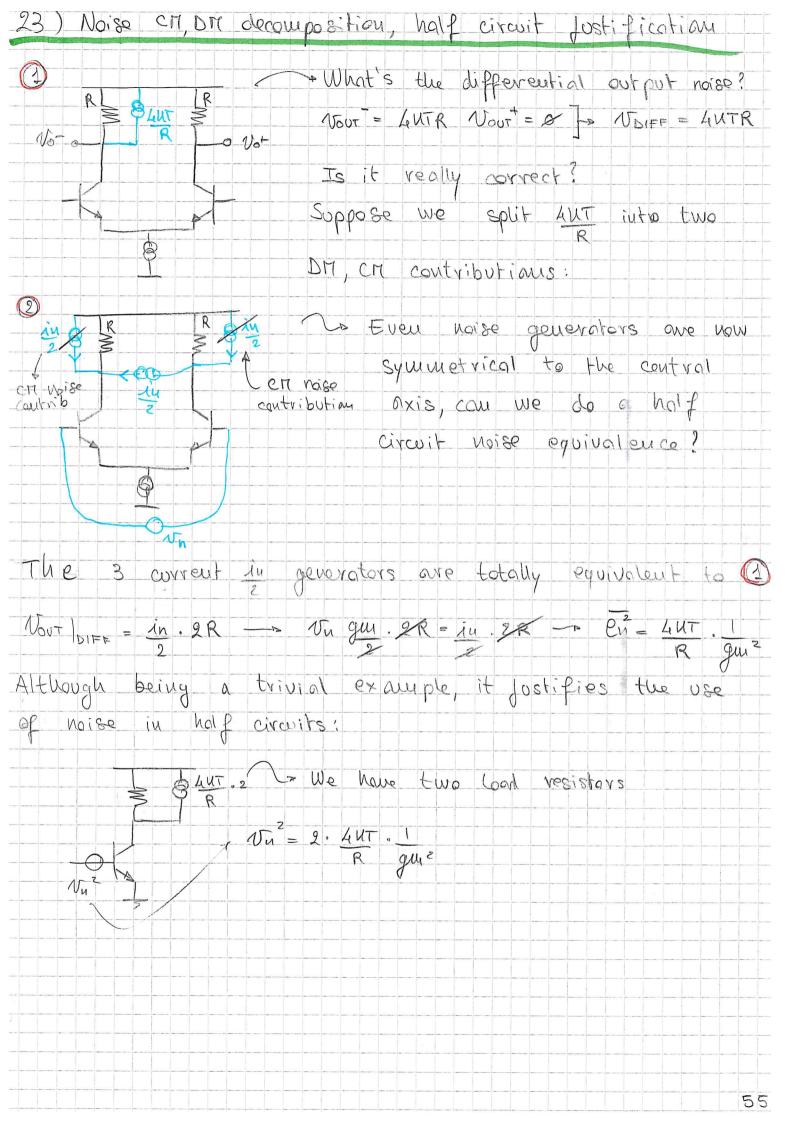

- 23. Differential and Common mode noise decomposition, half circuit justification

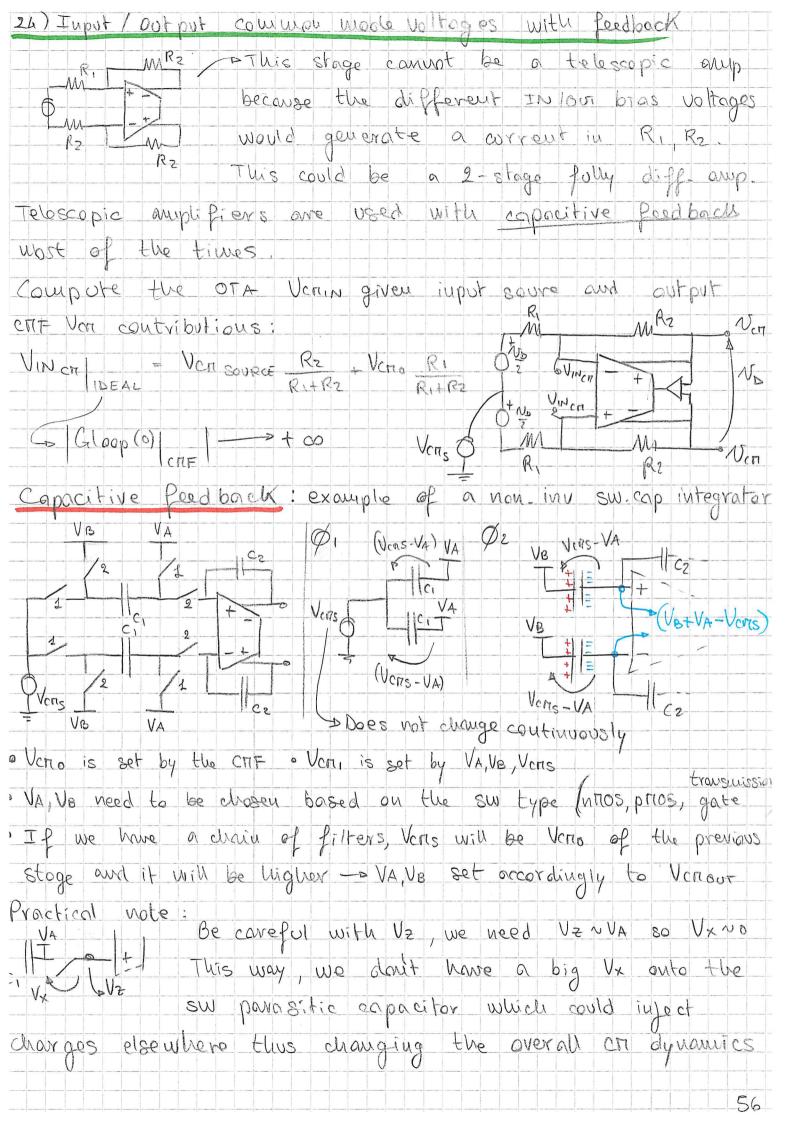

- 24. Setting input and ouput common mode voltages in a switched capacitor filter

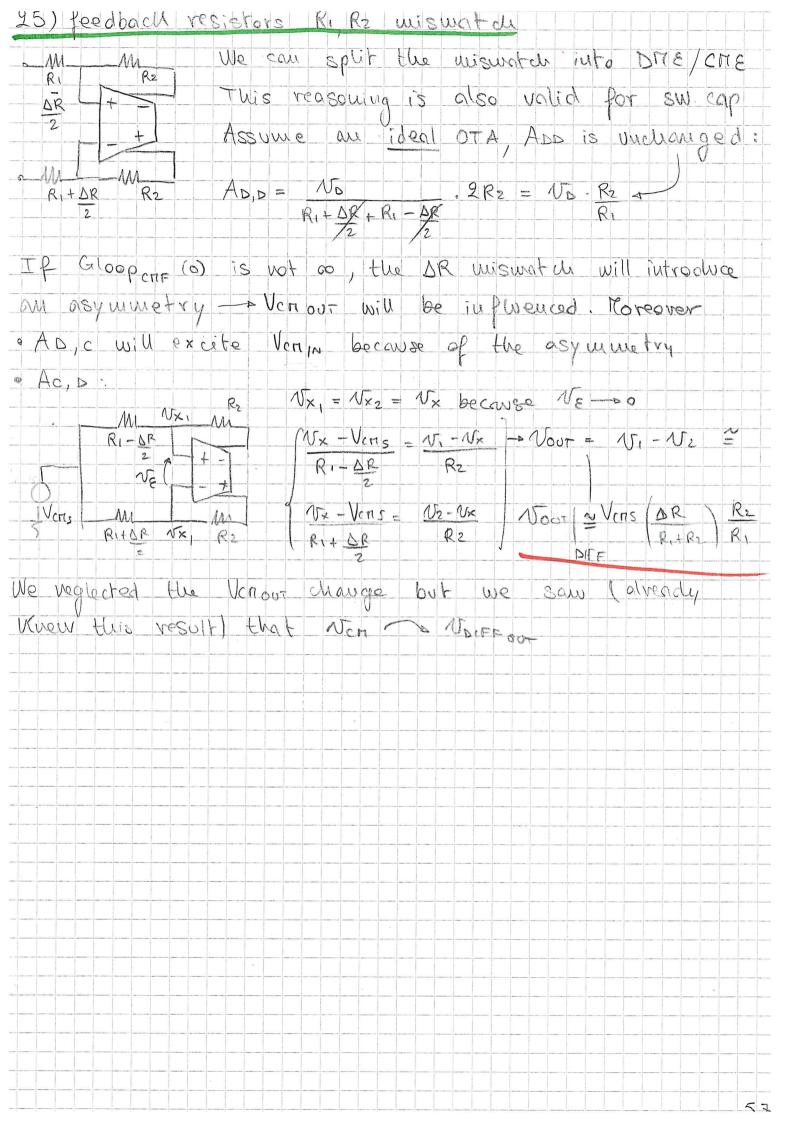

- 25. Mismatch of R1 and R2 in a fully differential amplifier

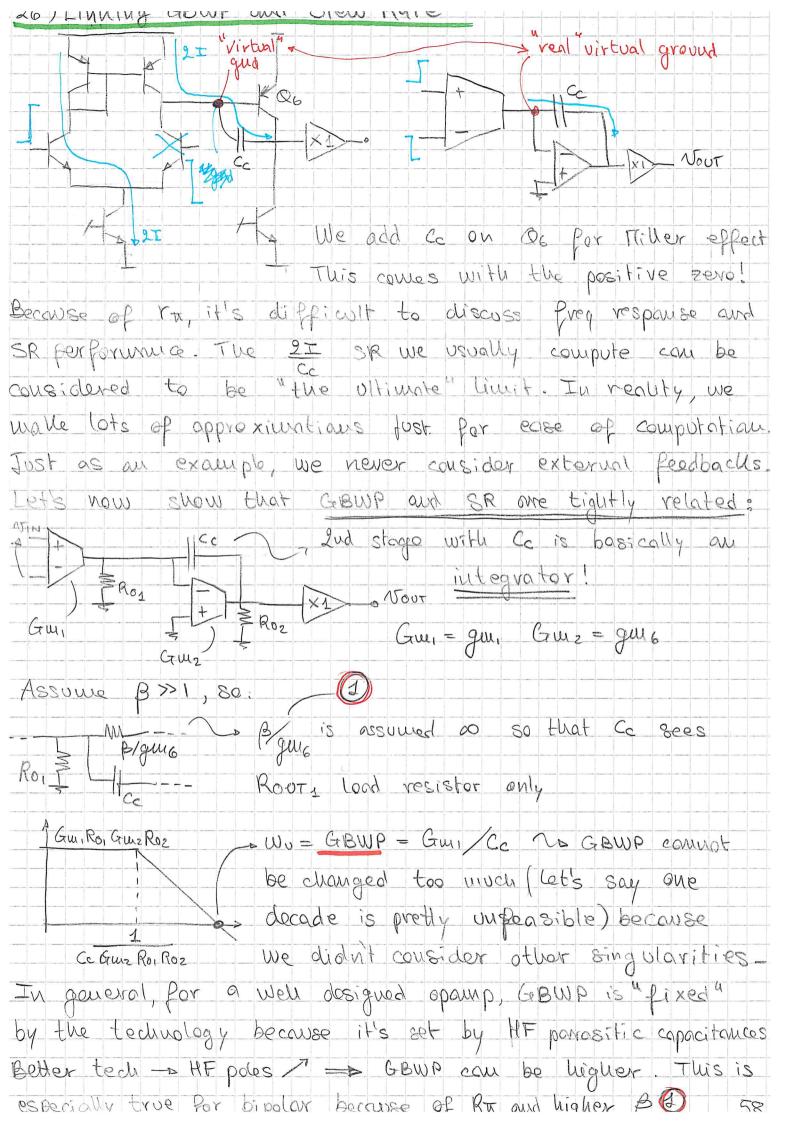

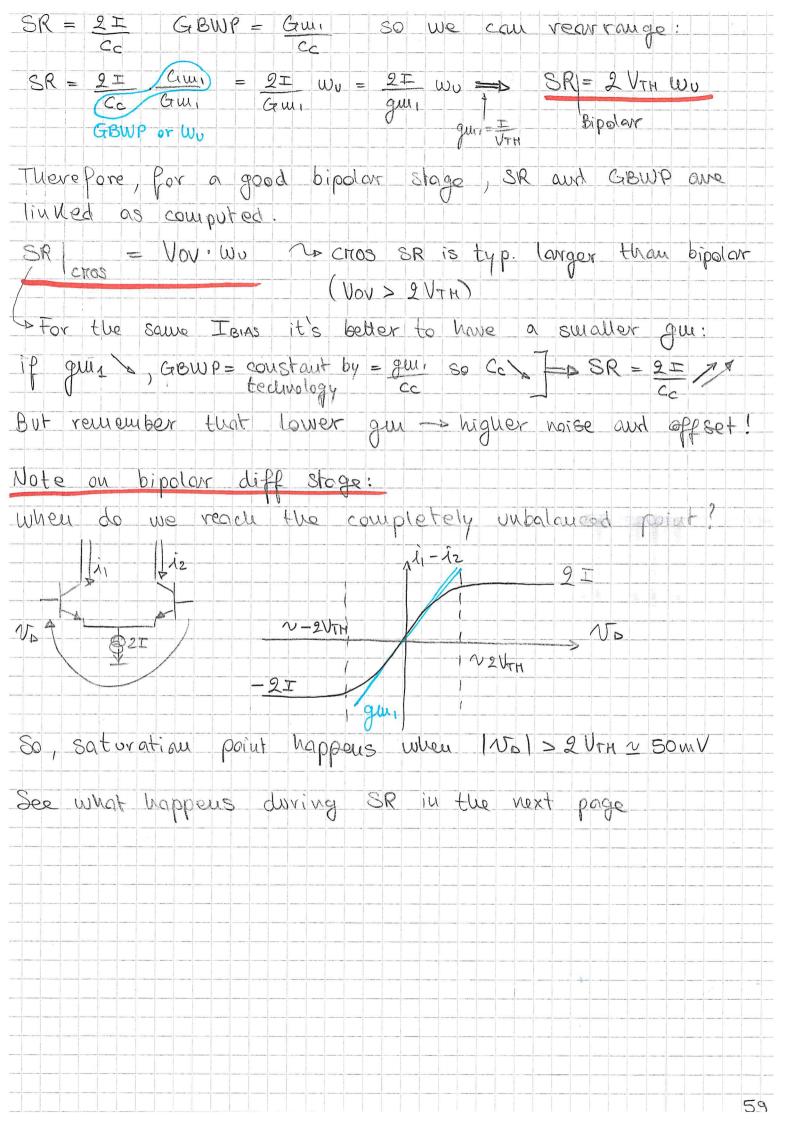

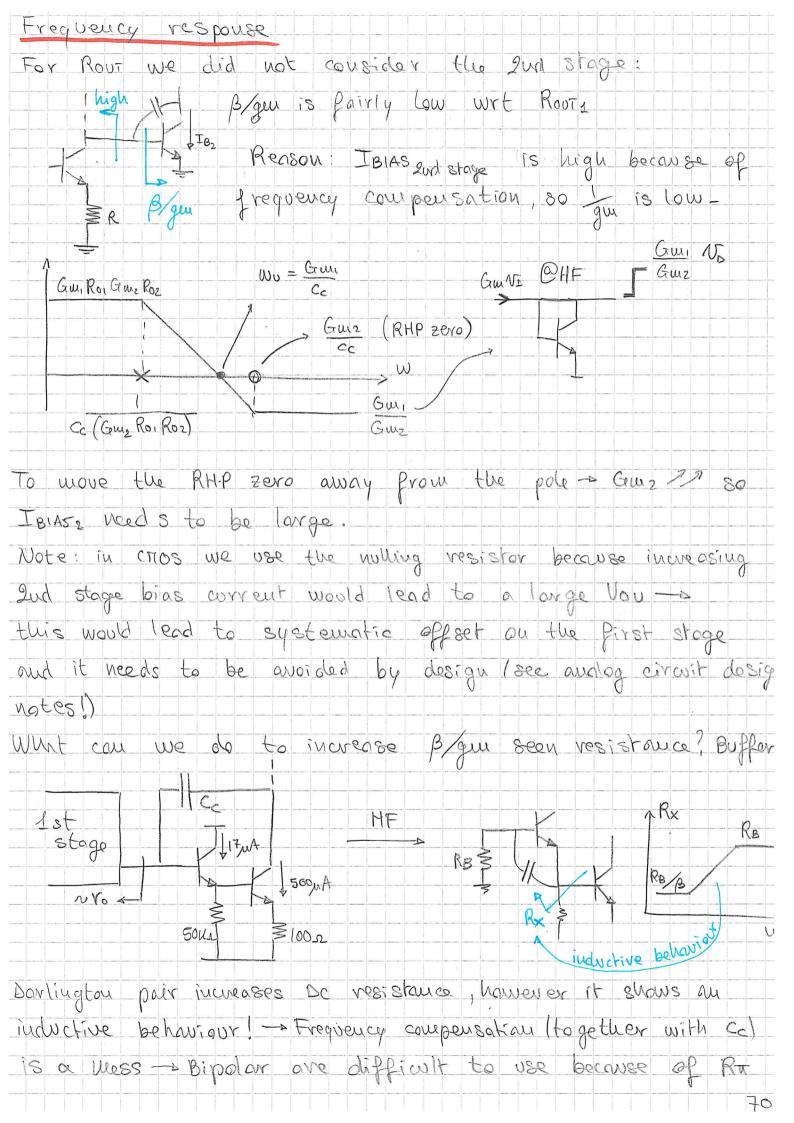

- 26. Slew Rate and Gain Bandwidth Product relation

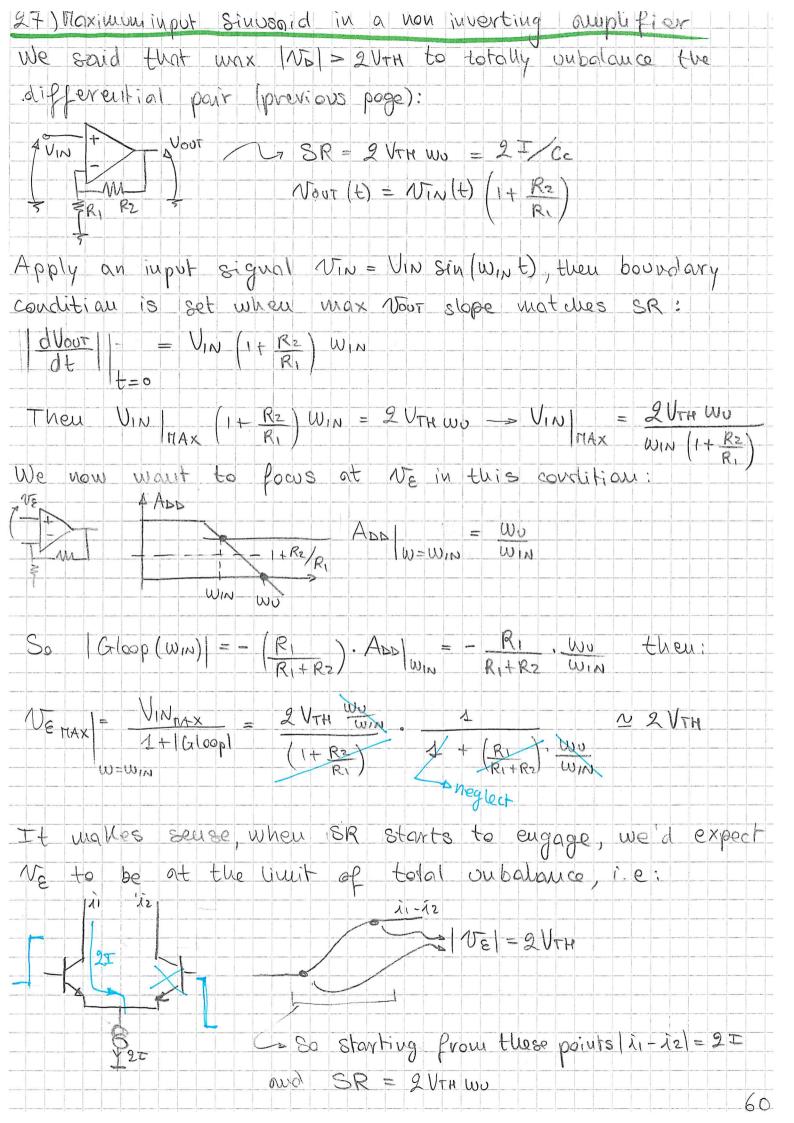

- 27. Maximum input sinusoid in a non inverting amplifier, Slew Rate condition

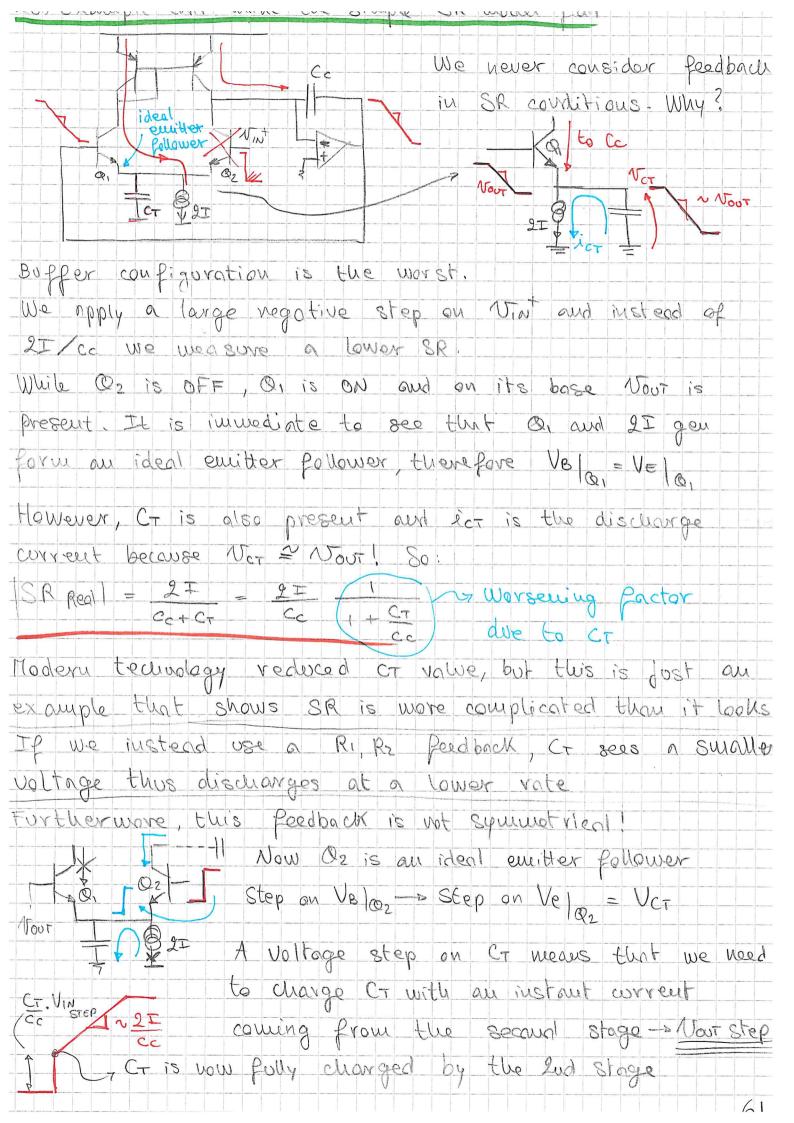

- 28. Examples that make simple Slew Rate model fail

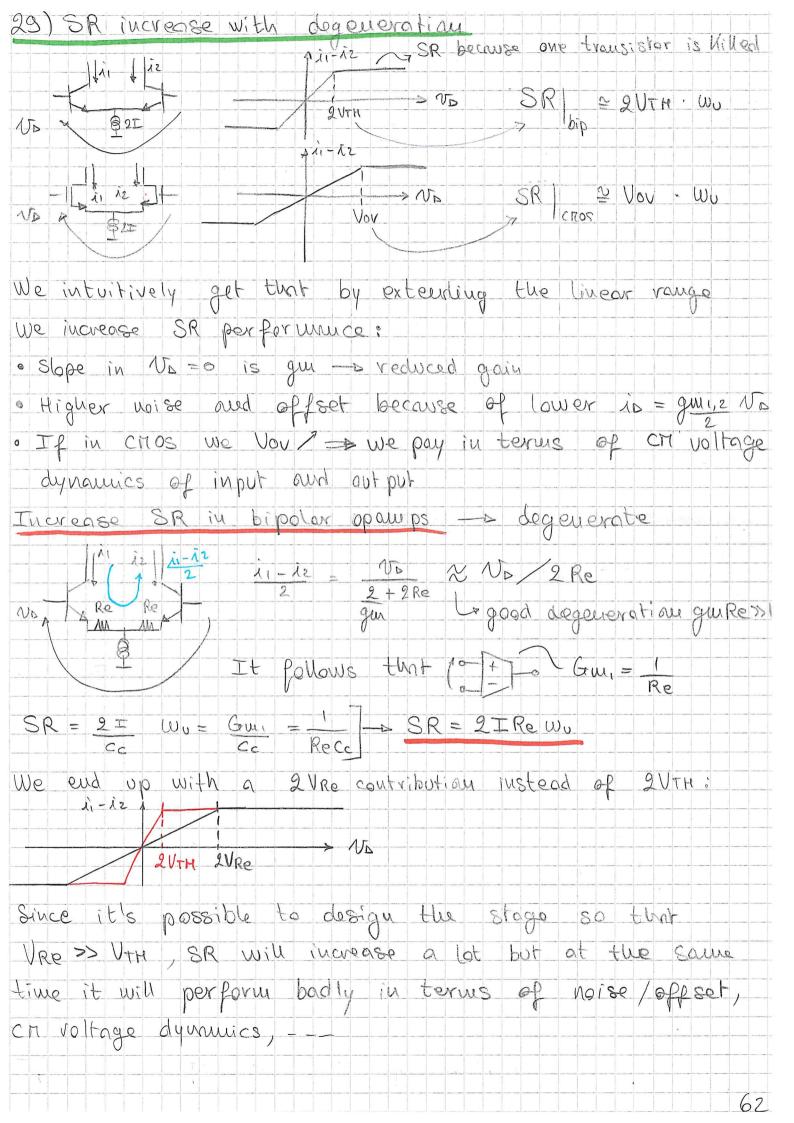

- 29. Slew Rate increase through input pair degeneration

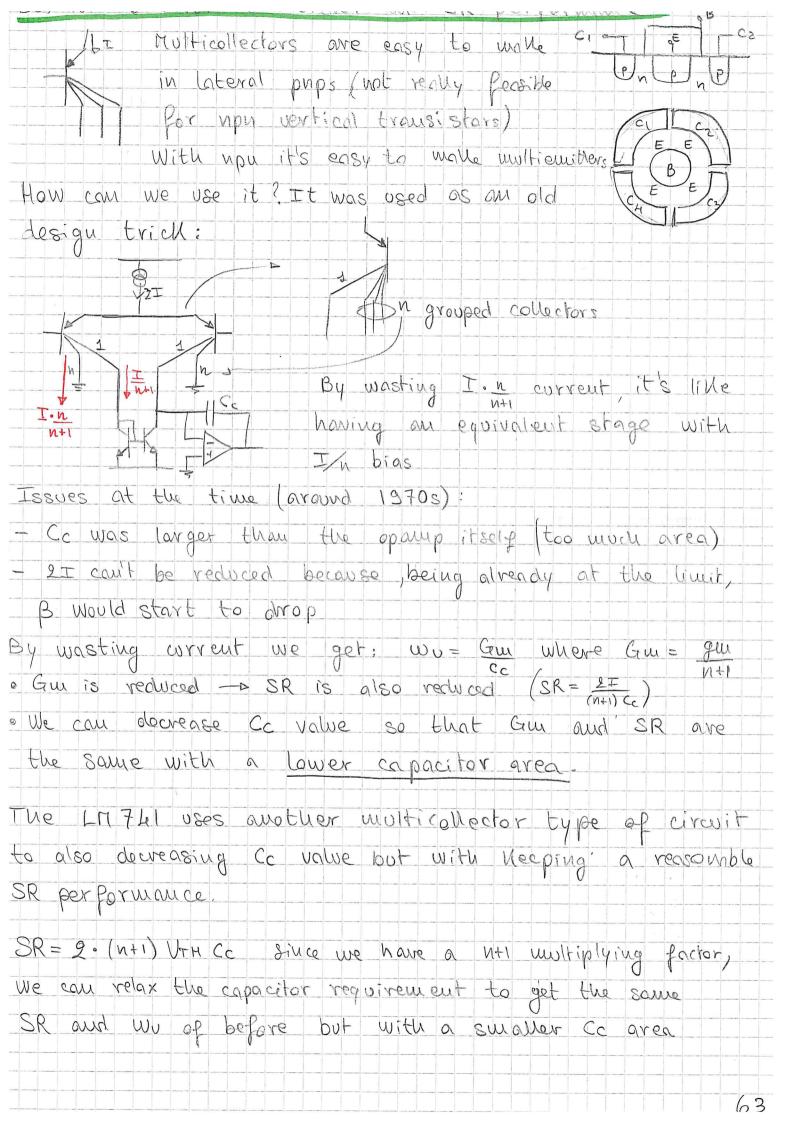

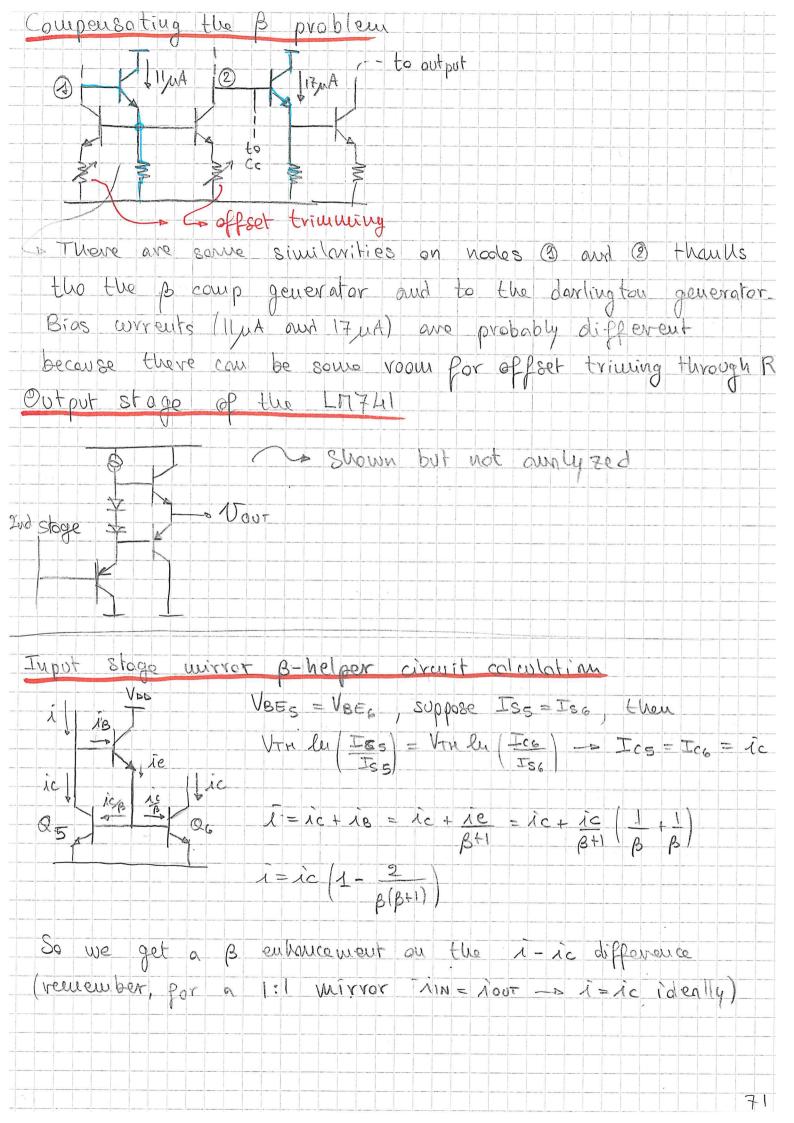

- 30. Multicollector transistors and Slew Rate performance

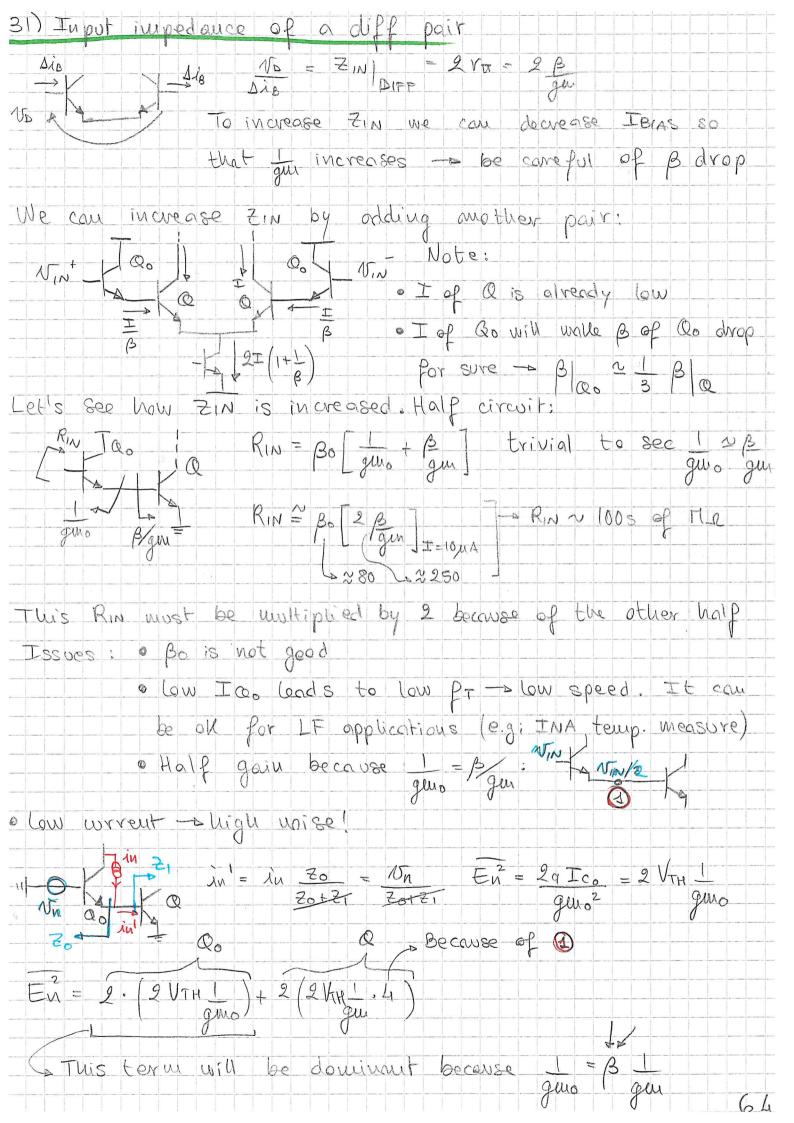

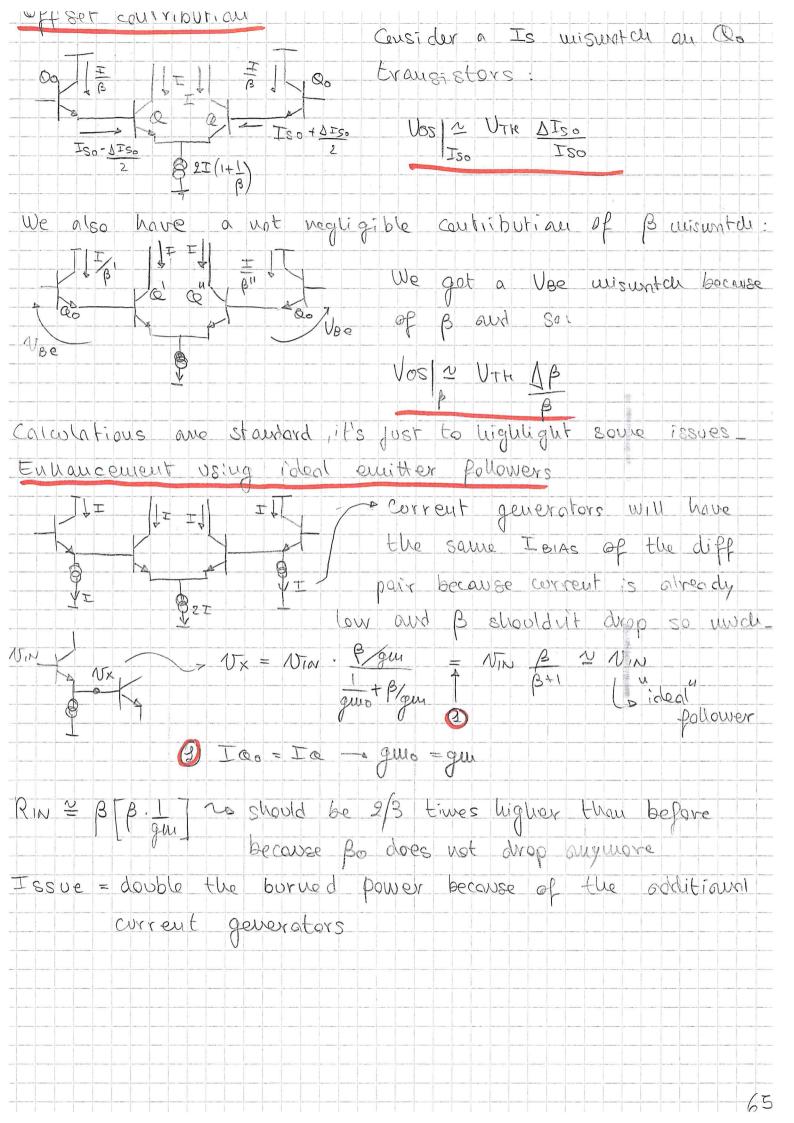

- 31. Input impedance of a differential pair: enhancement through buffers and additional transistors

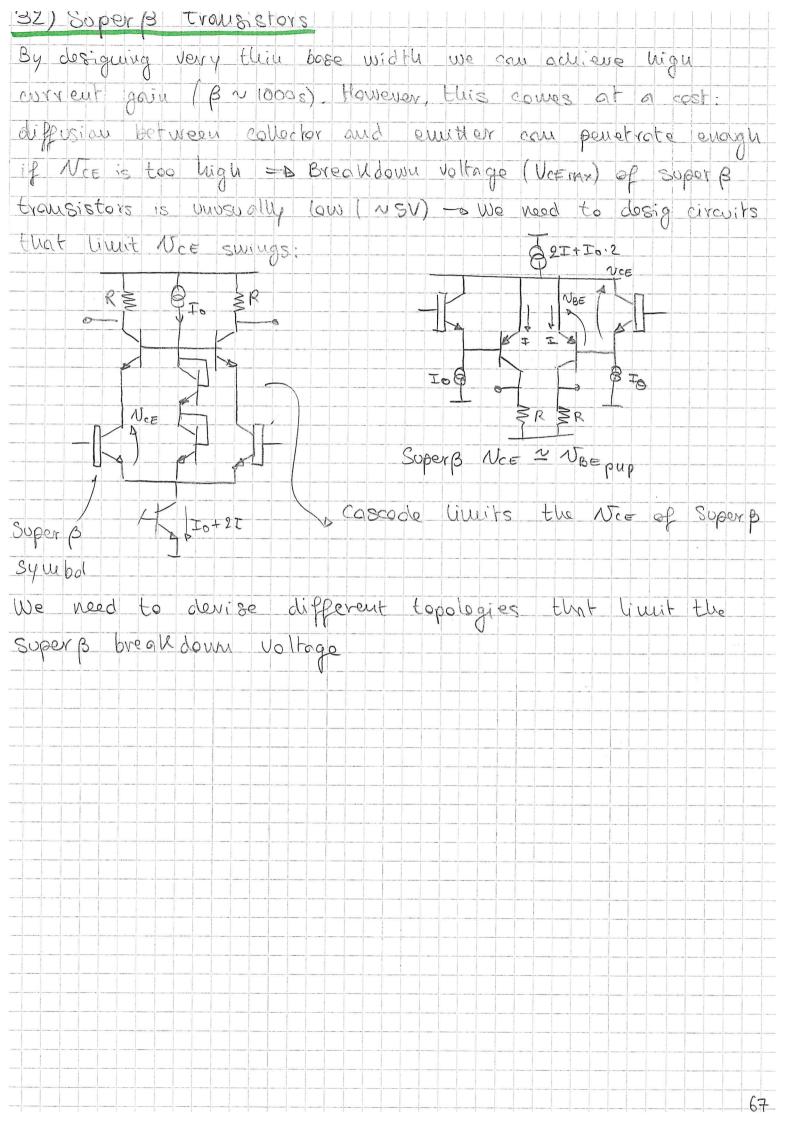

- 32. Super Beta transistors examples

- 33. LM741 analysis: level shift issue, new input stage idea, noise, offset, compensation and multicollector input stage analysis for Slew Rate

- 34. Current reference: simple example and Sensitivity definition

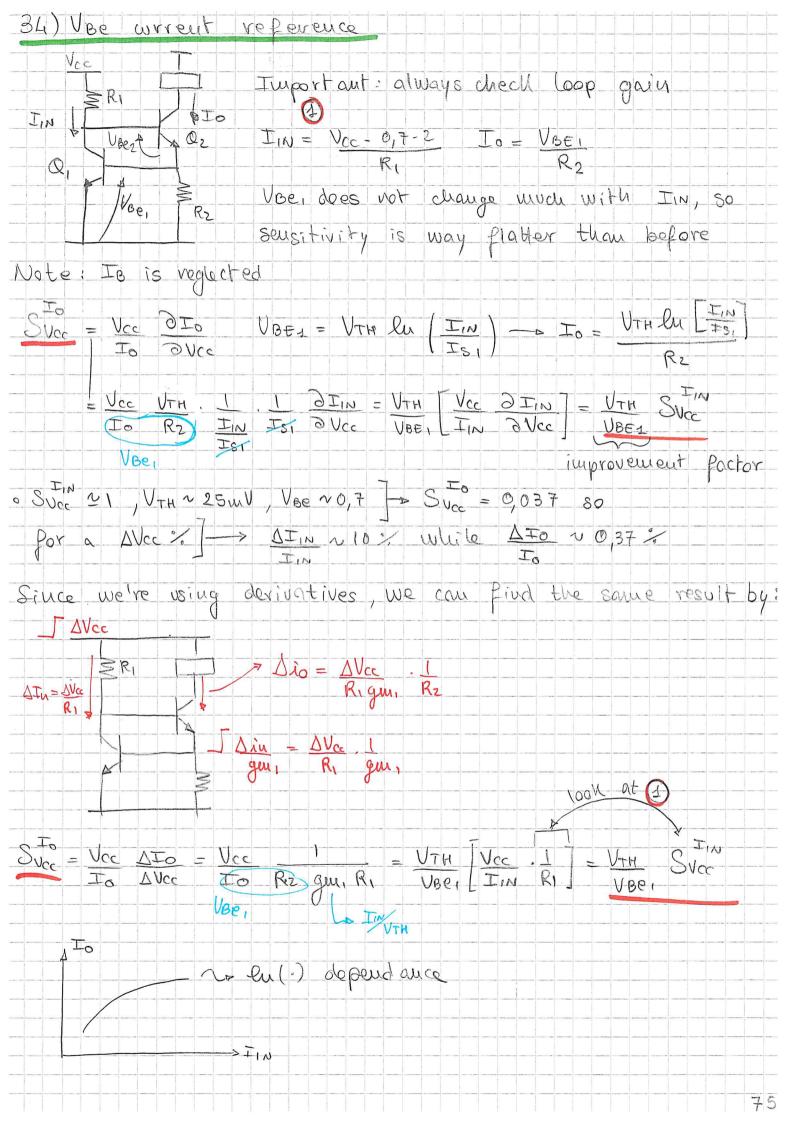

- 35. Vbe bipolar current reference

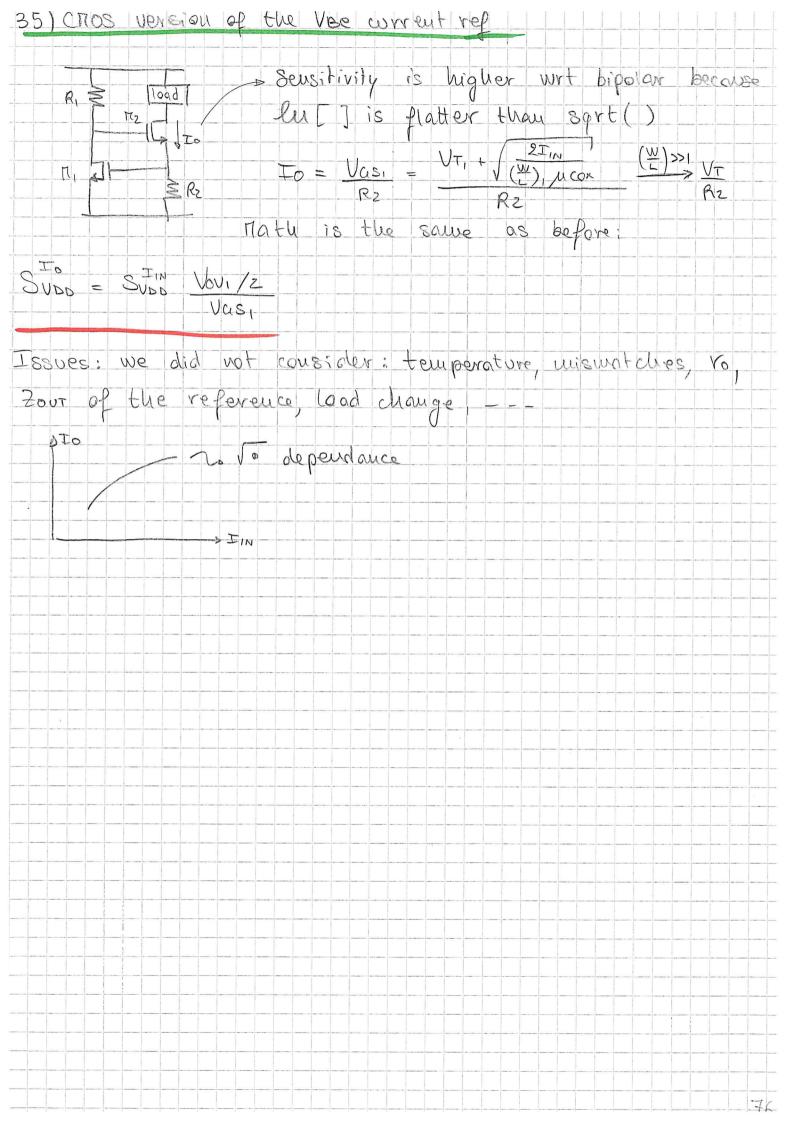

- 36. "Vgs" CMOS current reference

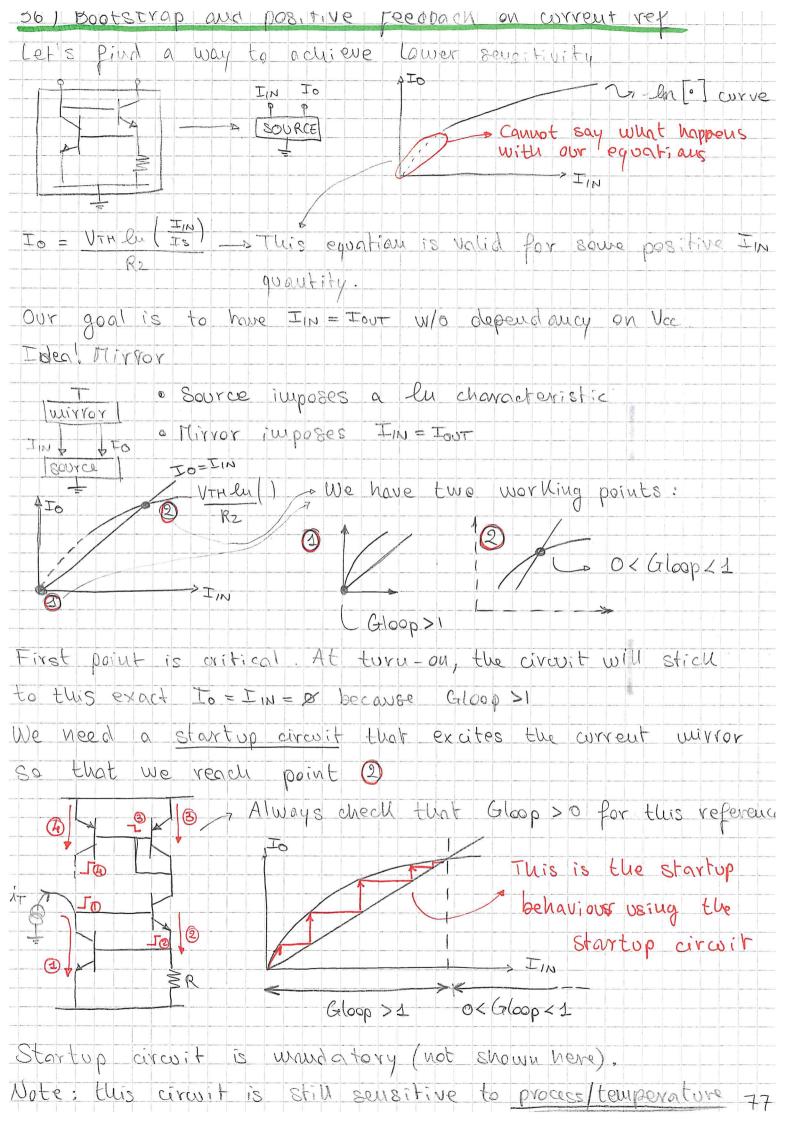

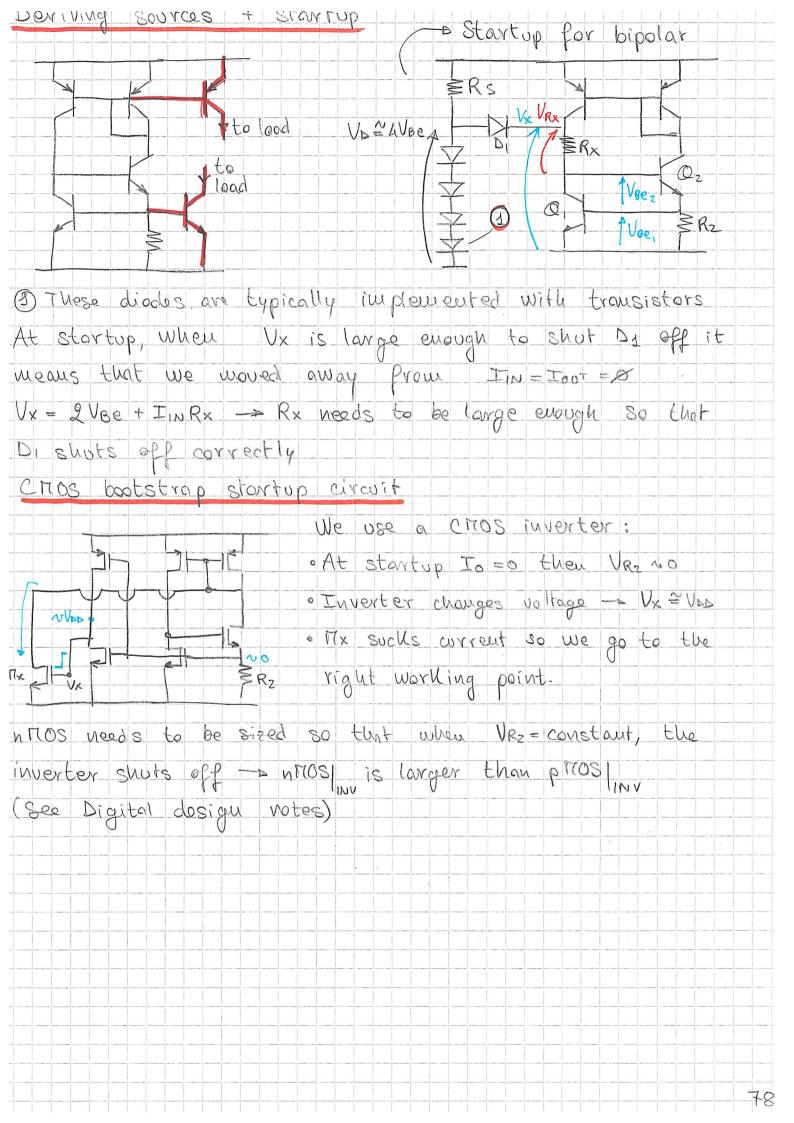

- 37. Bootstrap and positive feedback on current references

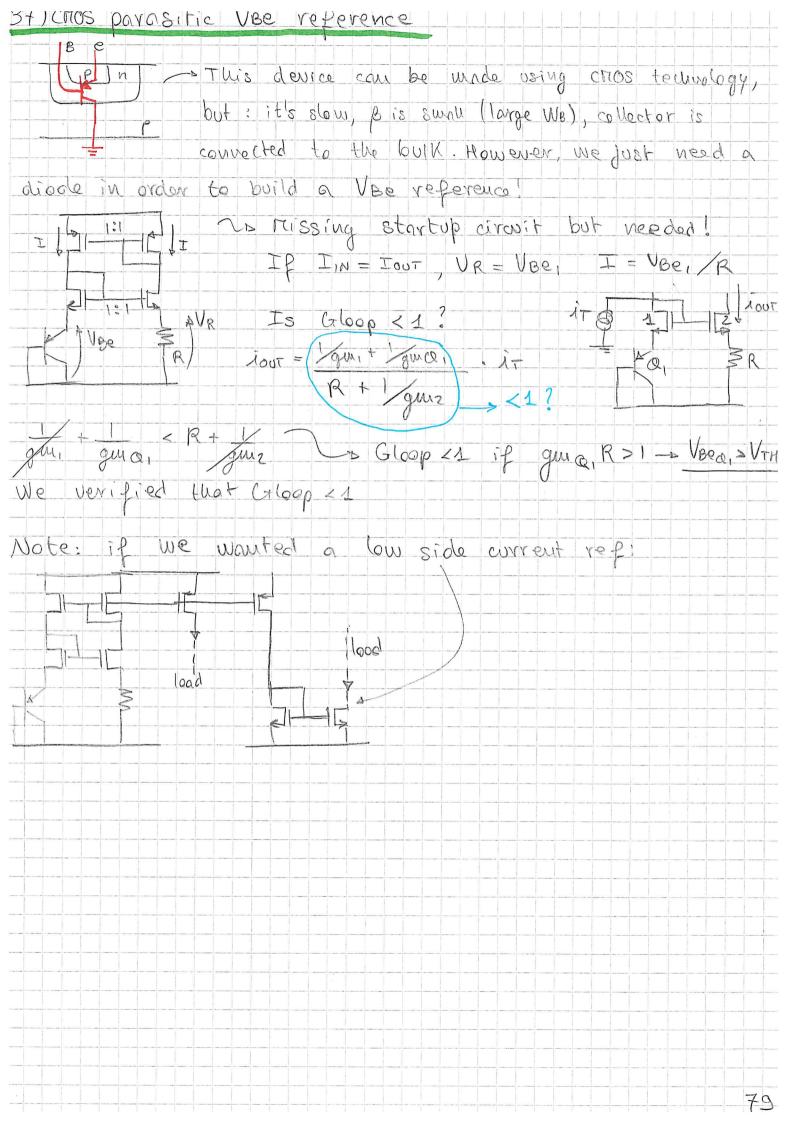

- 38. Vbe parasitic CMOS current reference

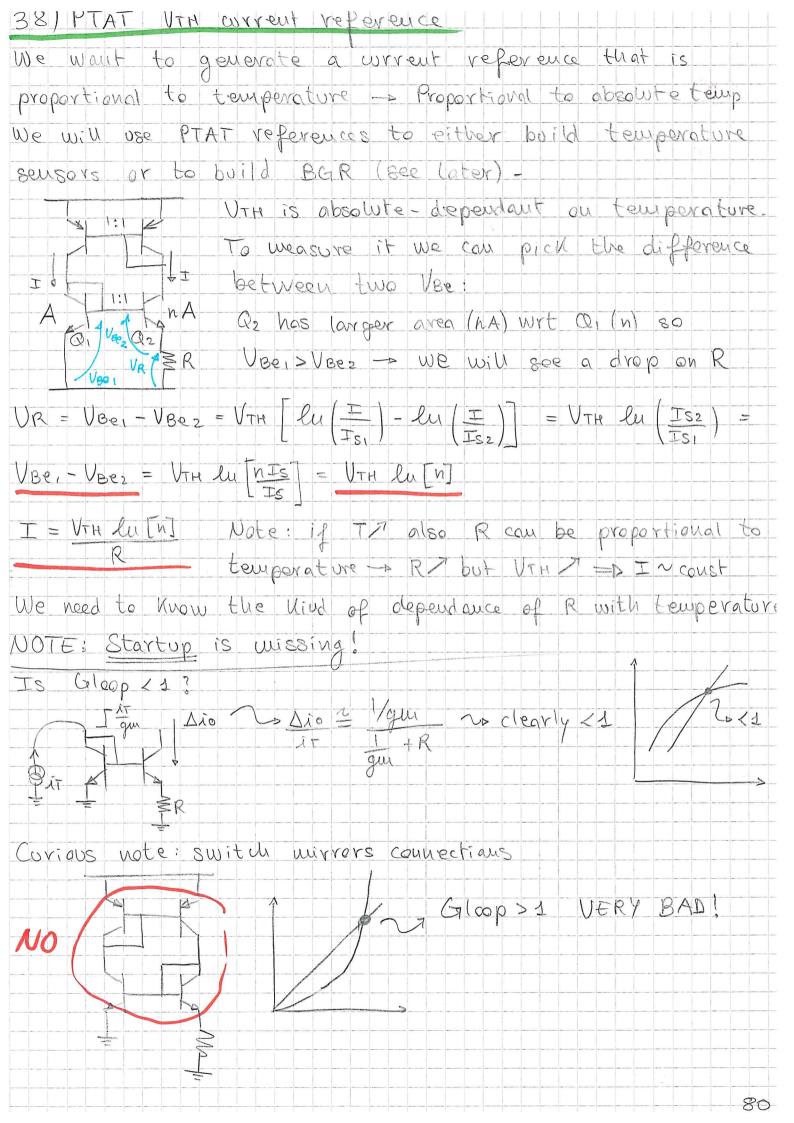

- 39. PTAT current reference using thermal voltage

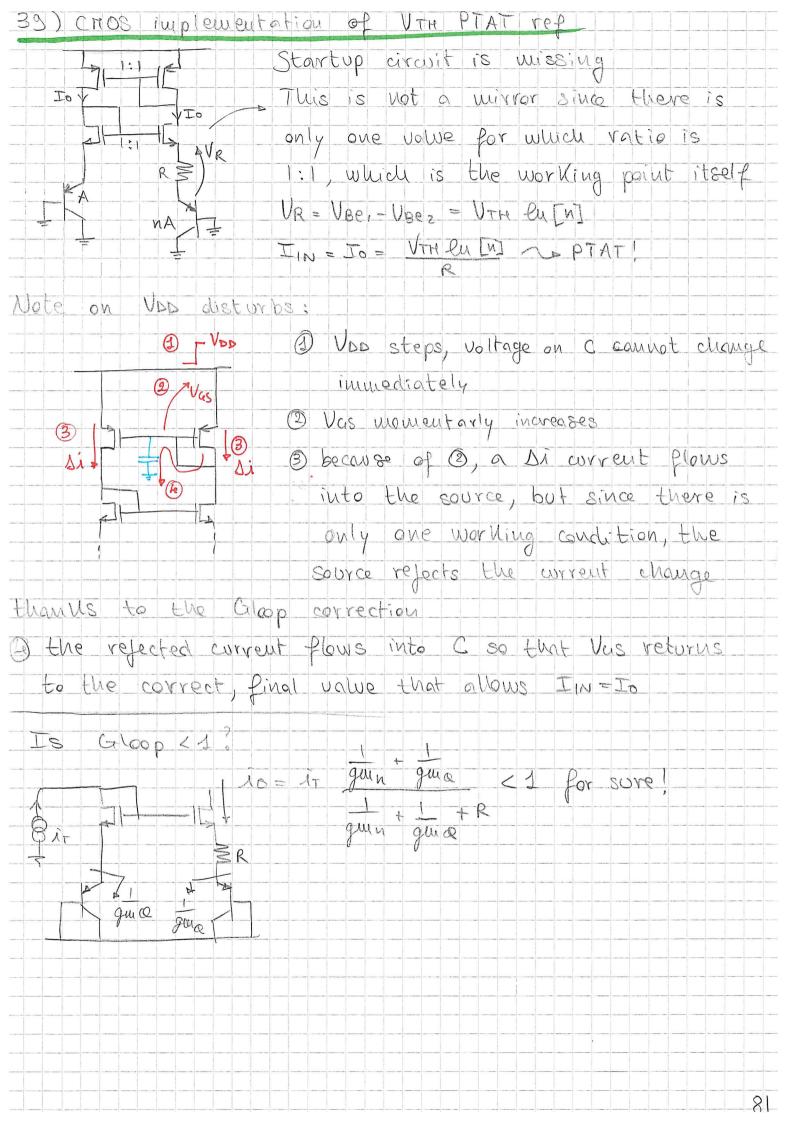

- 40. PTAT CMOS implementation

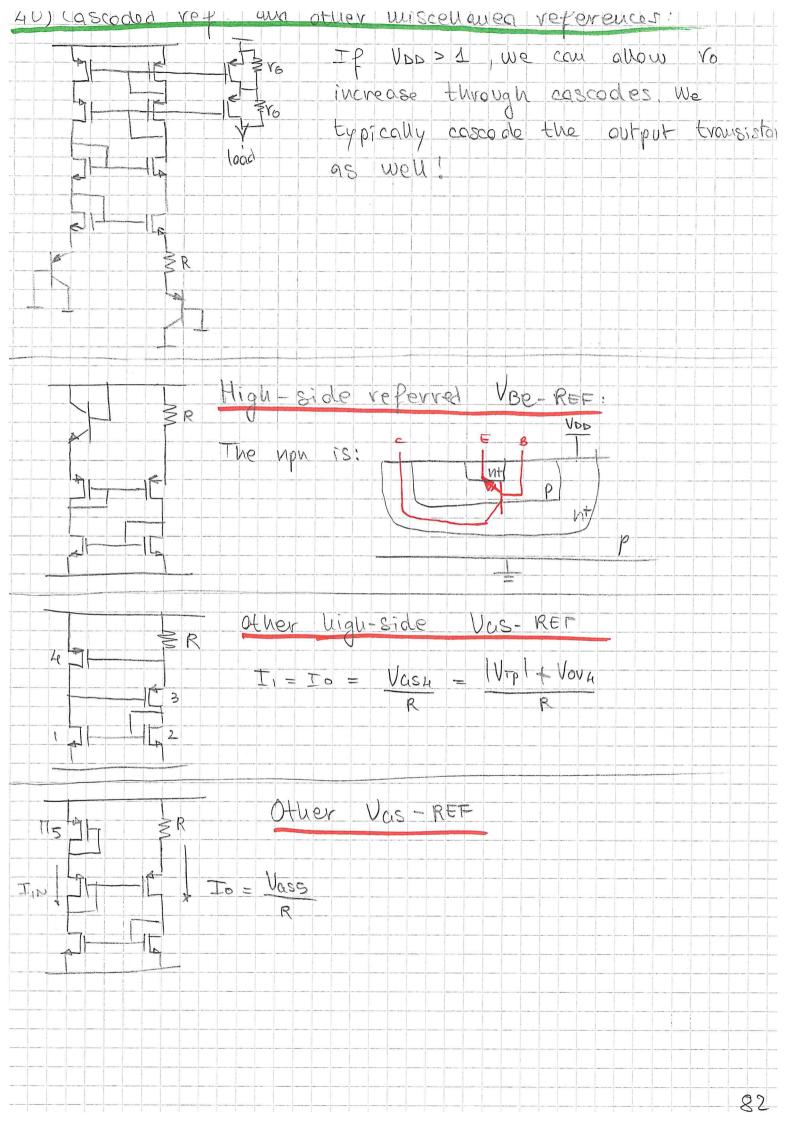

- 41. Cascoded current references and high-side circuits

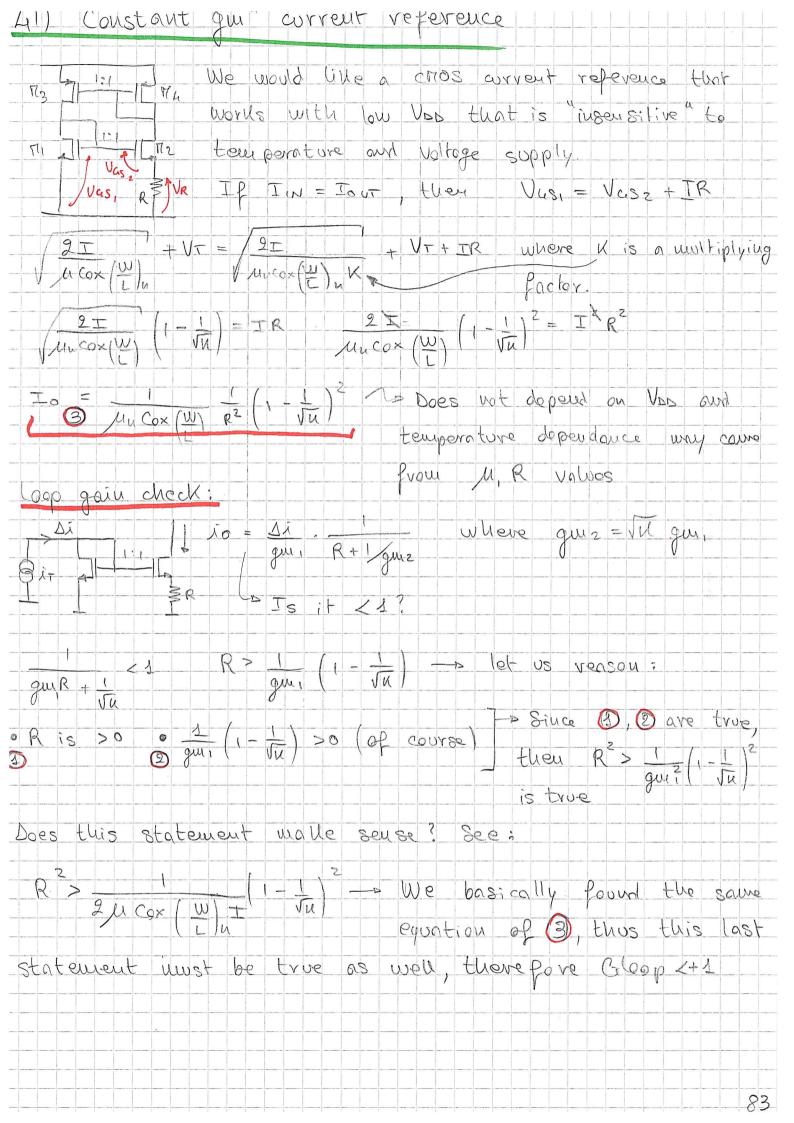

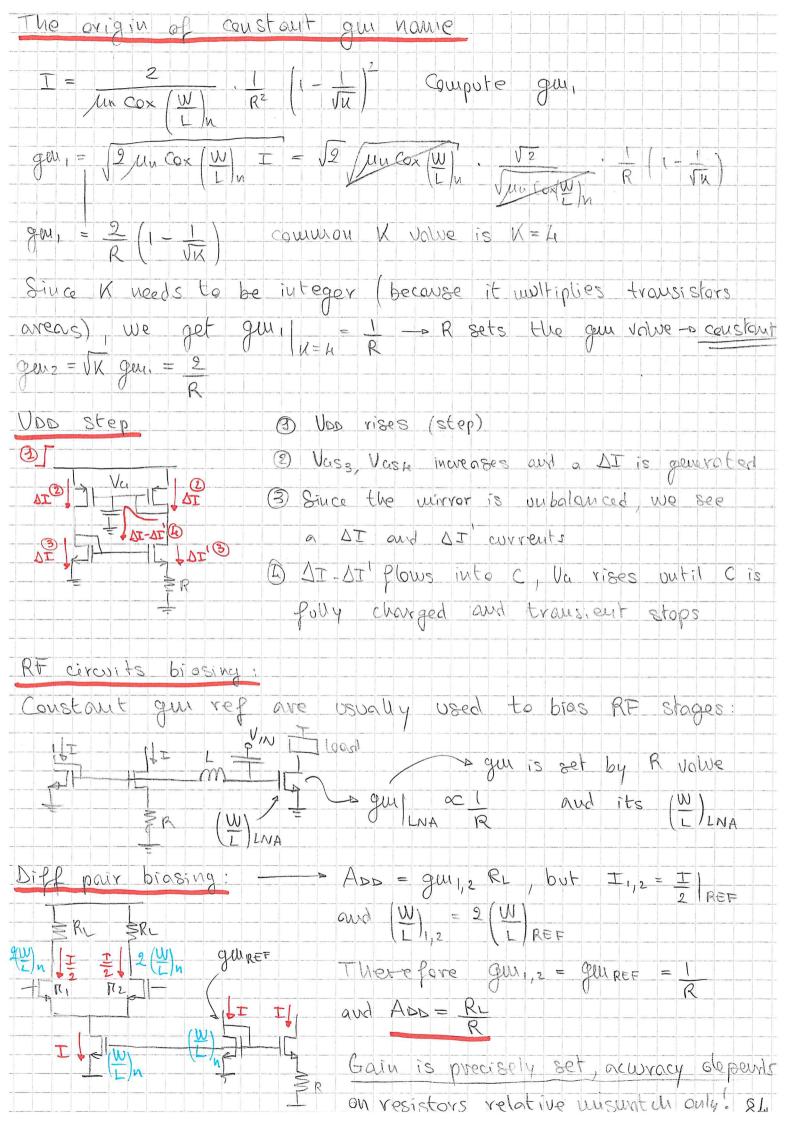

- 42. "Constant gm" current reference

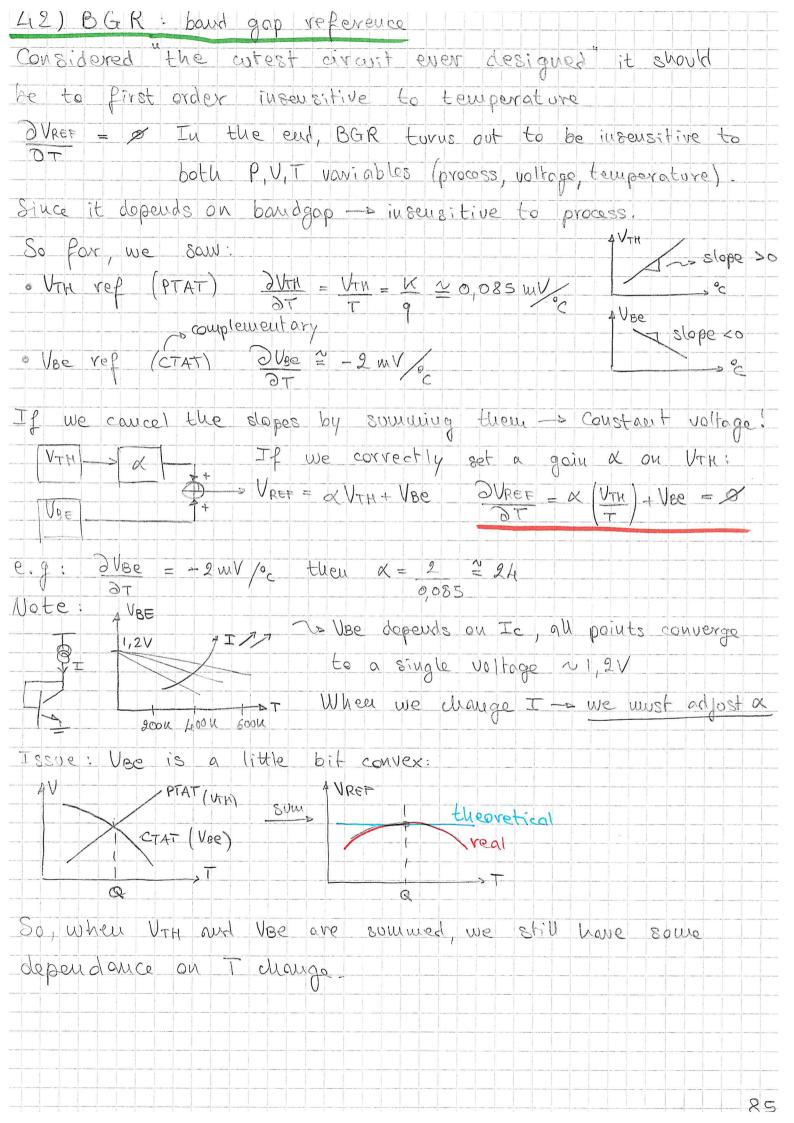

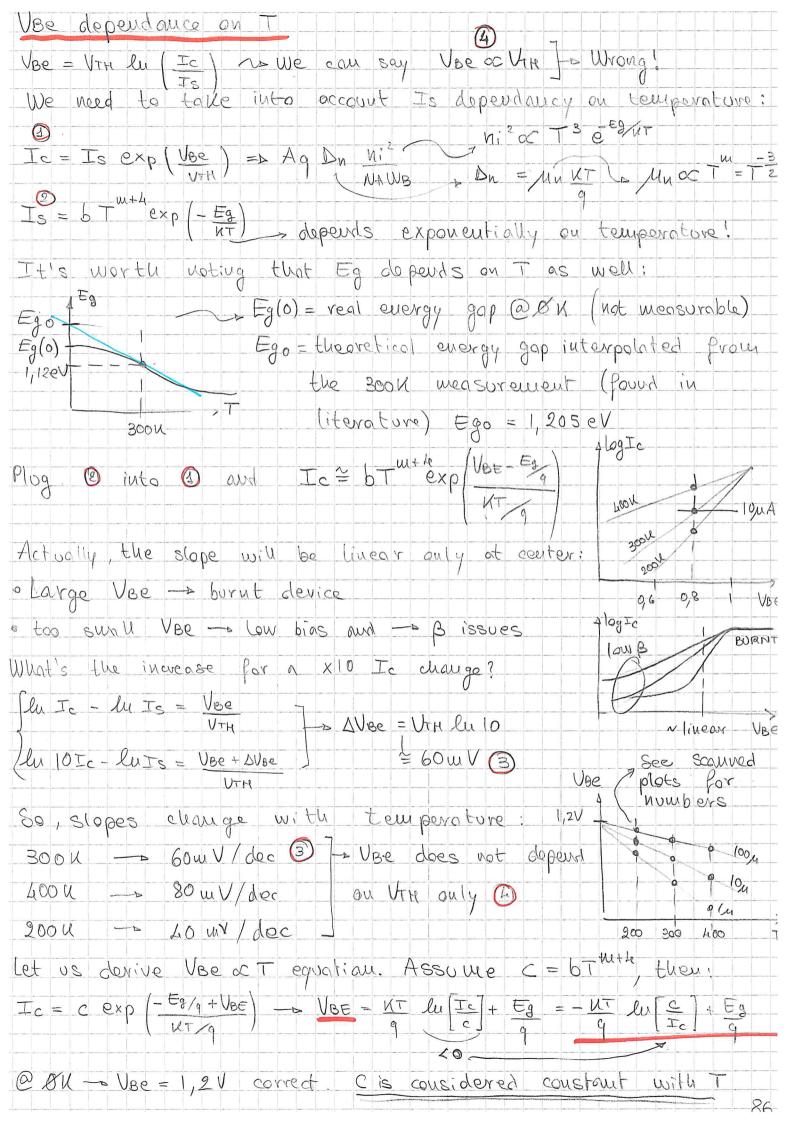

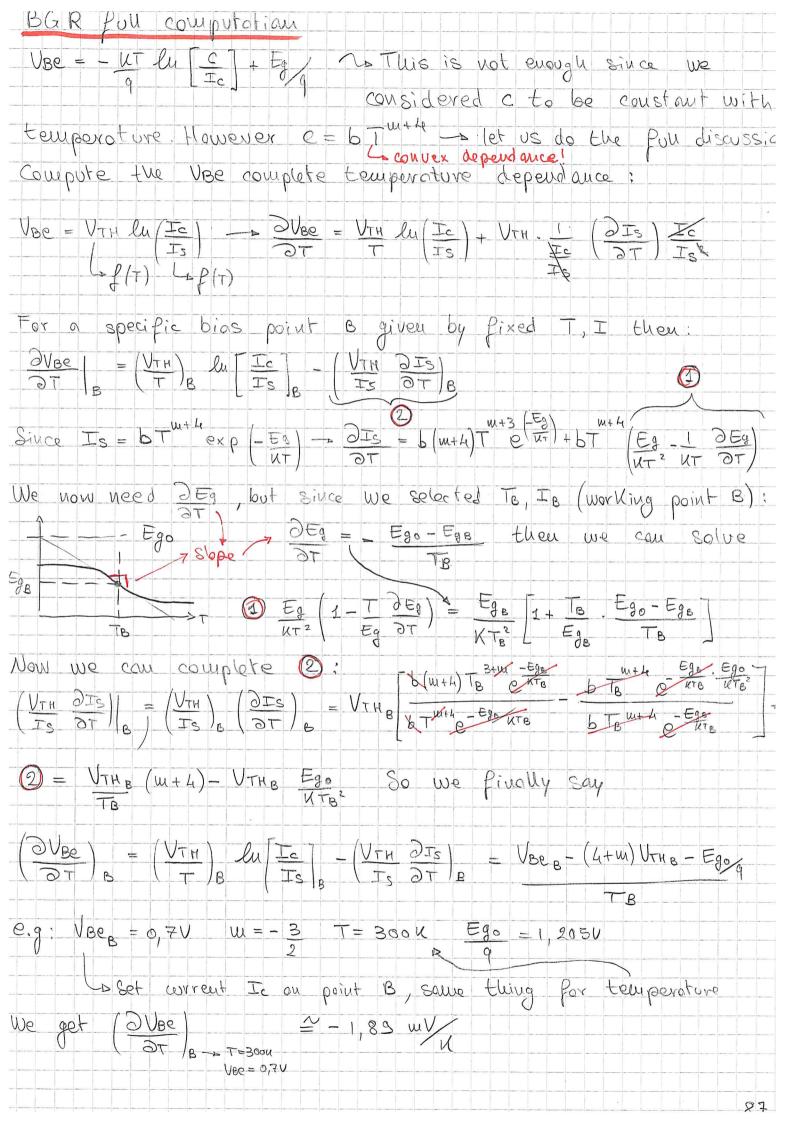

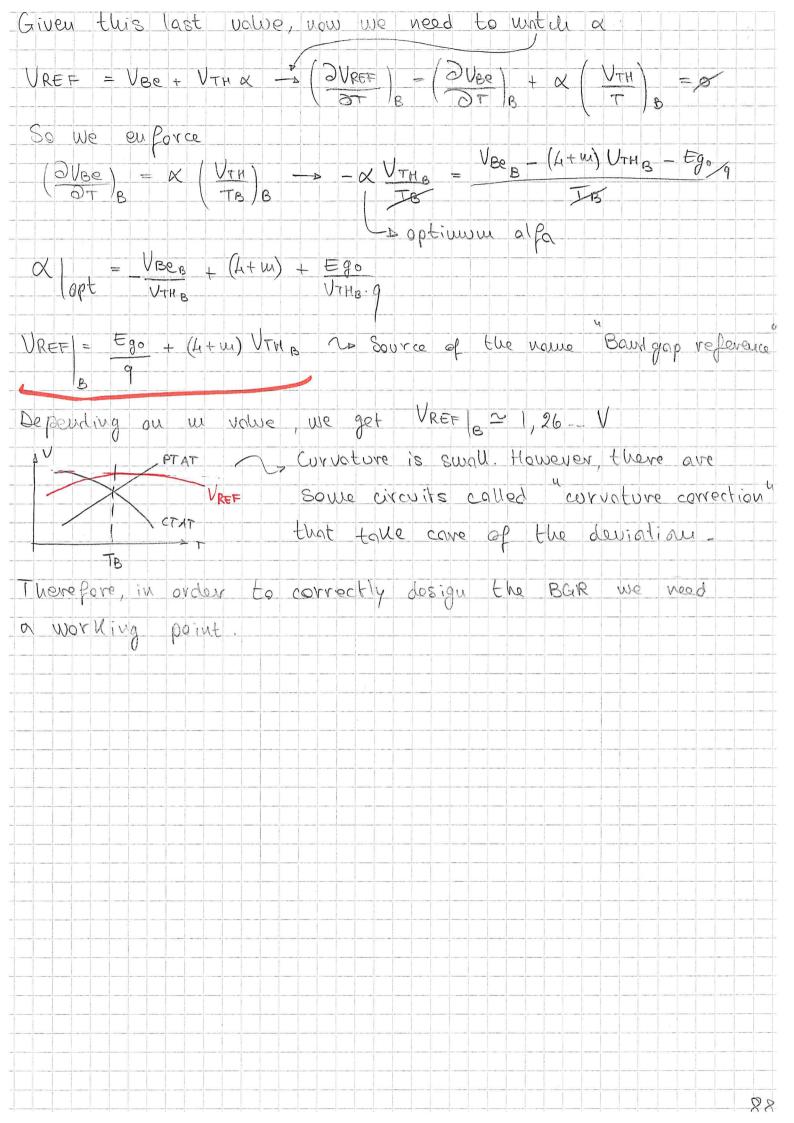

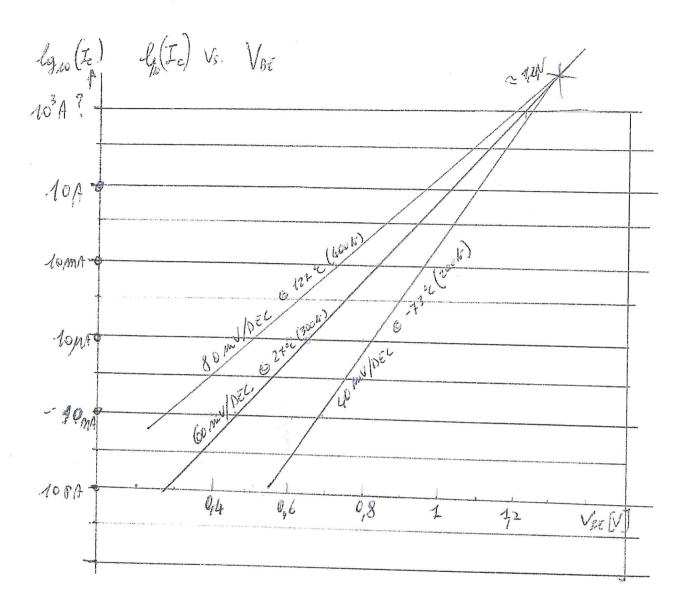

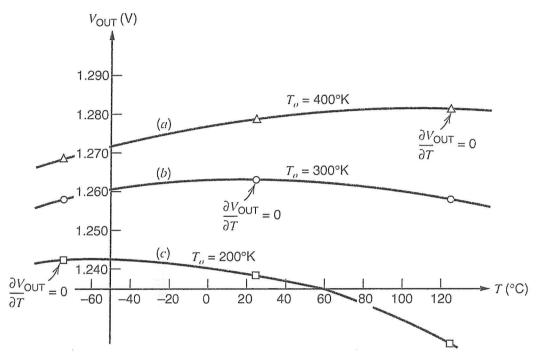

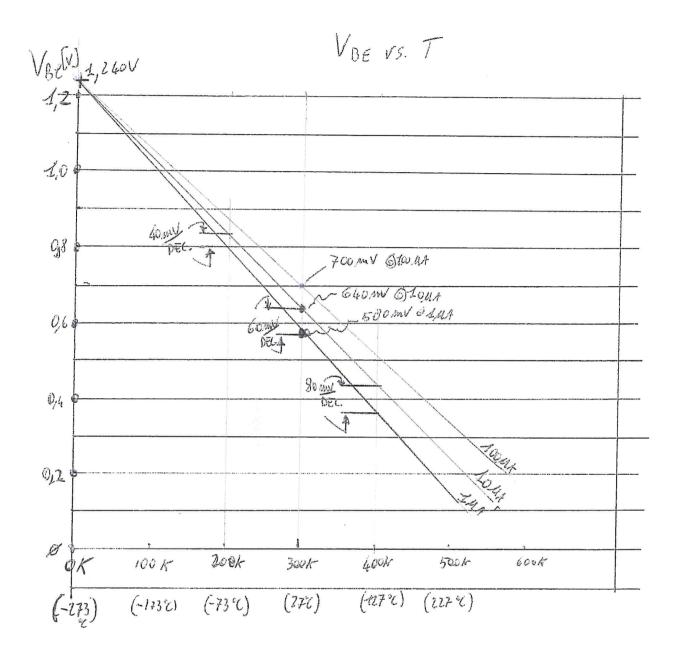

- 43. Bandgap Reference (BGR): idea and full computation

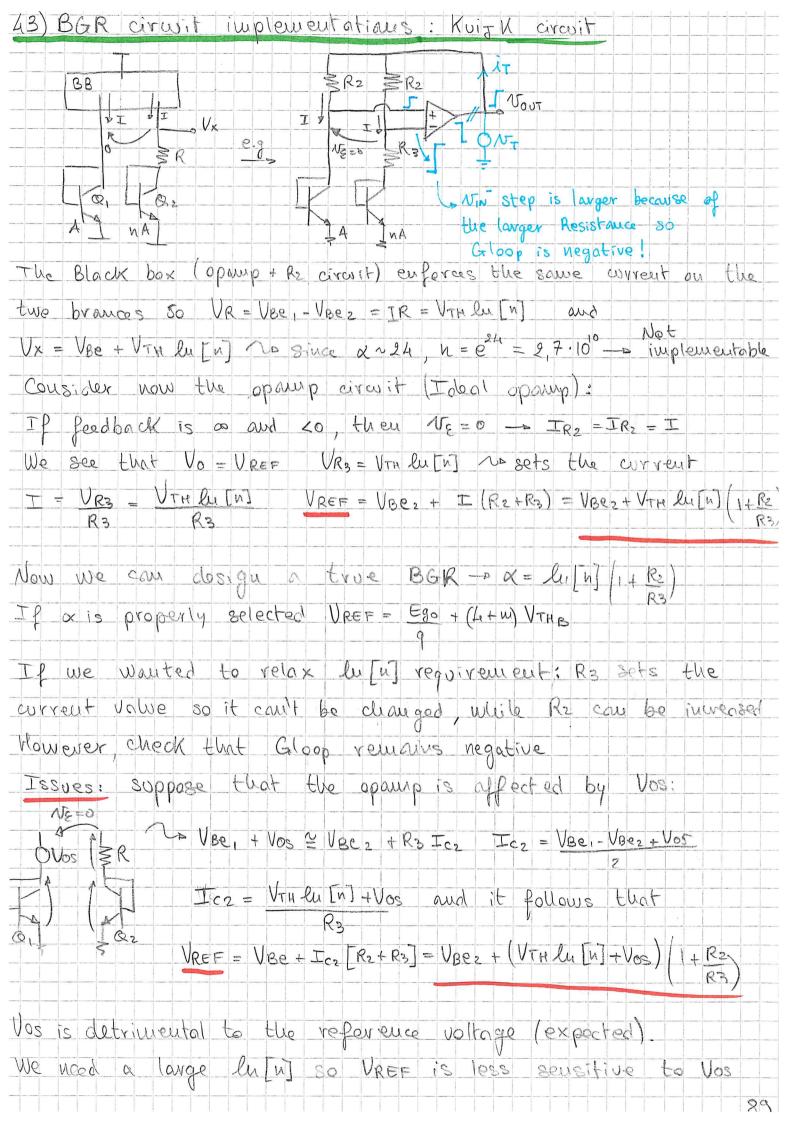

- 44. BGR circuit implementation: Kuijk circuit

- 45. BGR circuit implementation: Brokaw circuit

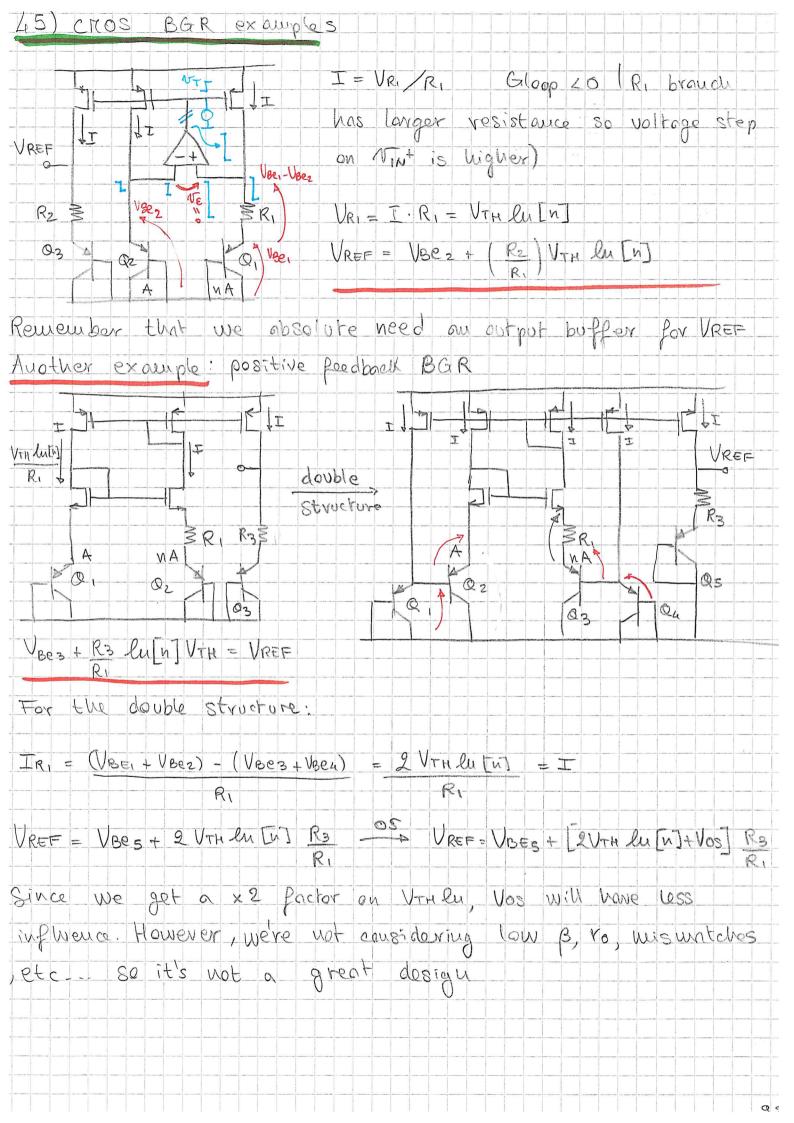

- 46. BGR CMOS examples

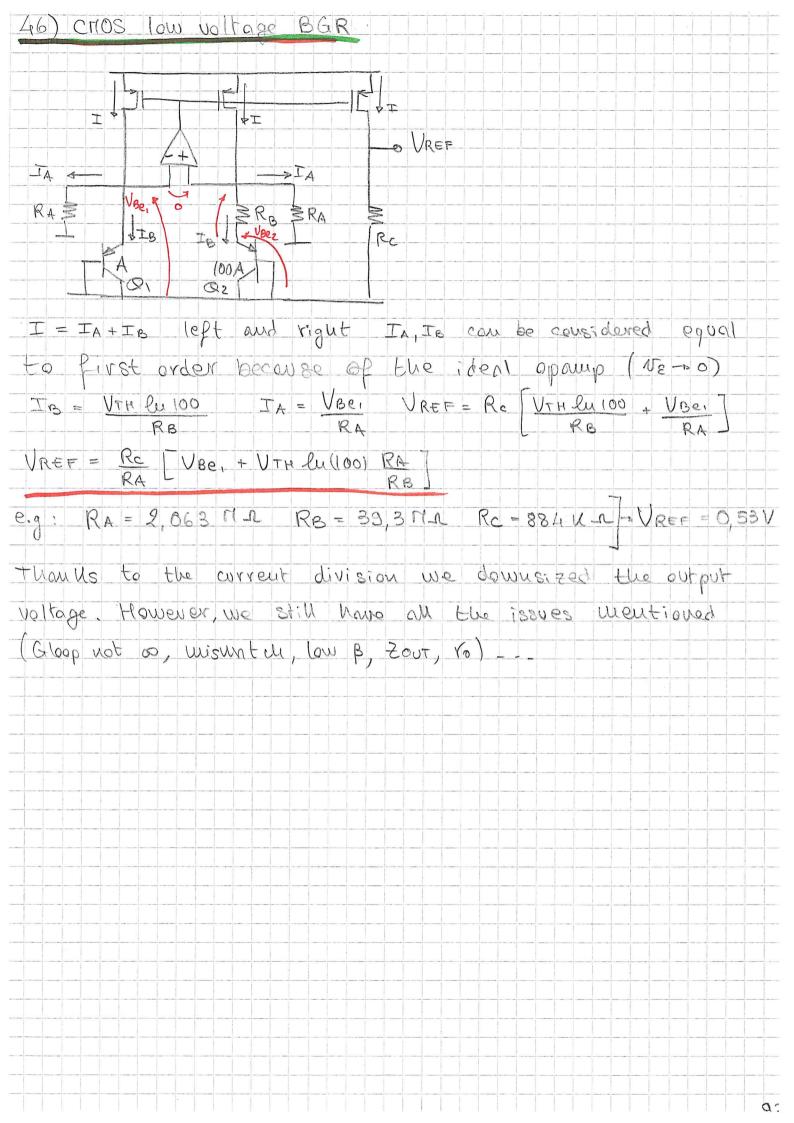

- 47. BGR low voltage circuit implementation

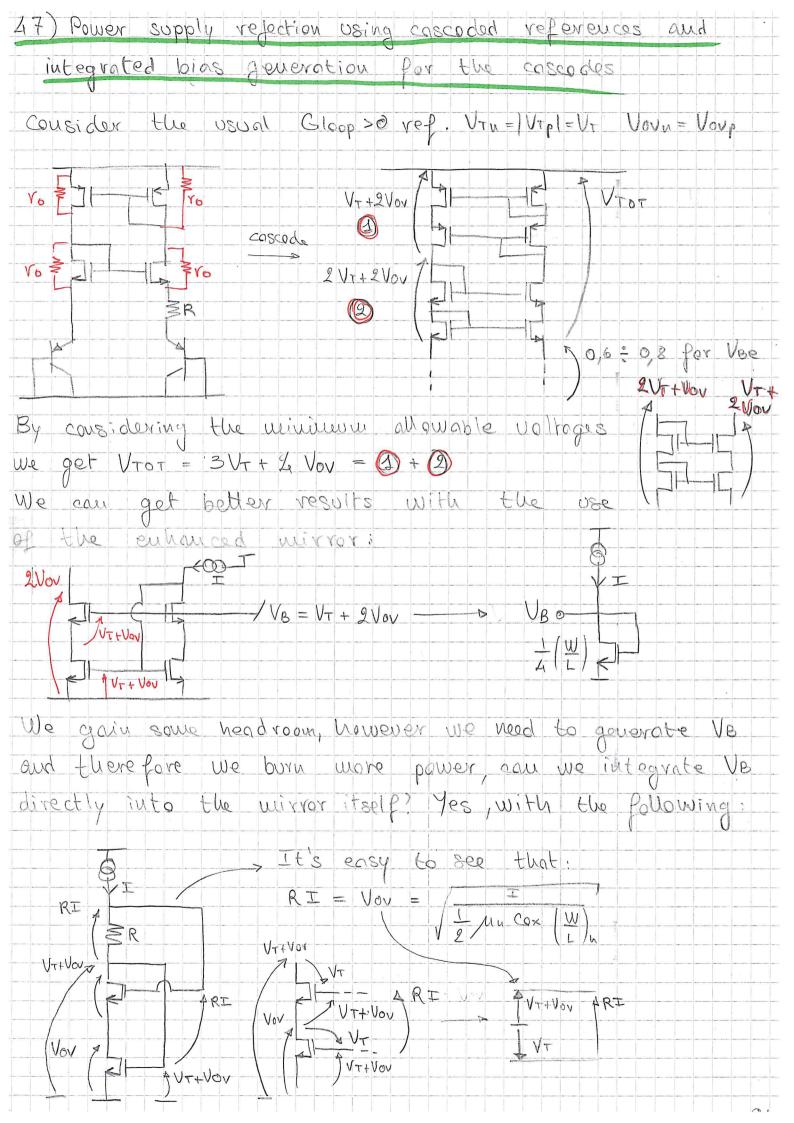

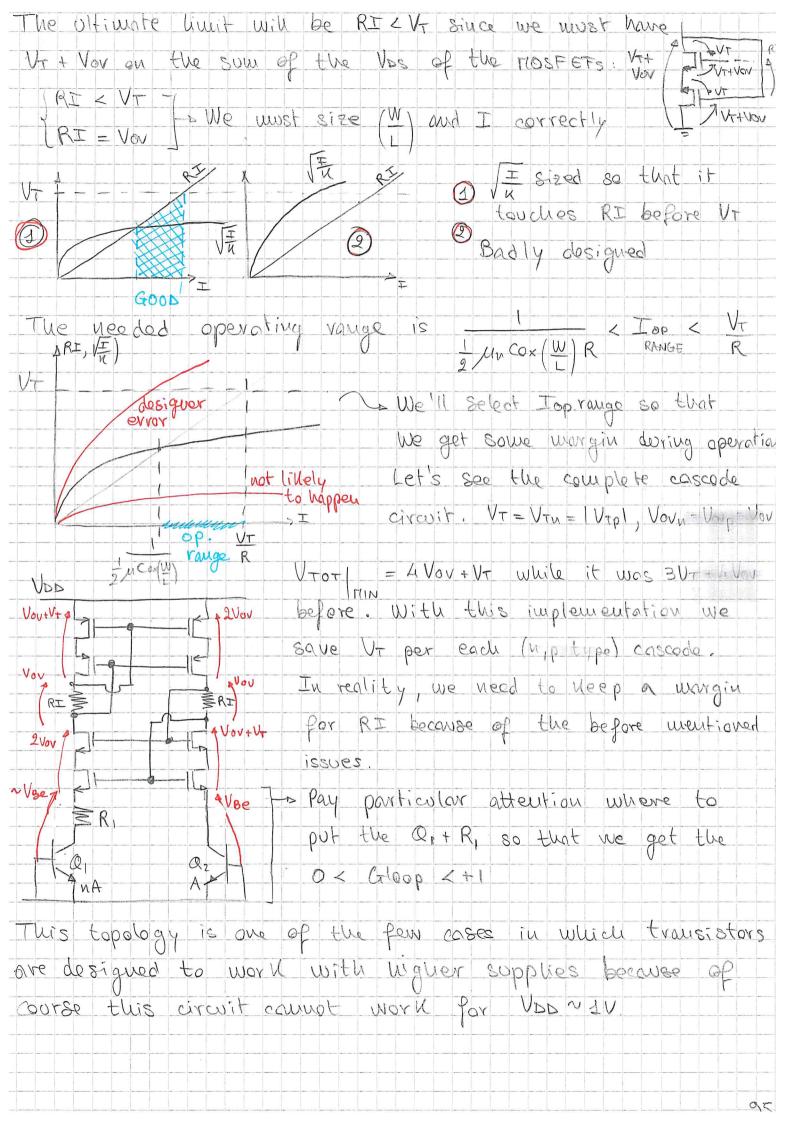

- 48. Power Supply Rejection using cascoded references and integrated bias generator for cascode bias voltage

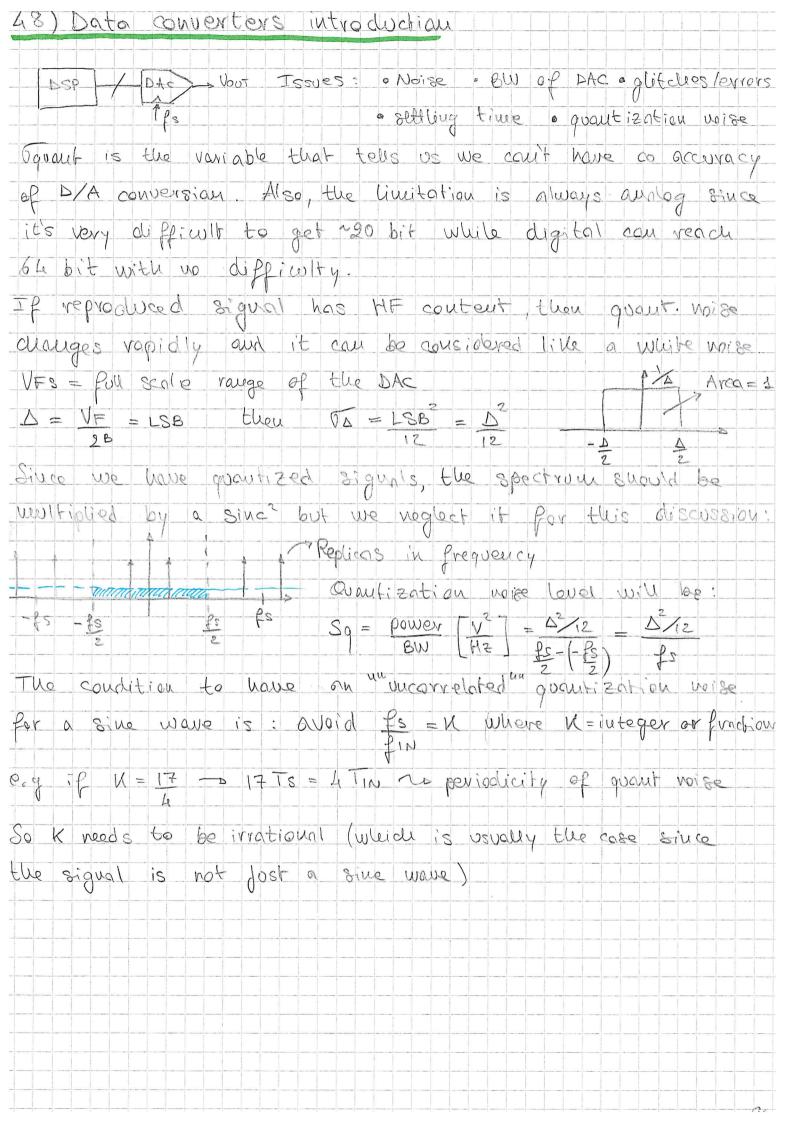

- 49. Data converters: introduction and quantization noise

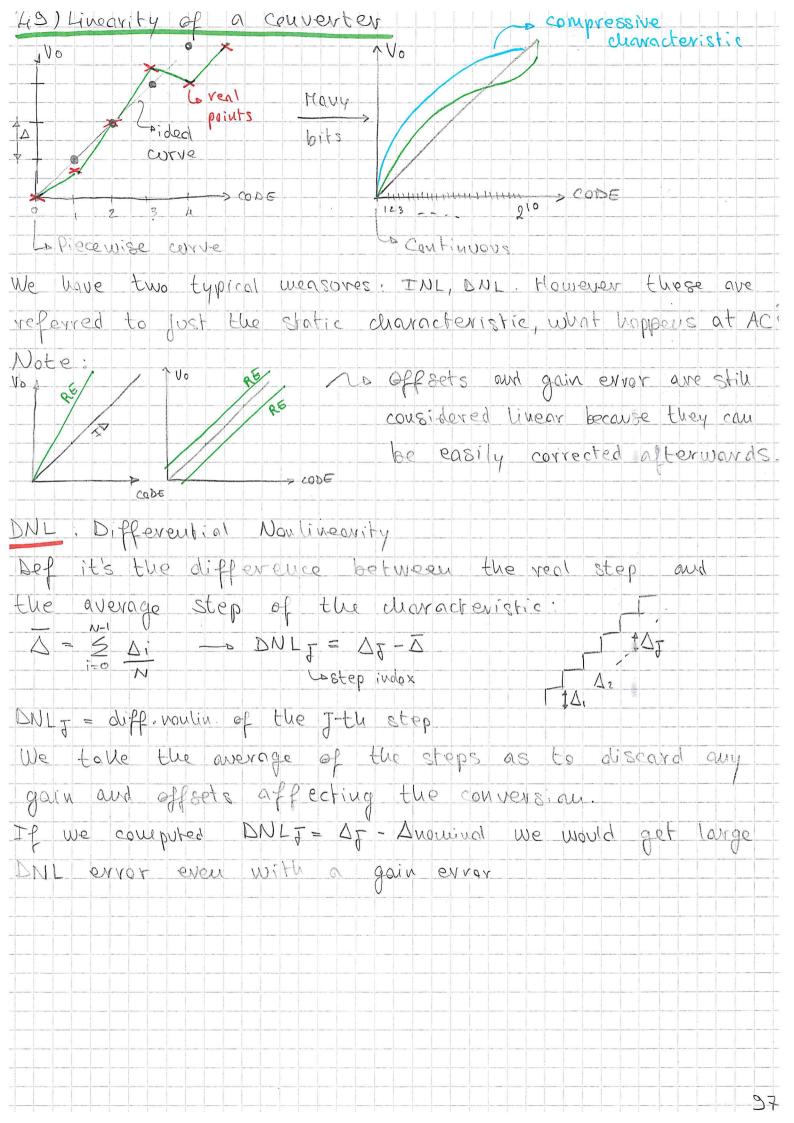

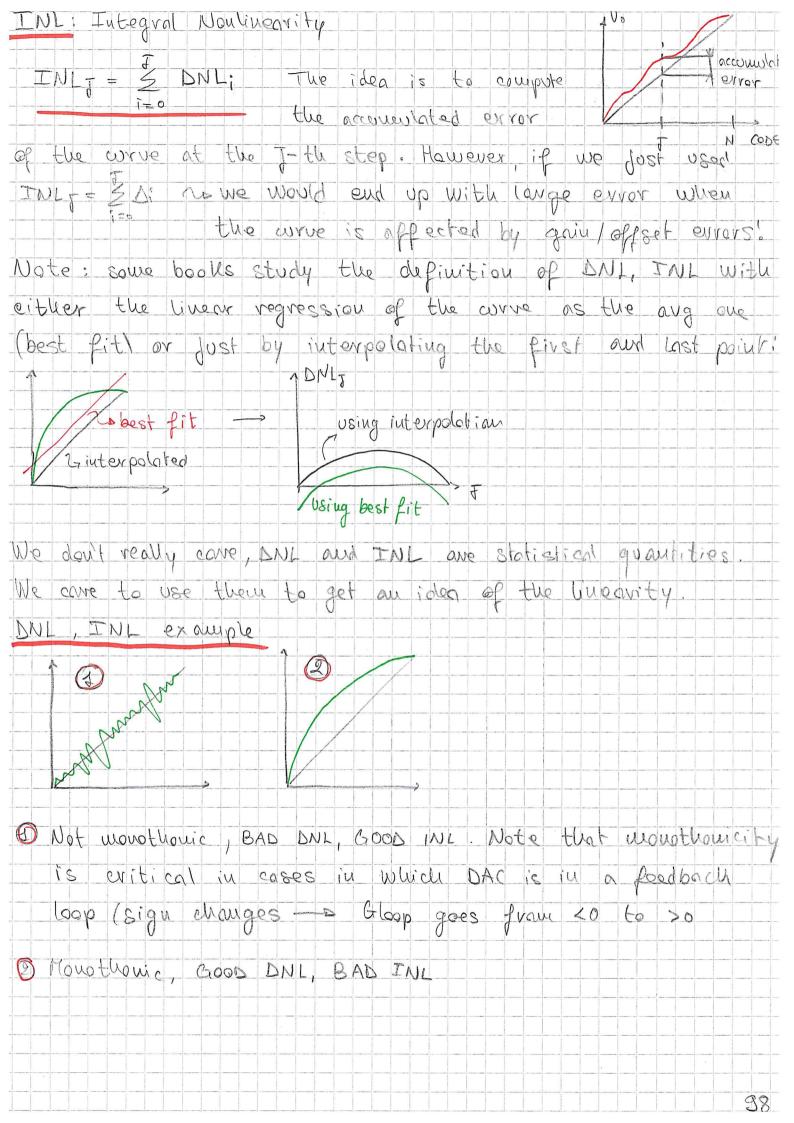

- 50. Linearity of a data converter: INL, DNL

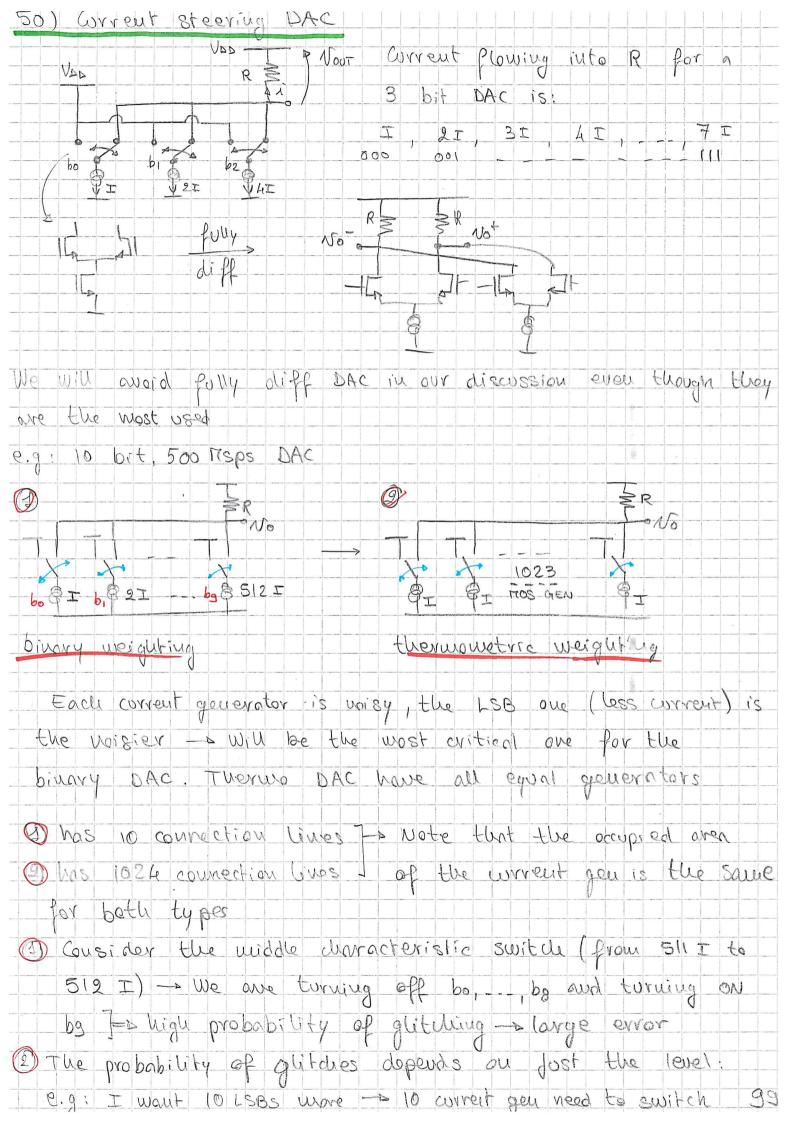

- 51. Current steering DAC

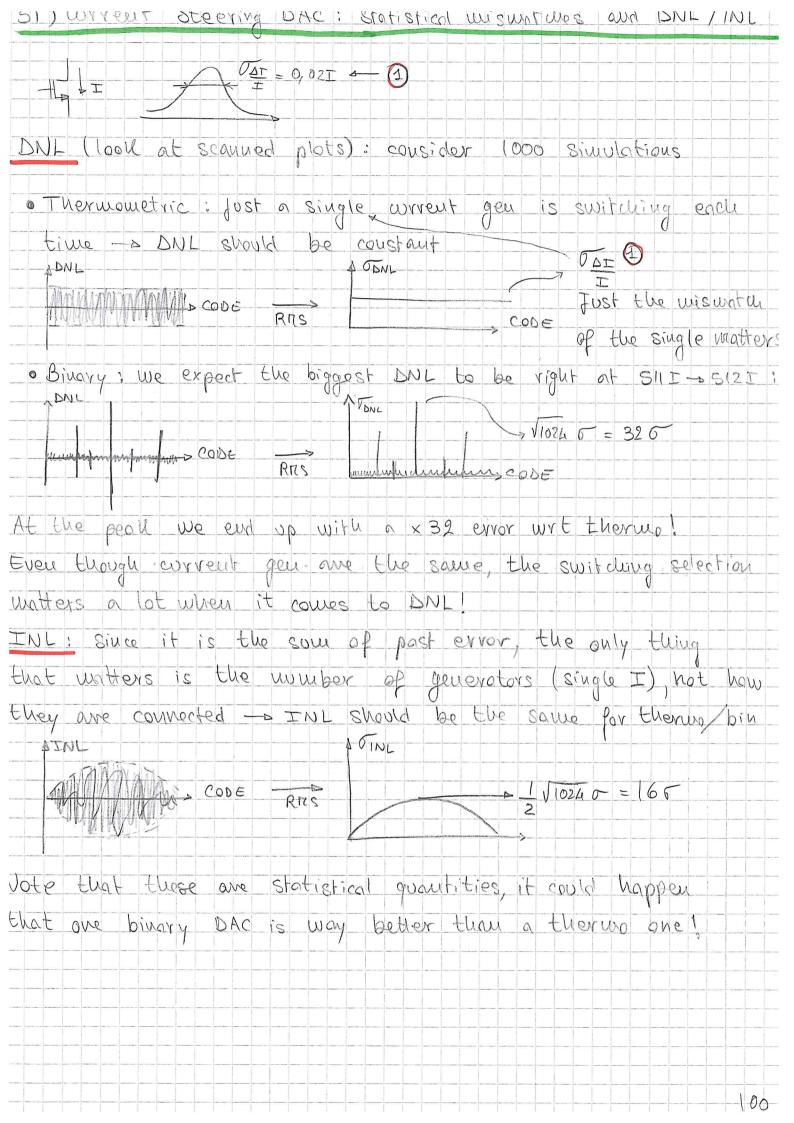

- 52. Current steering DAC DNL and INL

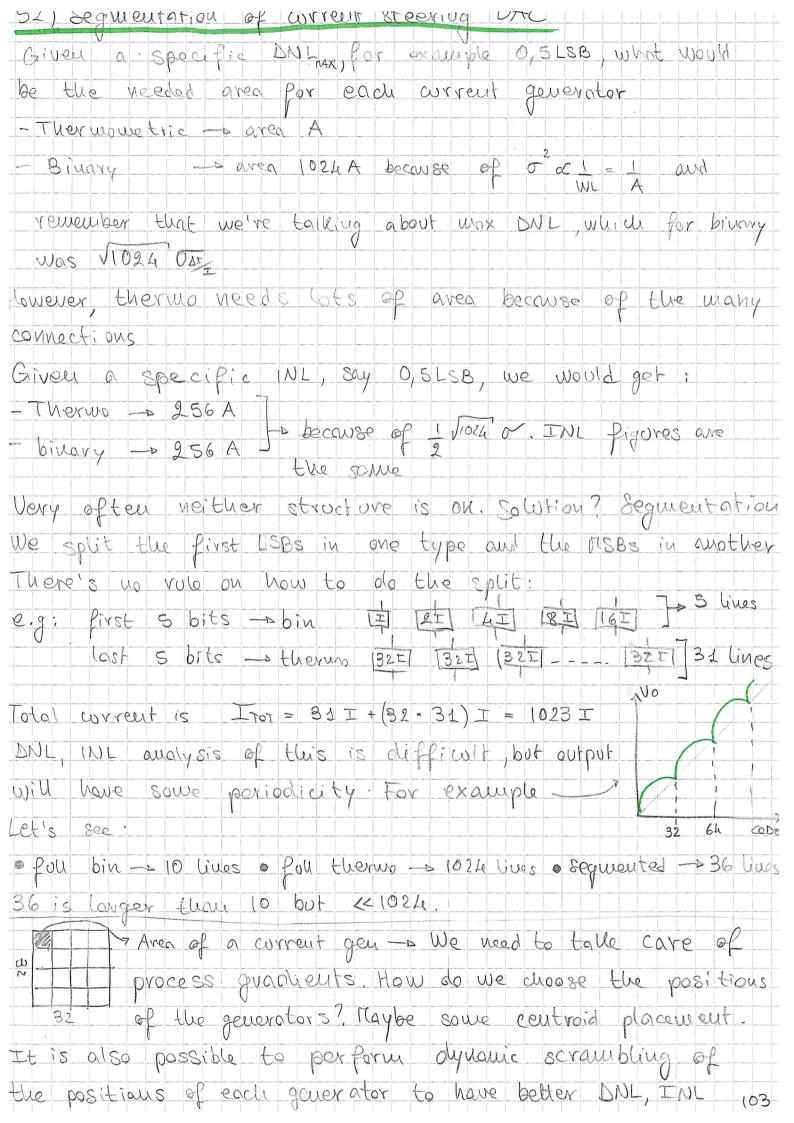

- 53. Segmentation of a current steering DAC

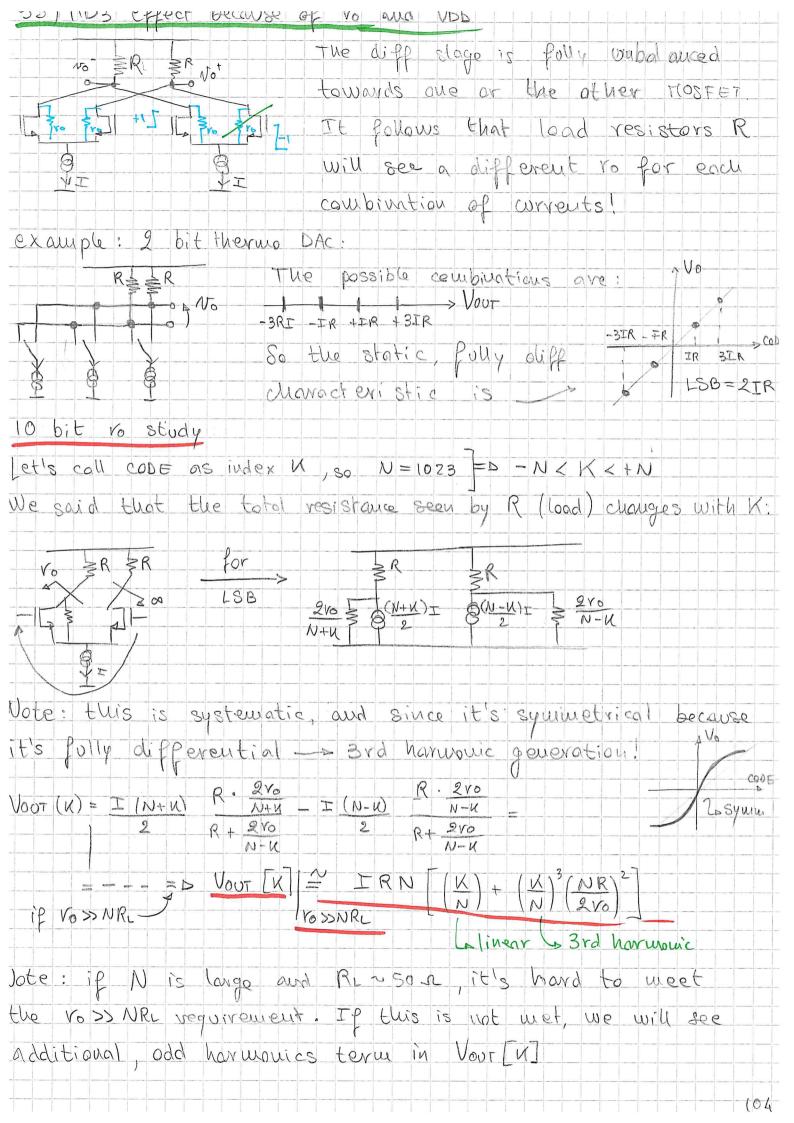

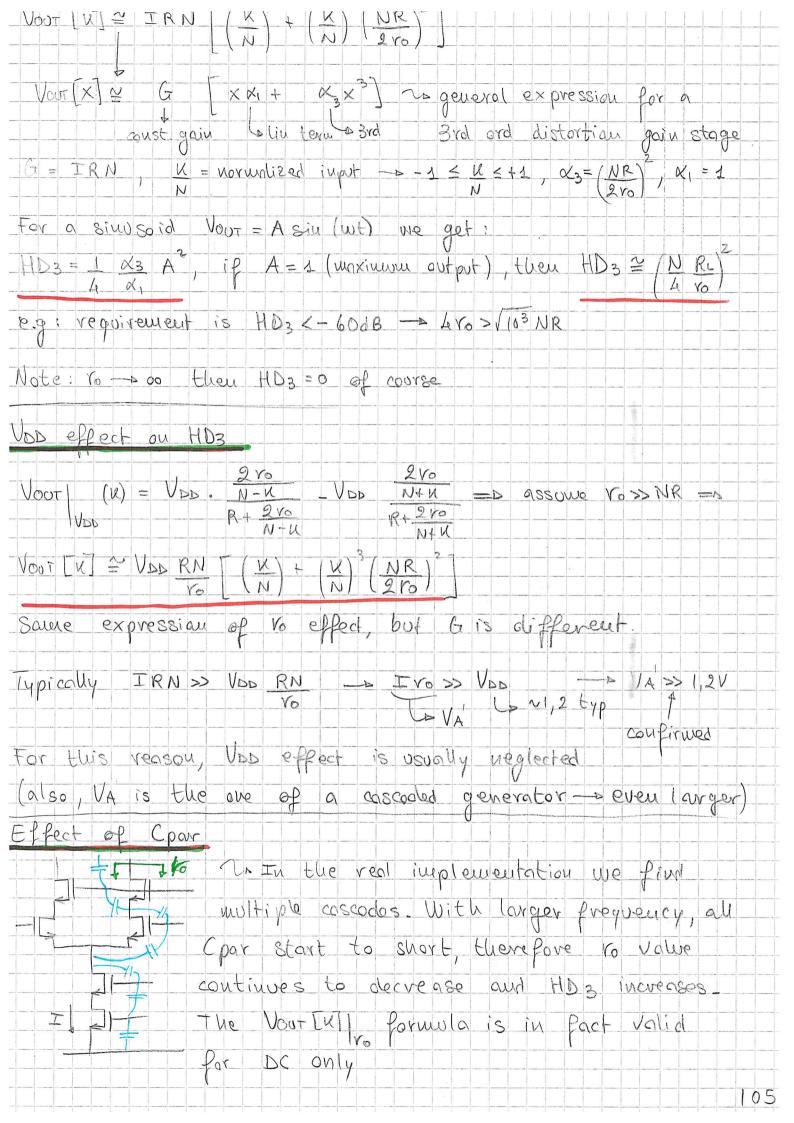

- 54. Third harmonic distortion effect of RO an Vdd on a current steering DAC

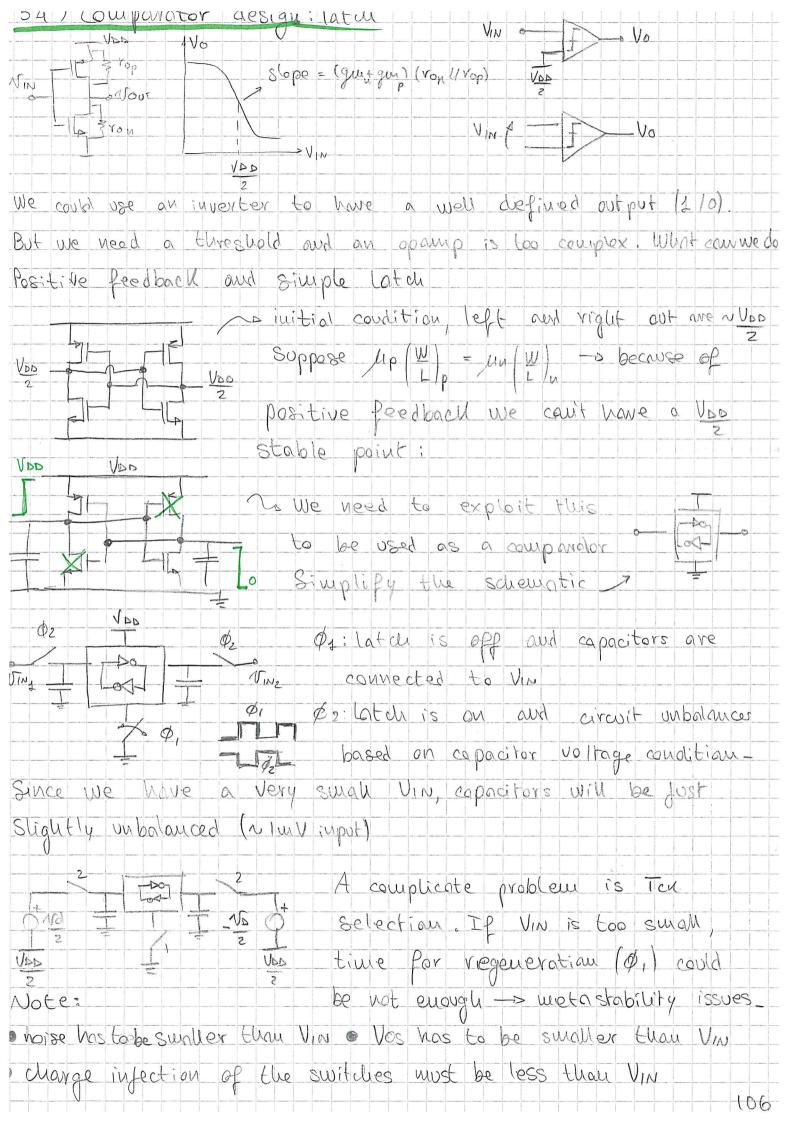

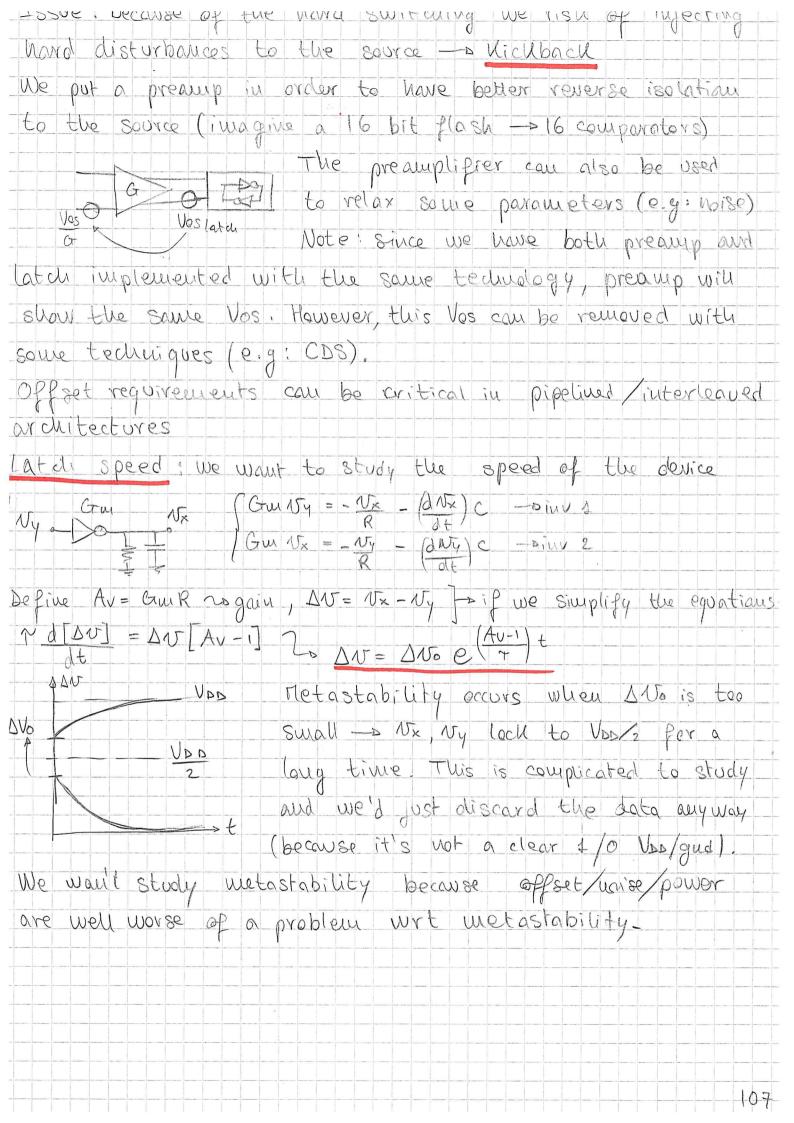

- 55. Latch comparator design

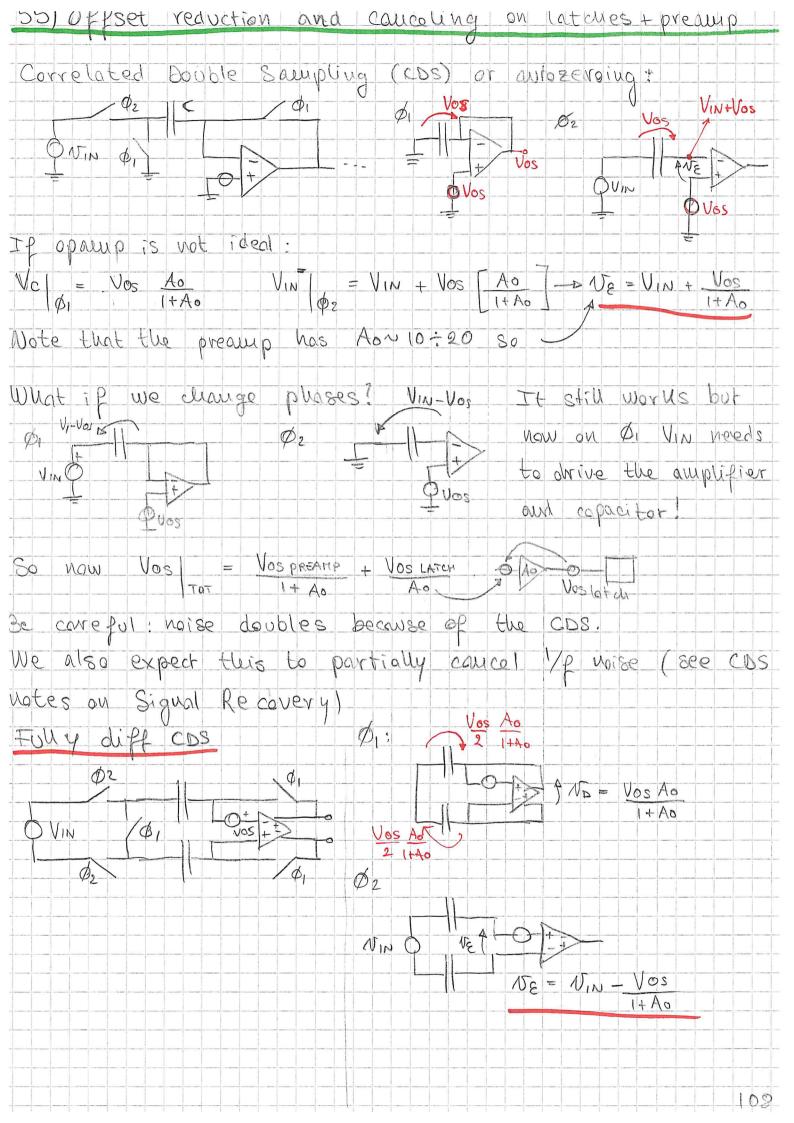

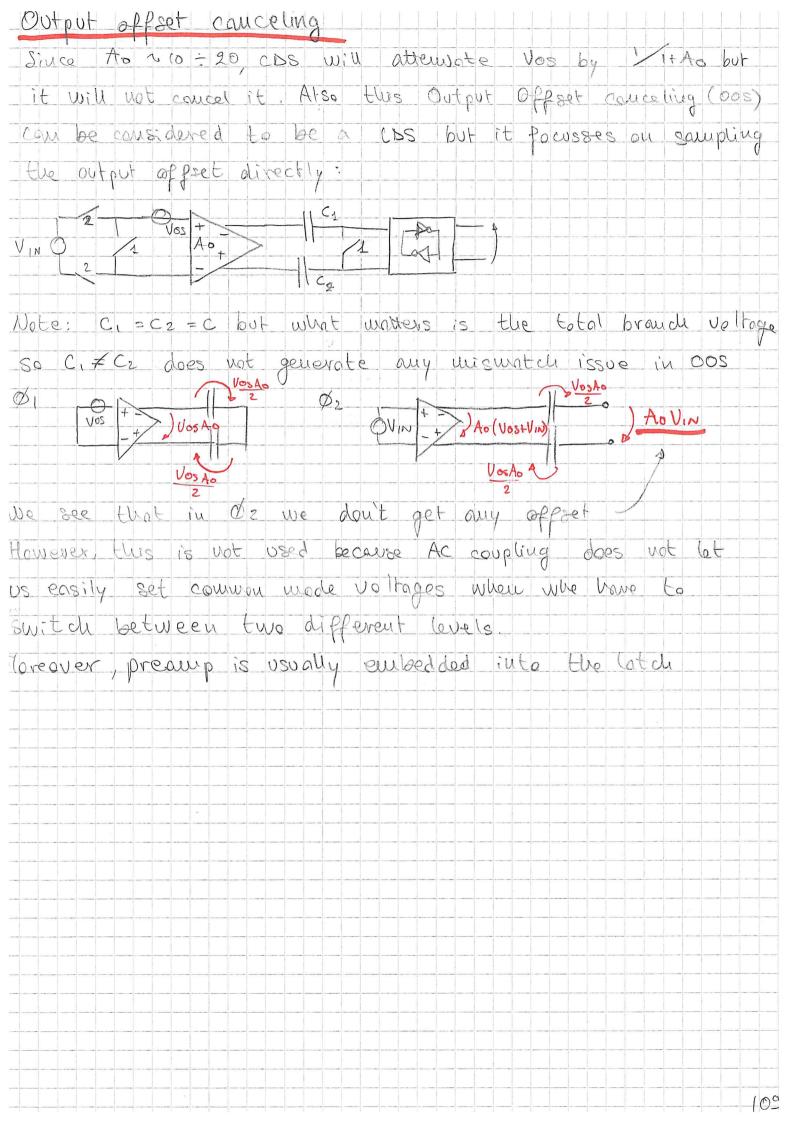

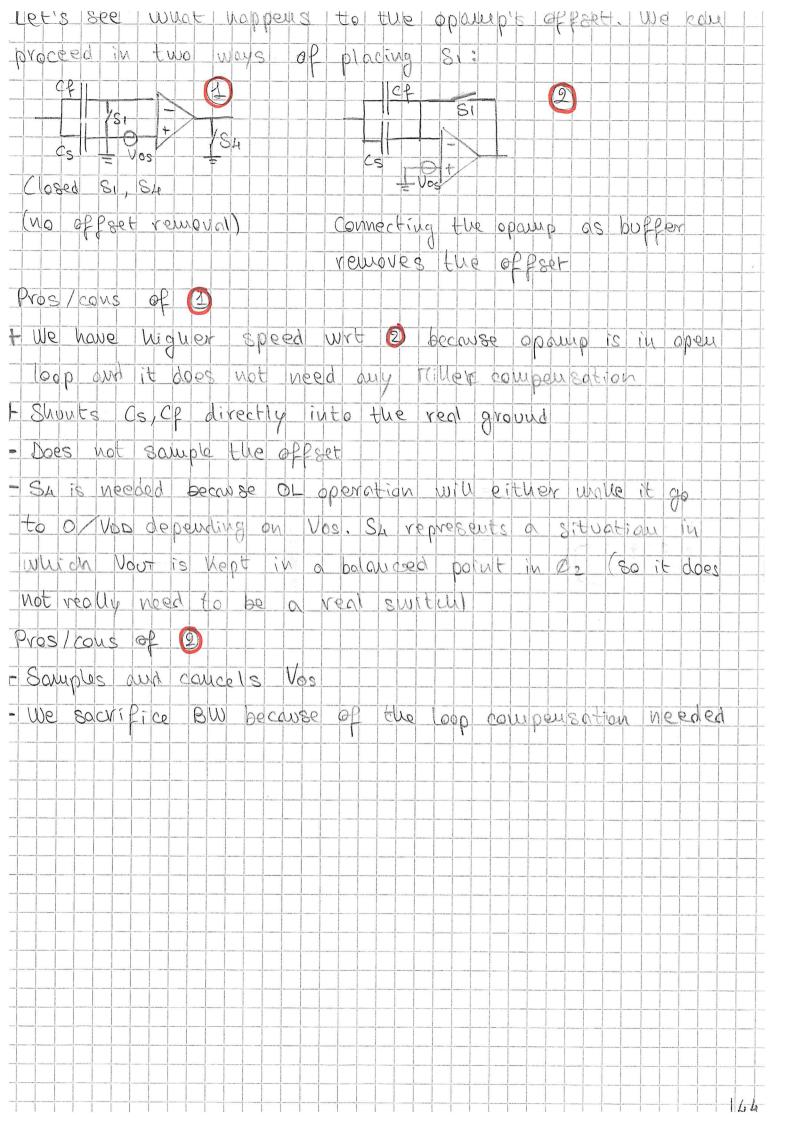

- 56. Correlated Double Sampling and output offset canceling of a comparator

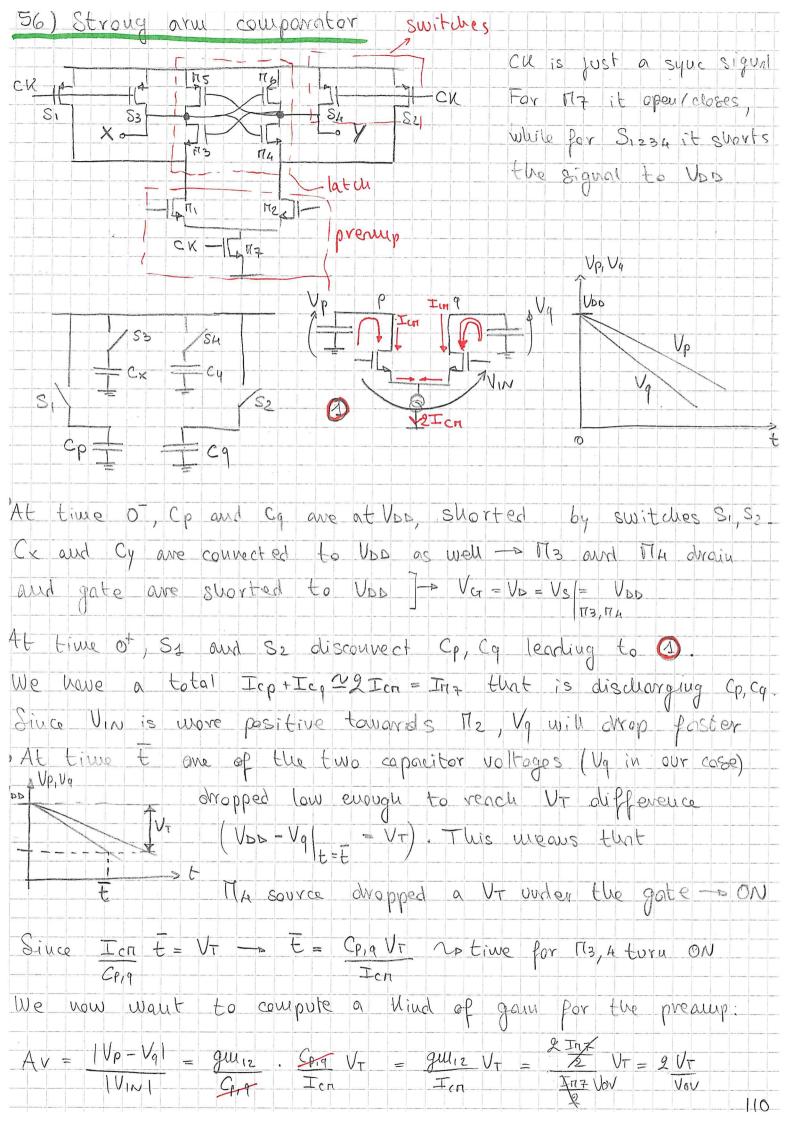

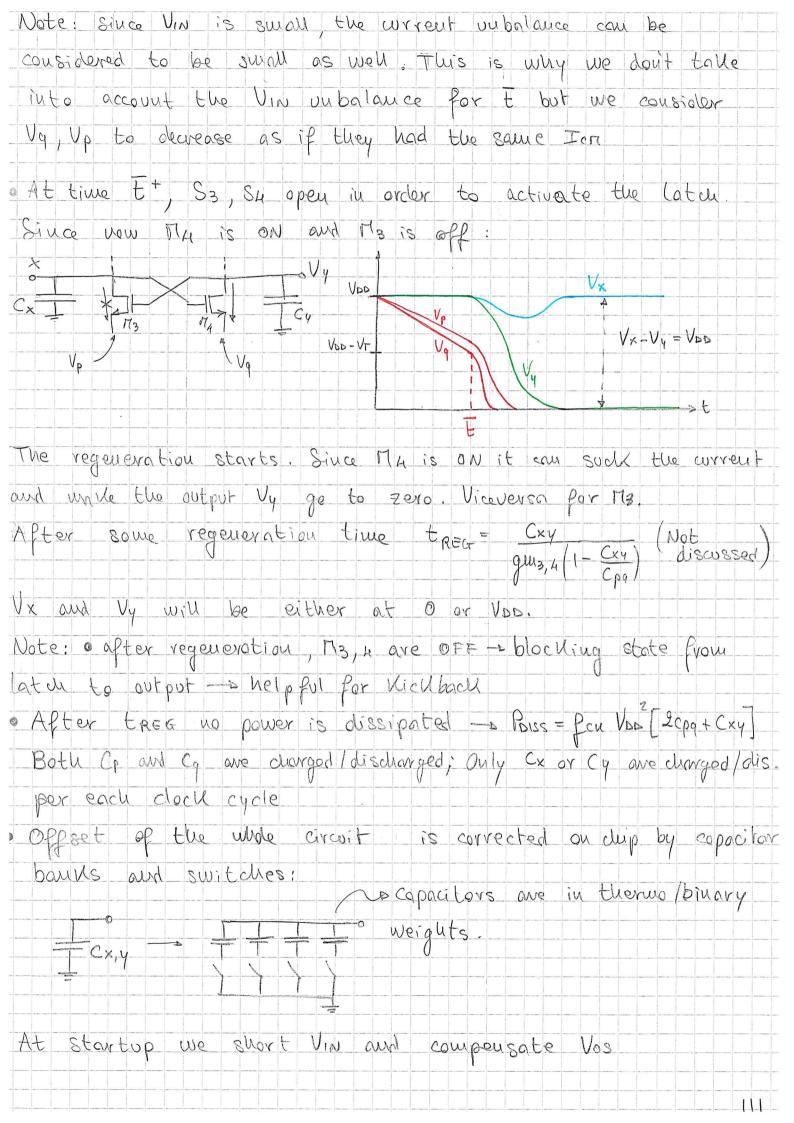

- 57. Strong arm comparator

- 58. Comparator noise

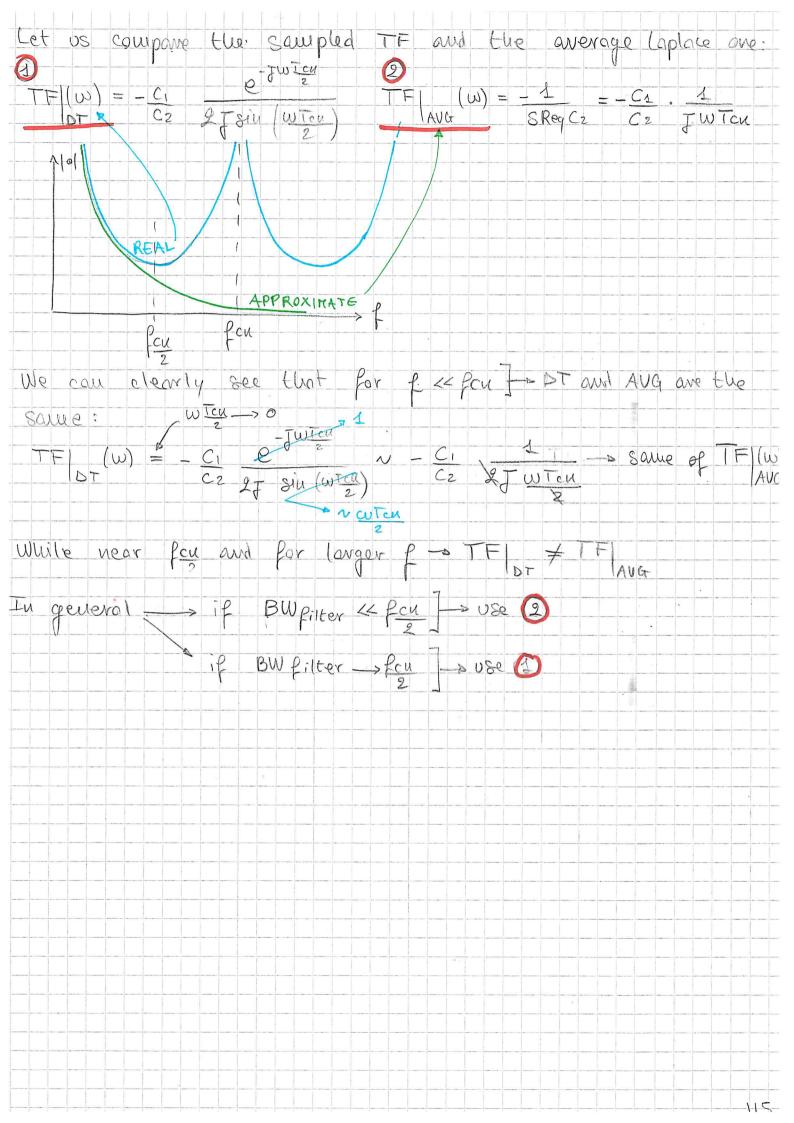

- 59. Recall on switched capacitors

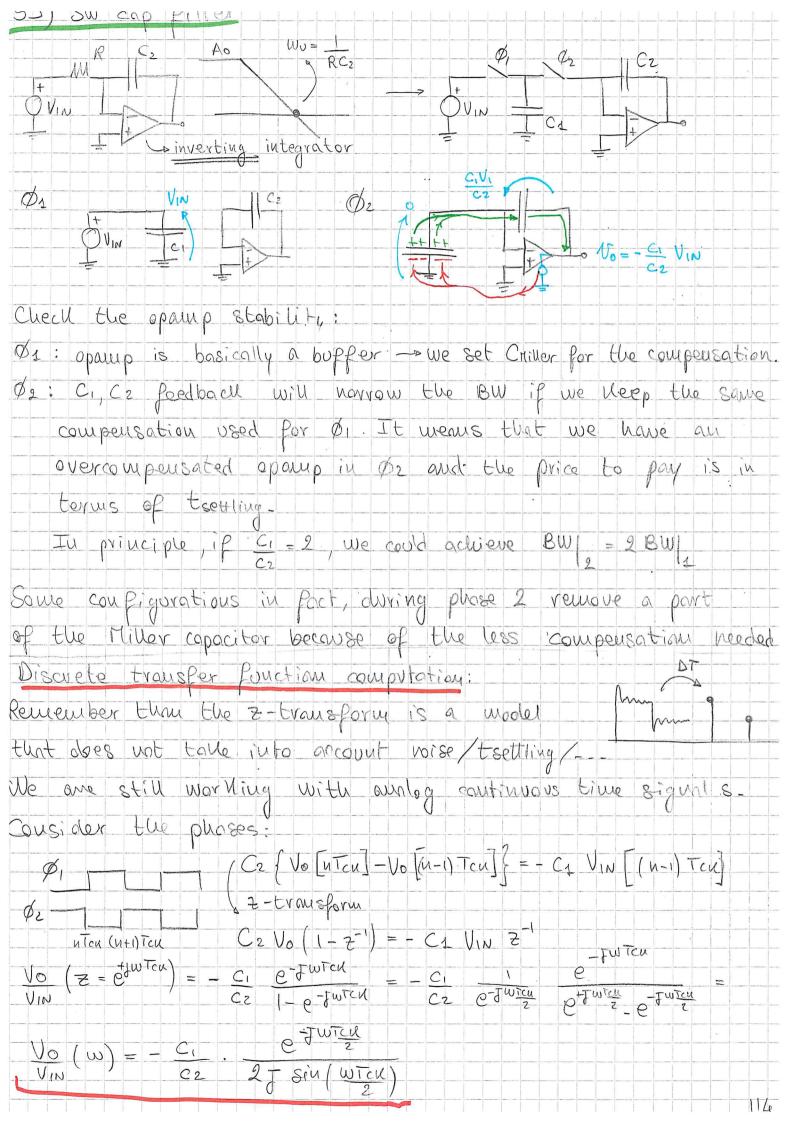

- 60. Switched capacitor filter: transfer function using z-transform

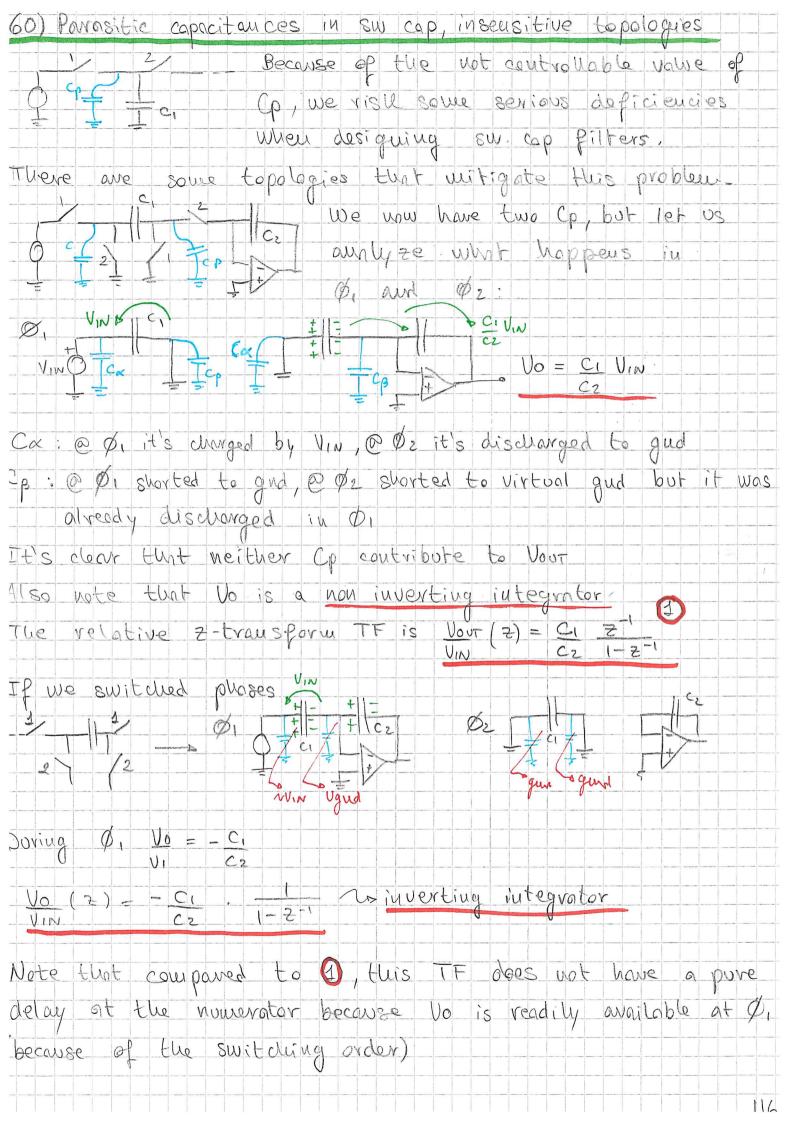

- 61. Parasitic capacitances in a switched capacitor filter and stray insensitive topologies

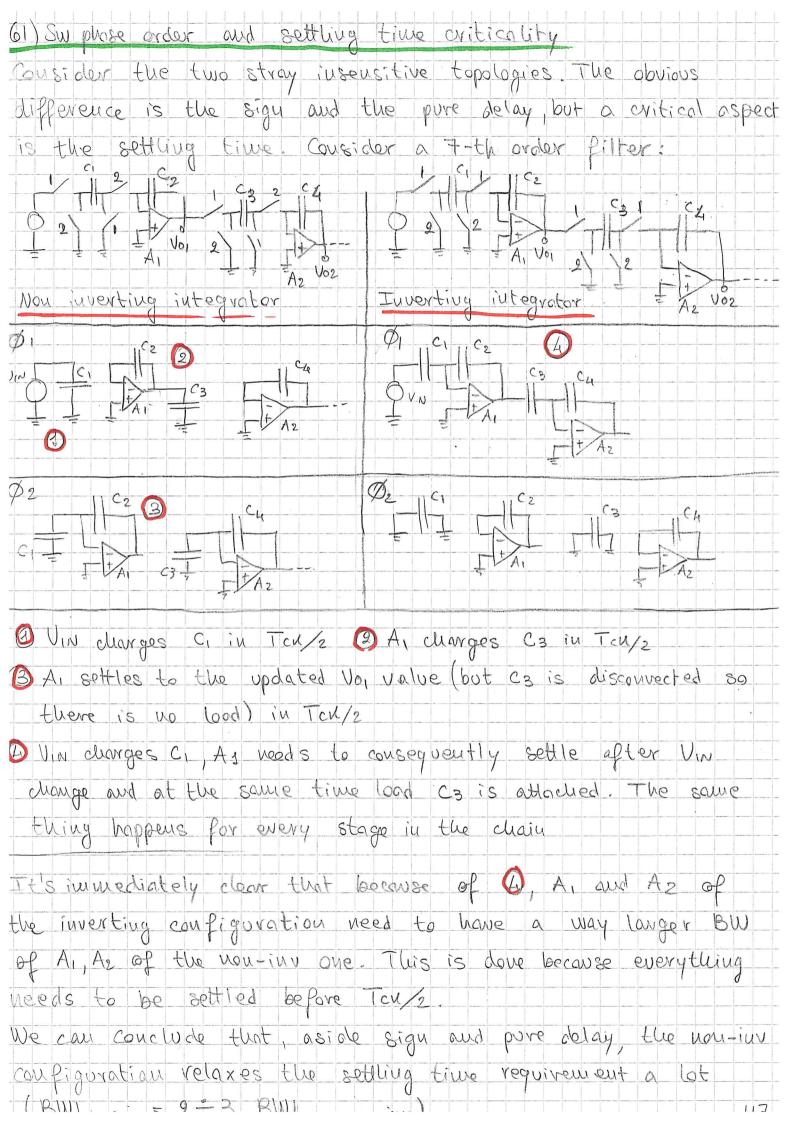

- 62. Switching phase order of stray insensitive topologies and consequences in settling time performance

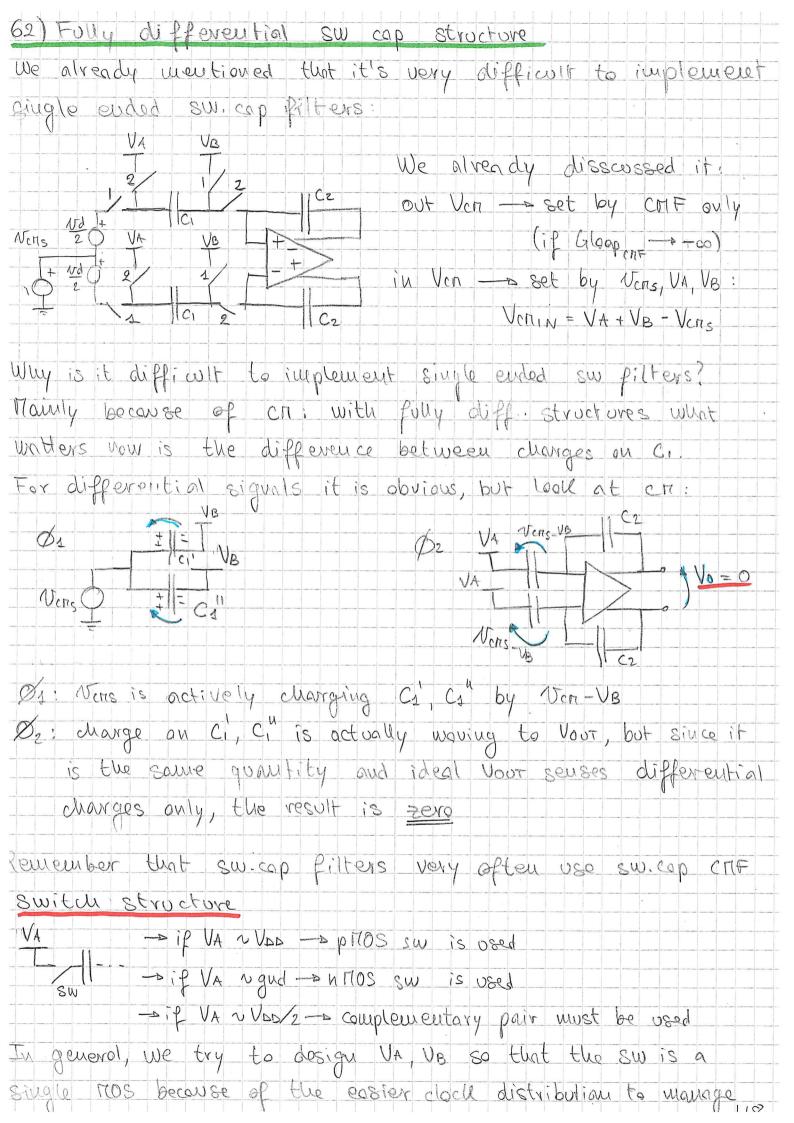

- 63. Fully differential switch capacitor structure

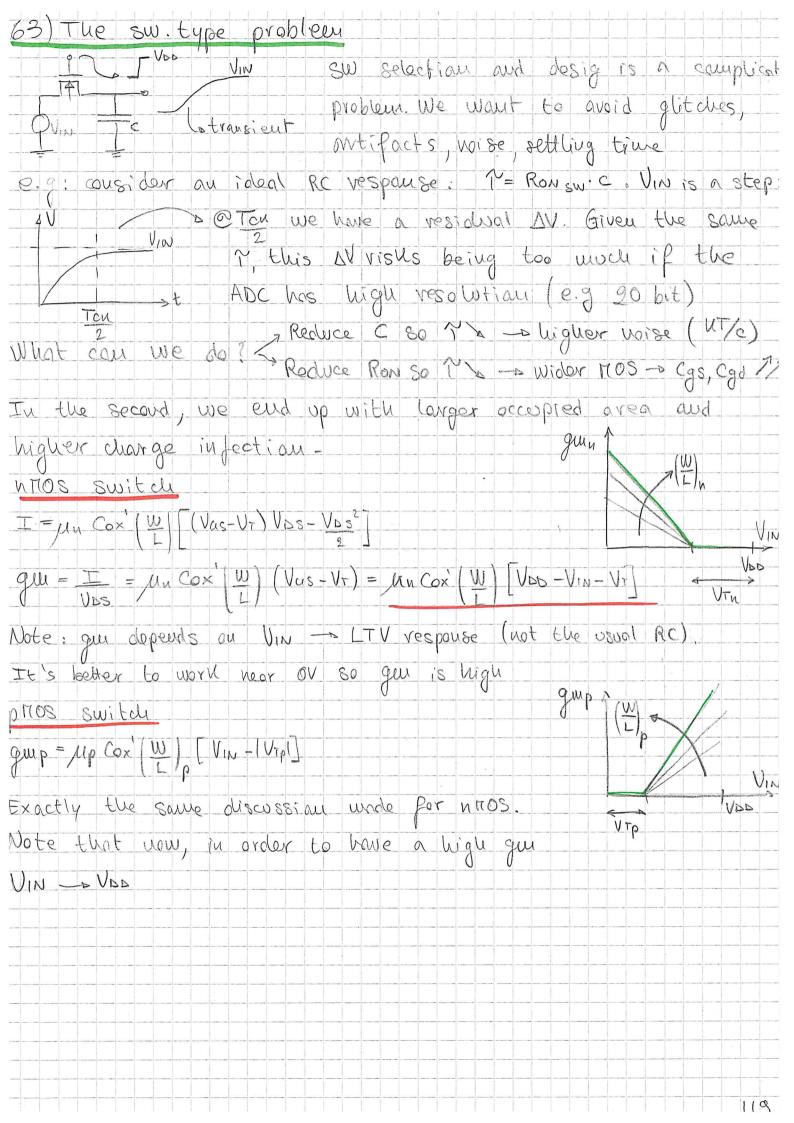

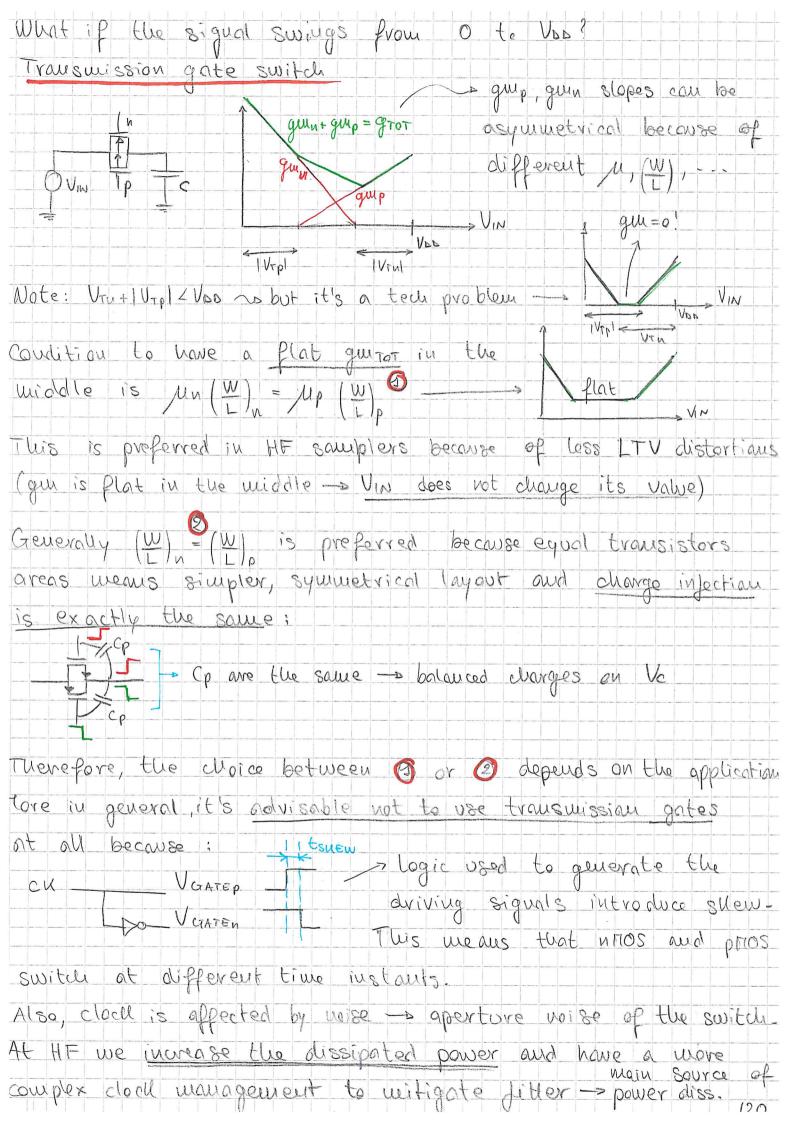

- 64. Switch type selection problem

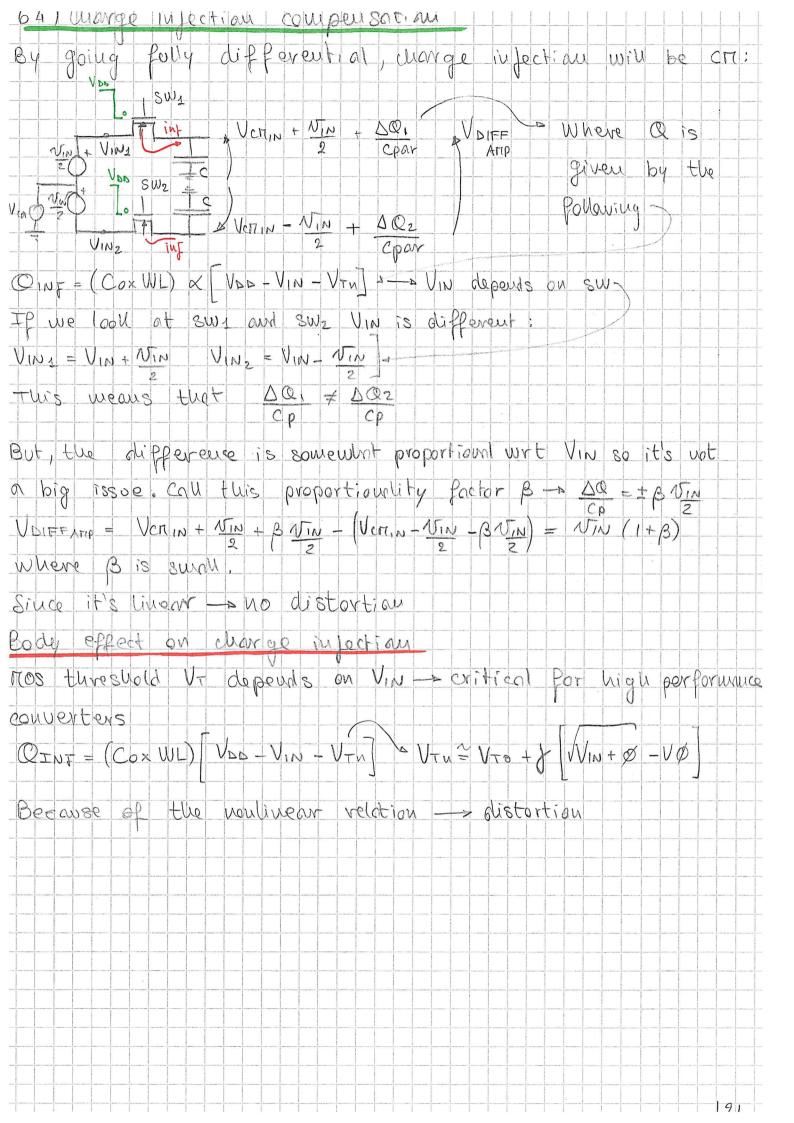

- 65. Charge injection compensation of switched capacitors using fully differential structures

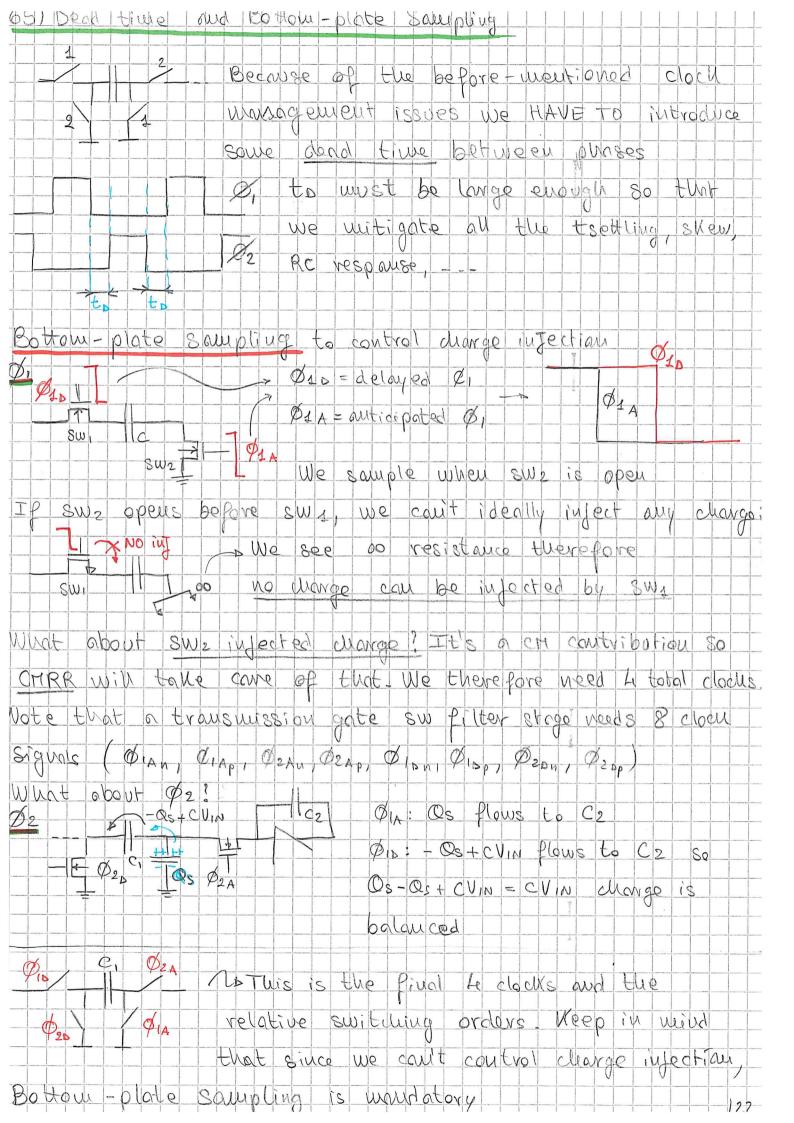

- 66. Dead time and bottom plate sampling

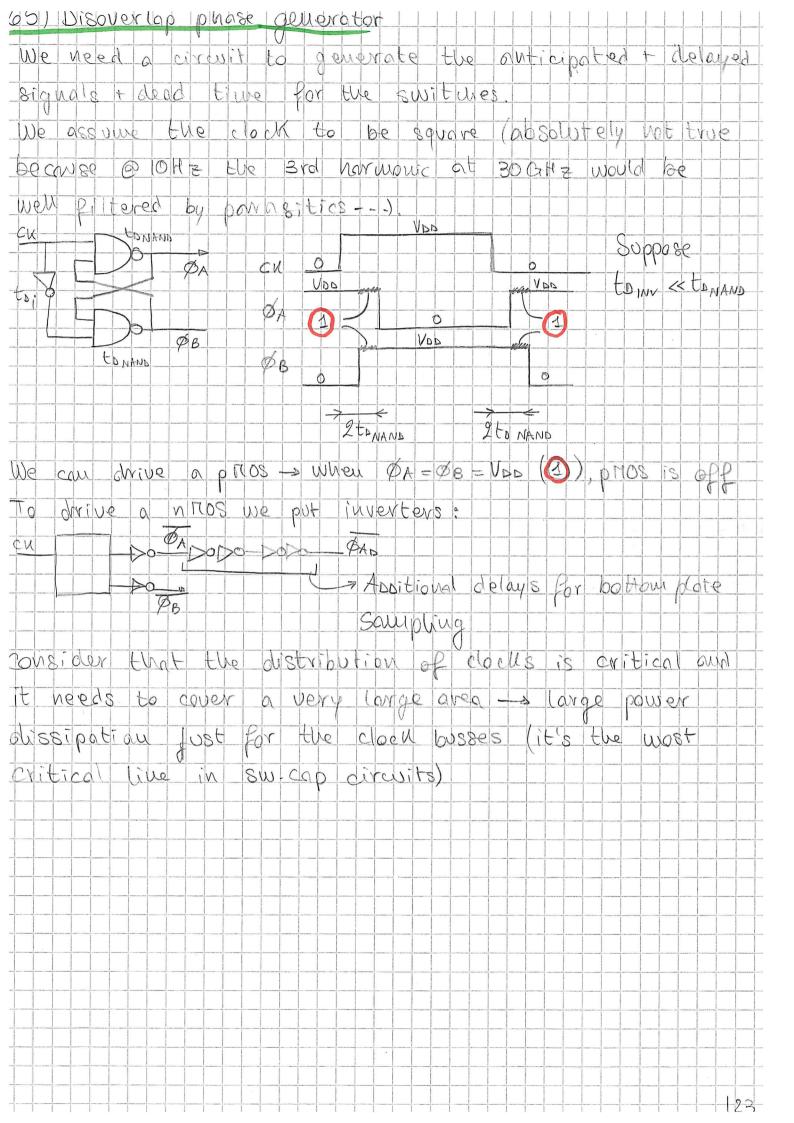

- 67. Disoverlap generator for dead time and phase order for bottom plate sampling

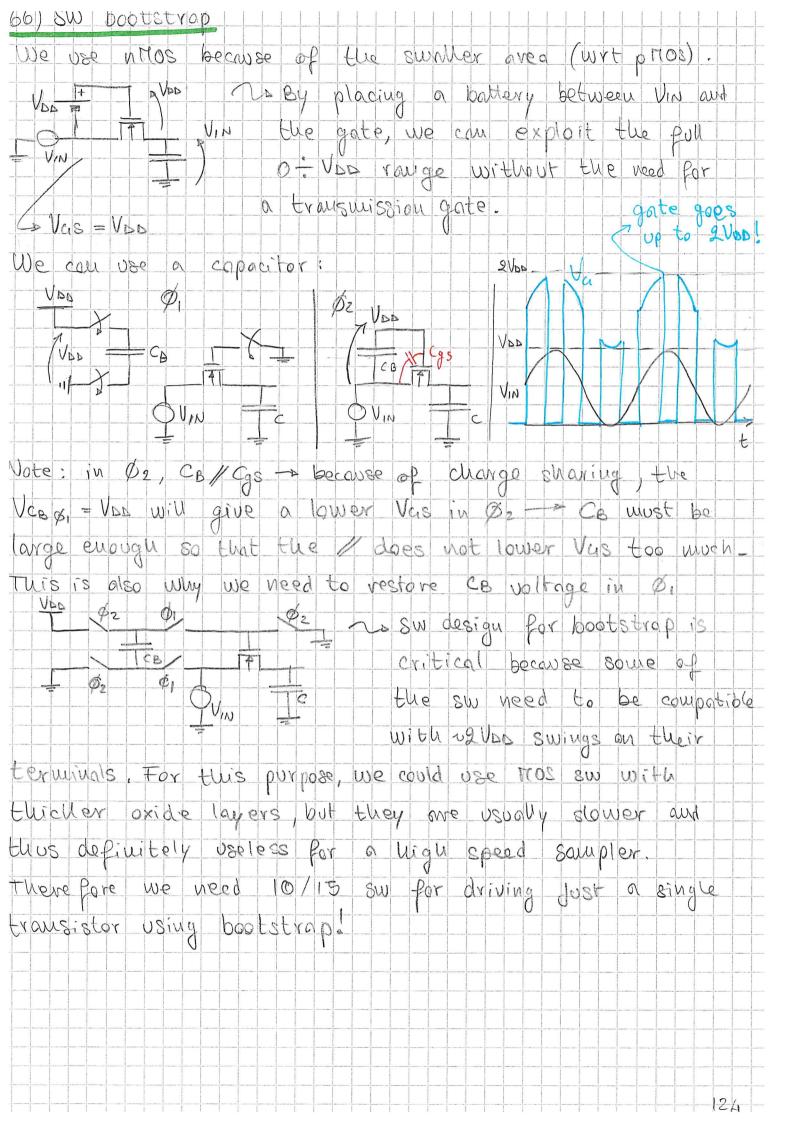

- 68. Bootstrap on a switch

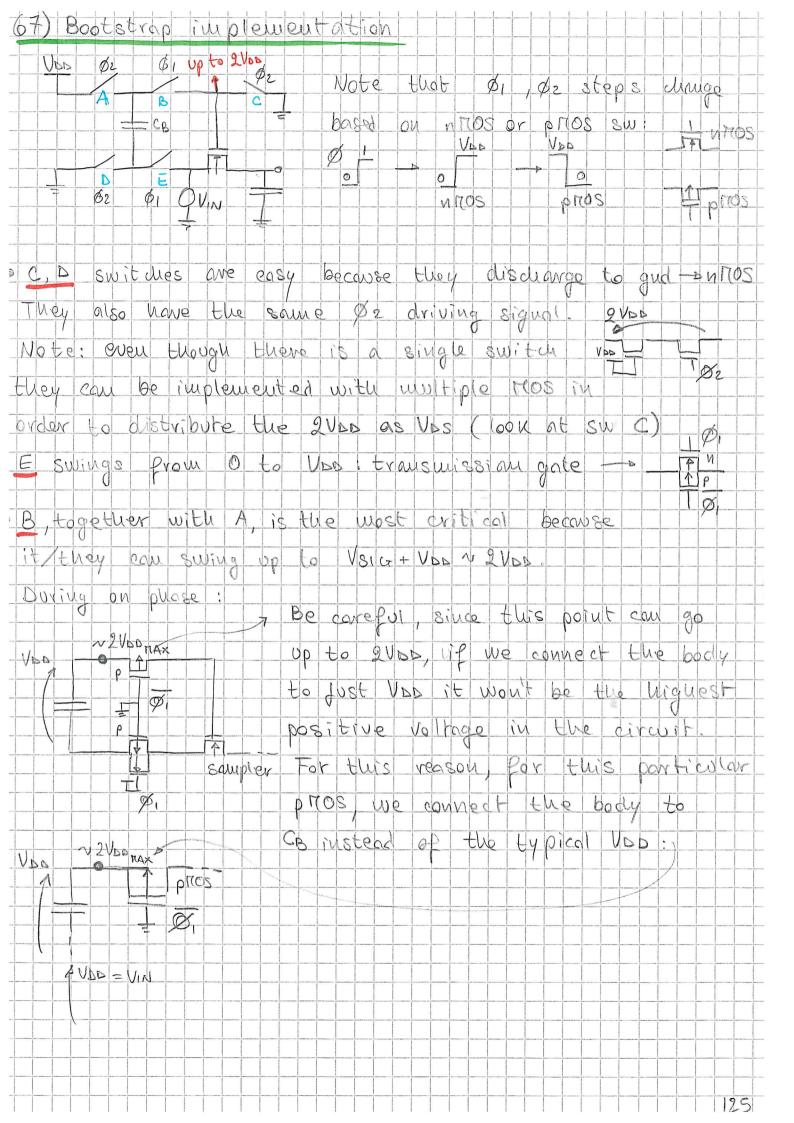

- 69. Bootstrap implementation

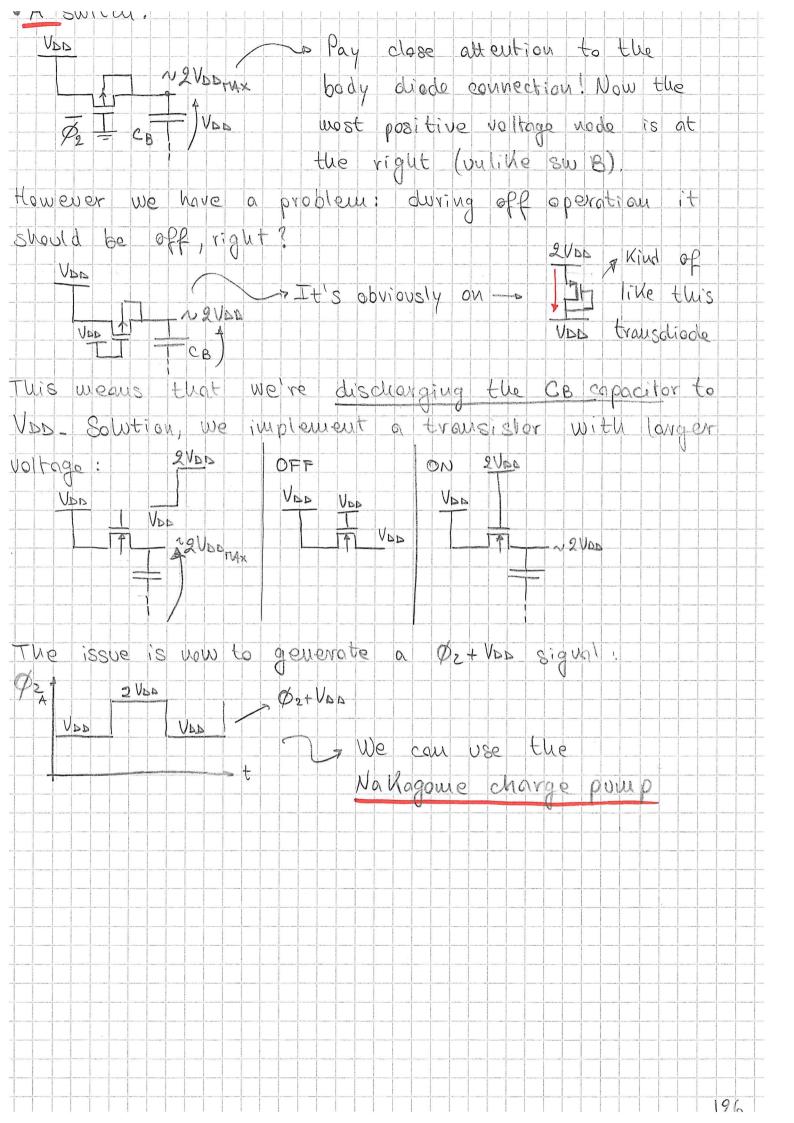

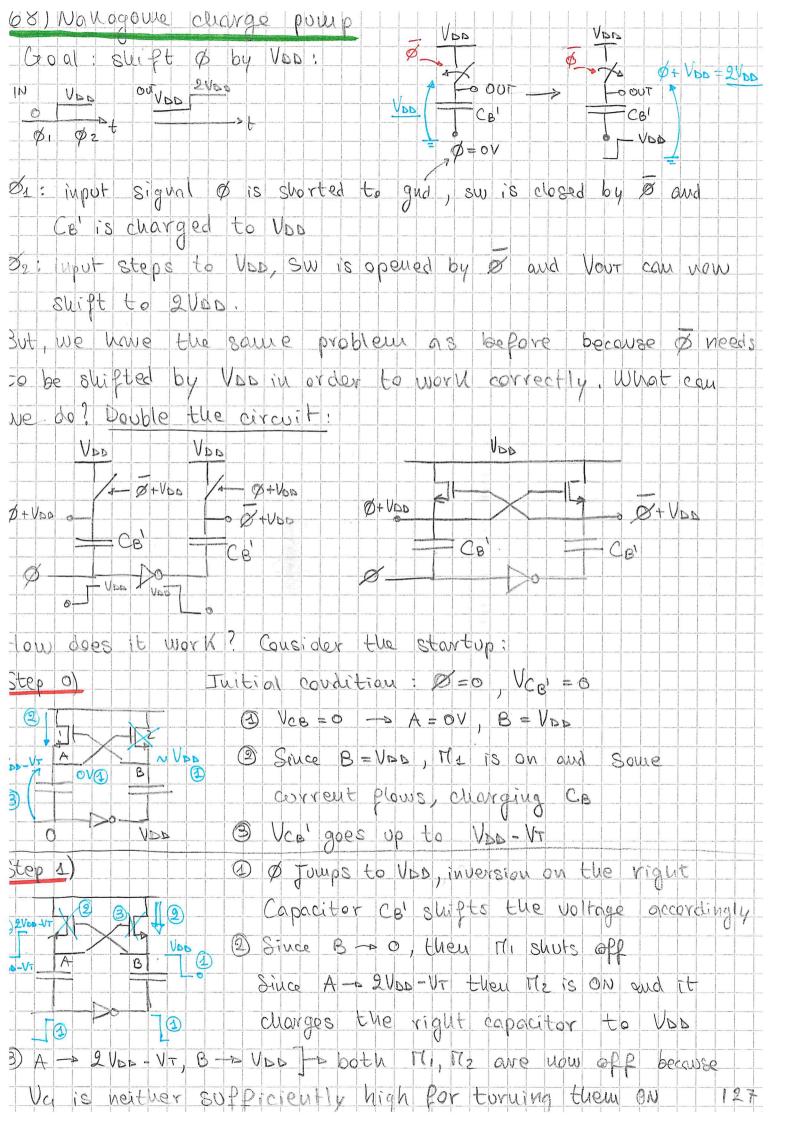

- 70. Nakagome charge pump

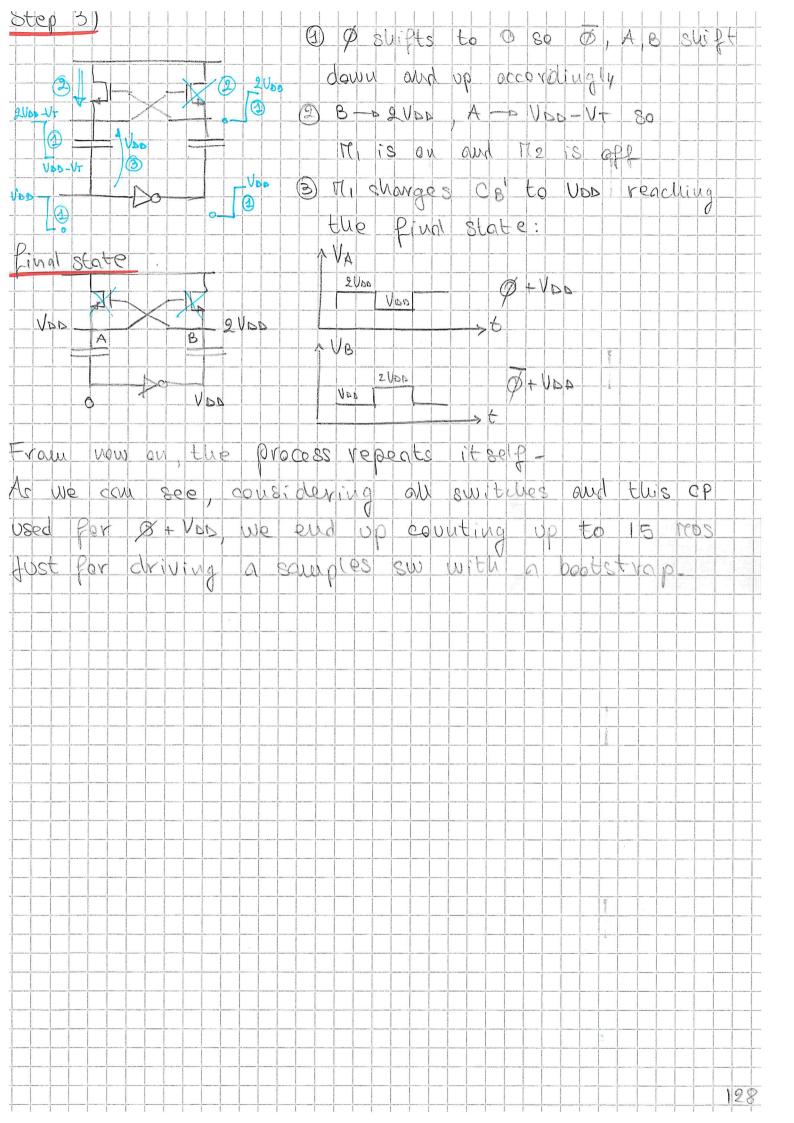

- 71. Sampled noise: SNR computation, aperture/jitter noise

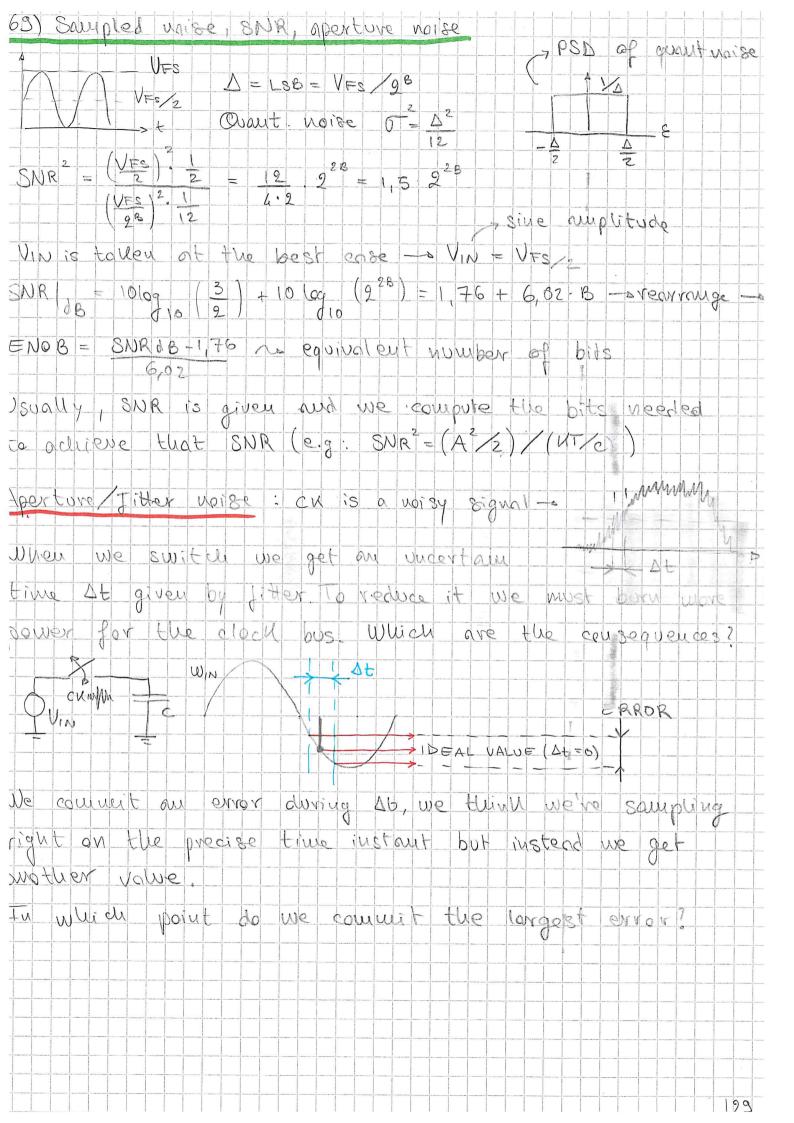

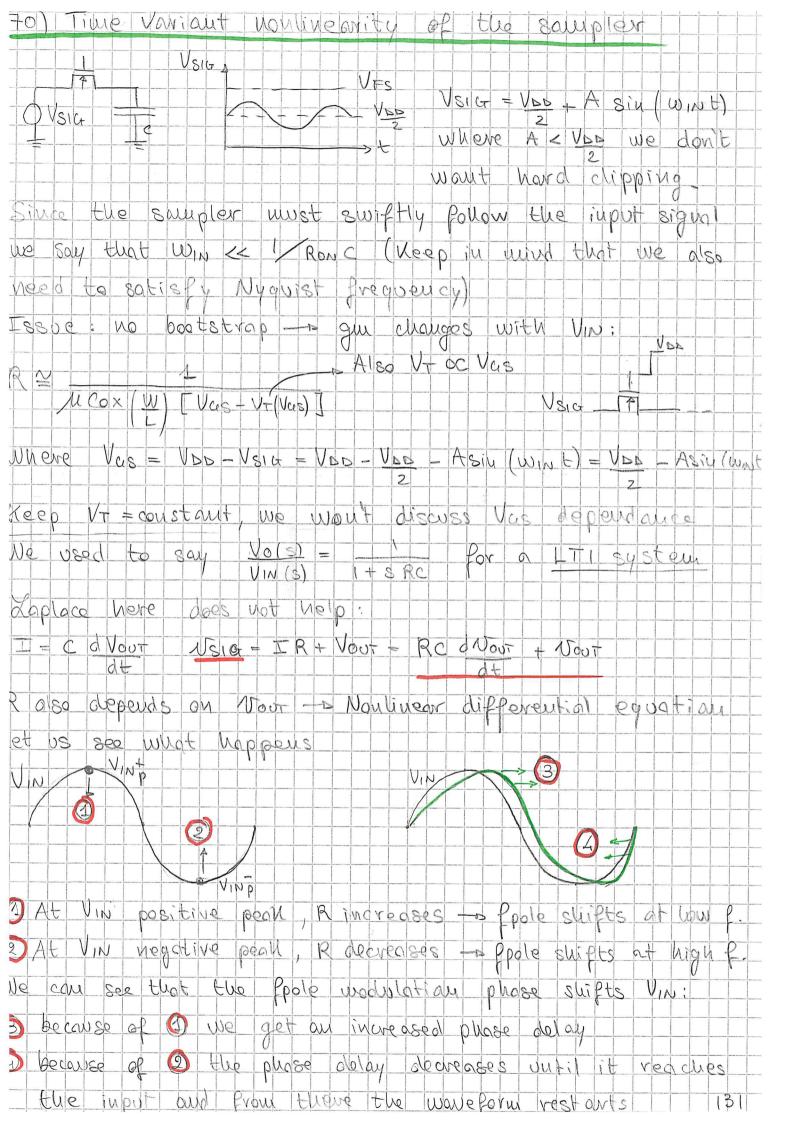

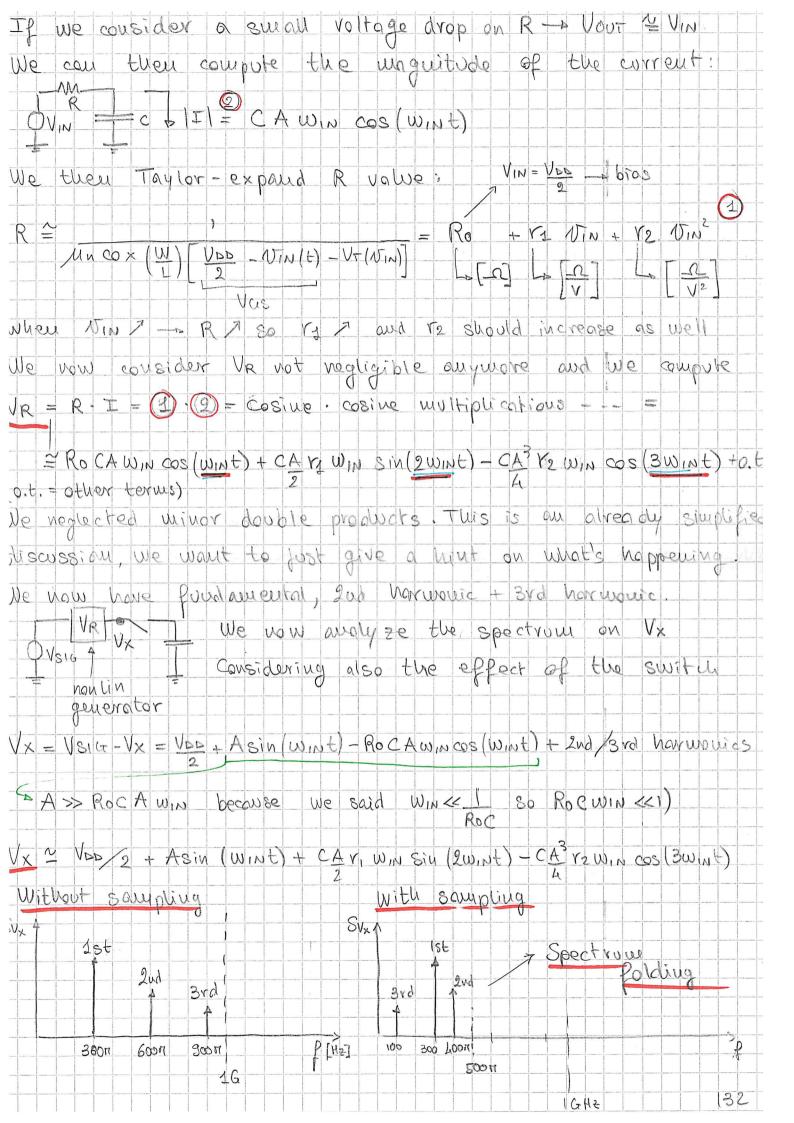

- 72. Time variant nonlinearity of a sampler distortion analysis

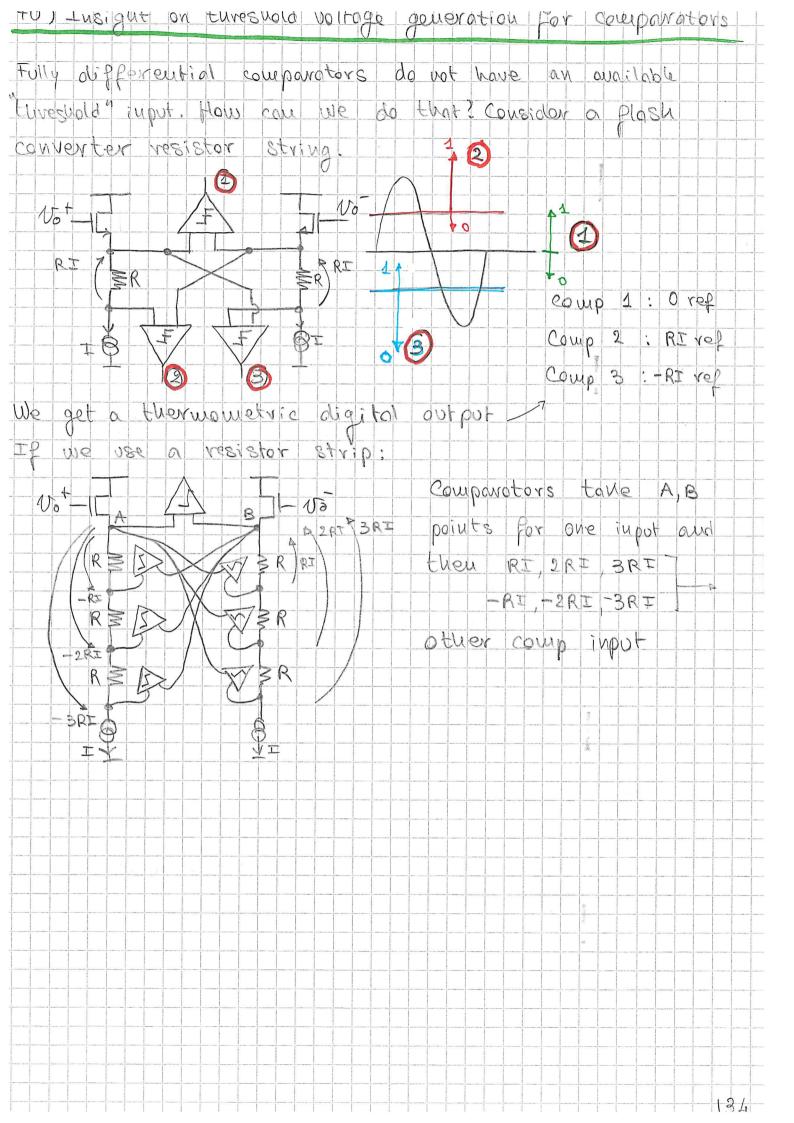

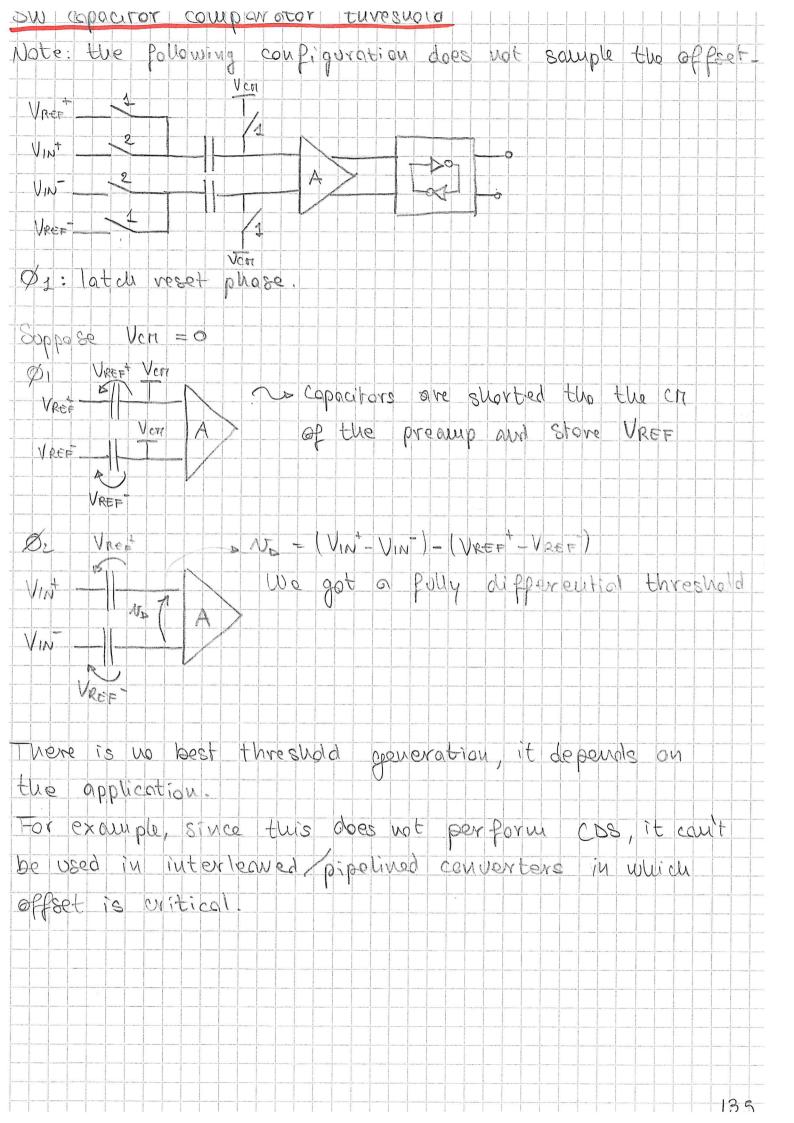

- 73. Insight on generating threshold voltages for fully differential structures: resistor strip and switched capacitor circuits

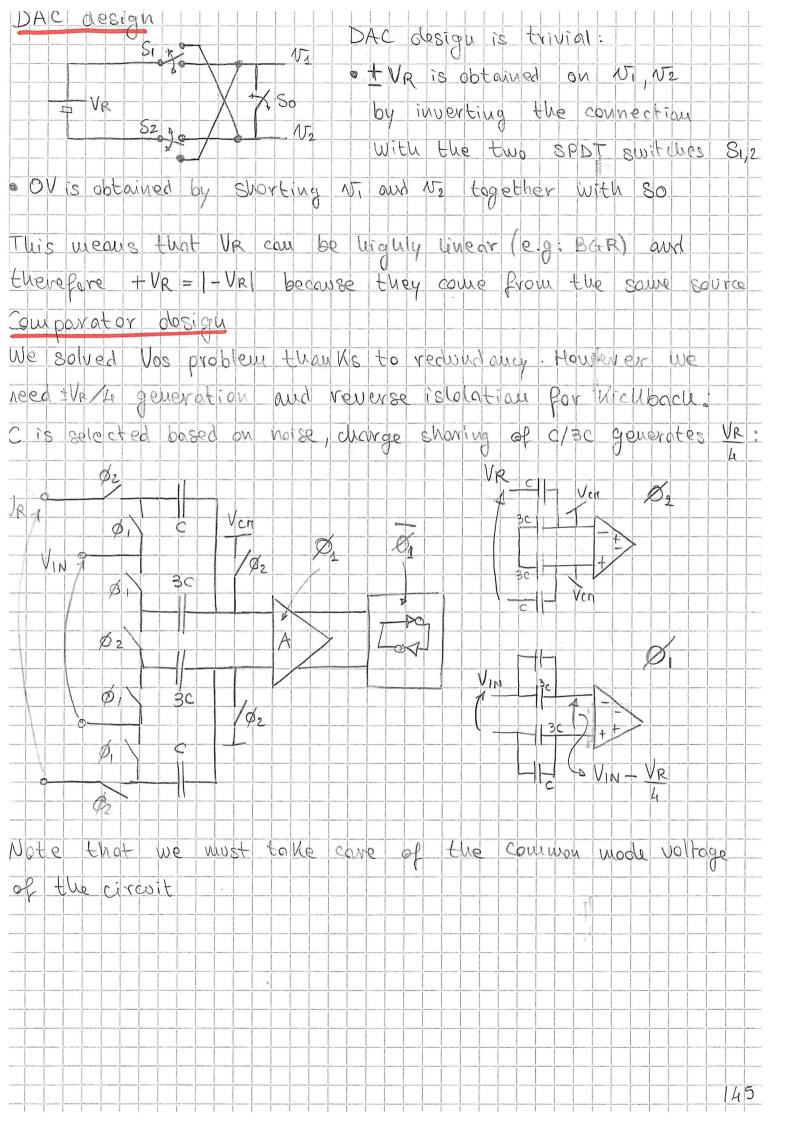

- 74. Pipelined Analog to Digital Converters

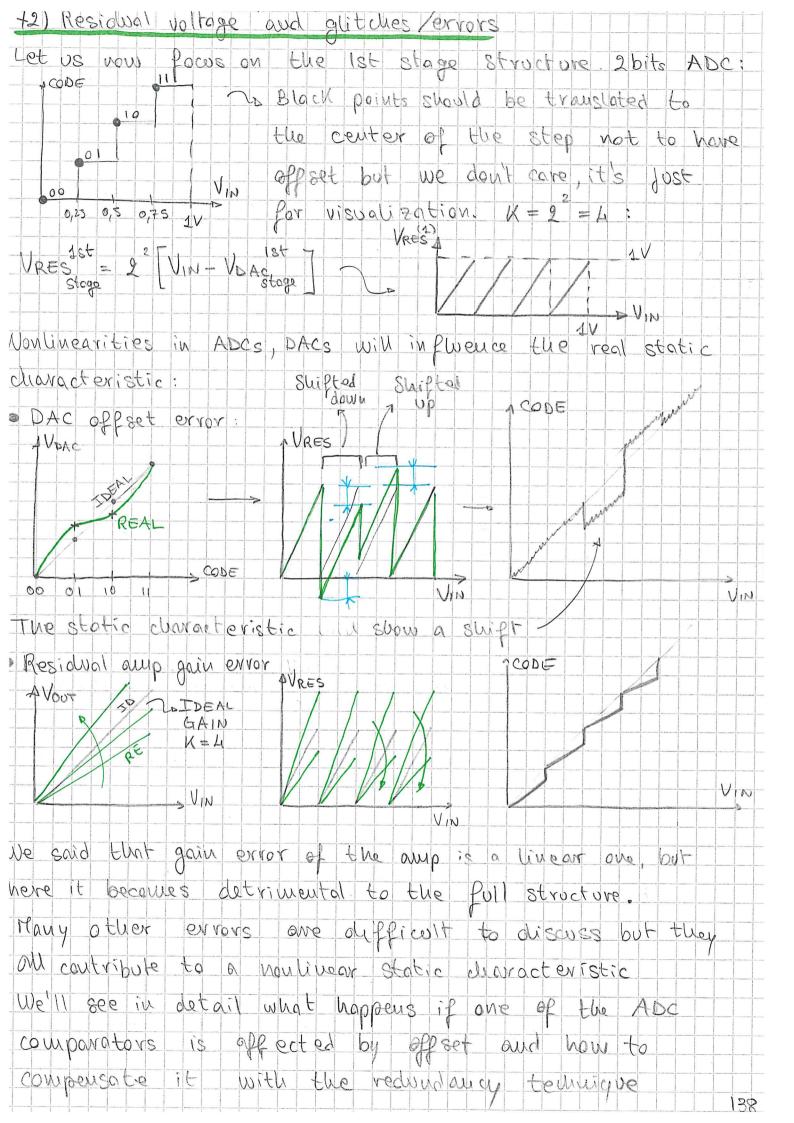

- 75. Residual voltage of a pipelined ADC and effects on static characteristic due to nonlinearities of internal components

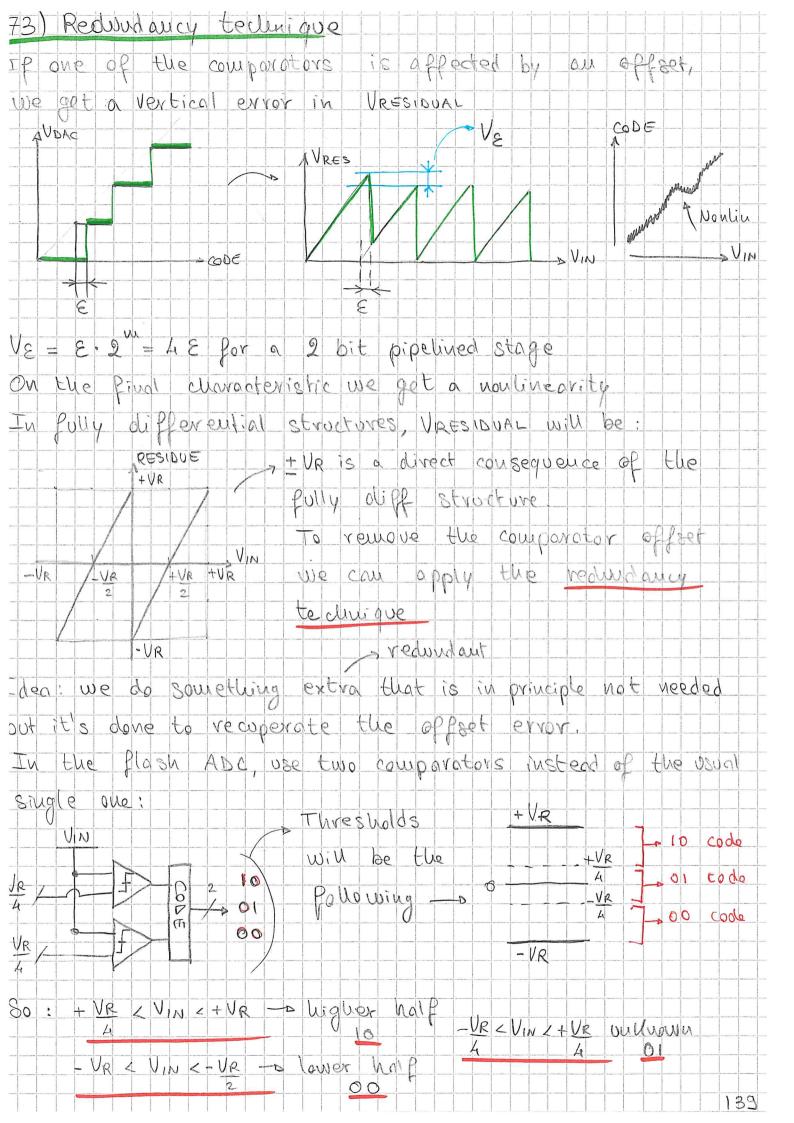

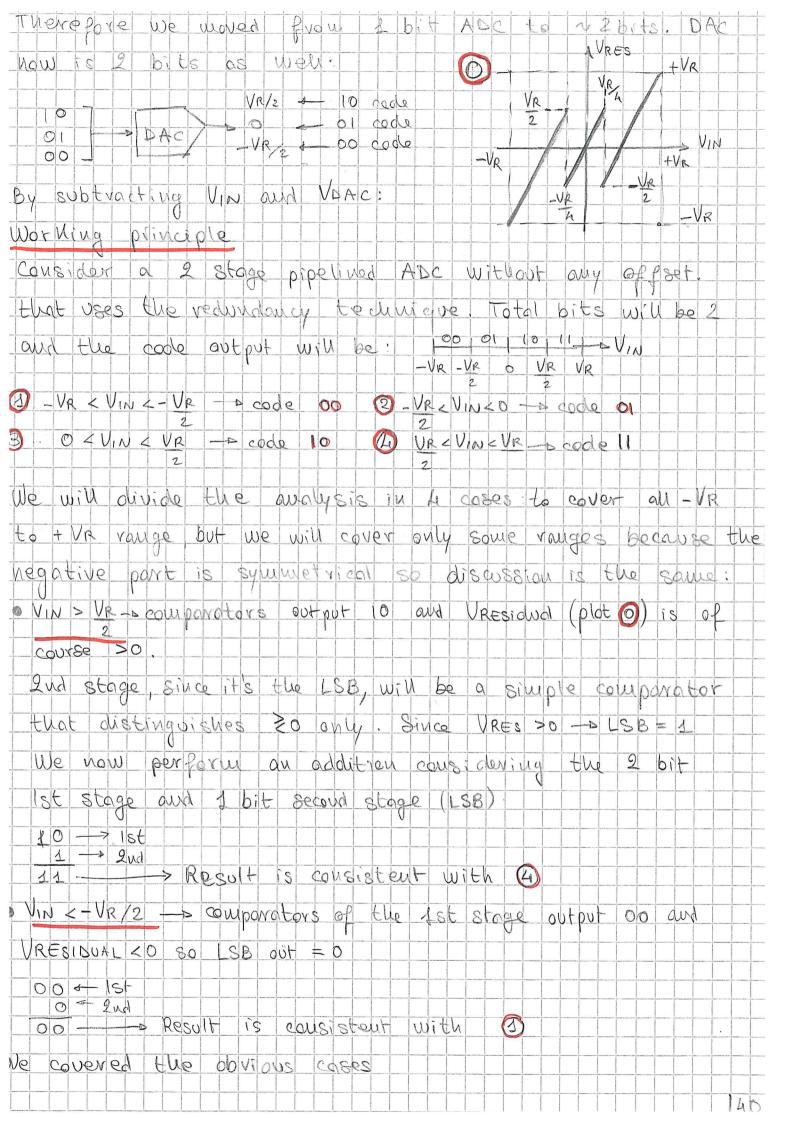

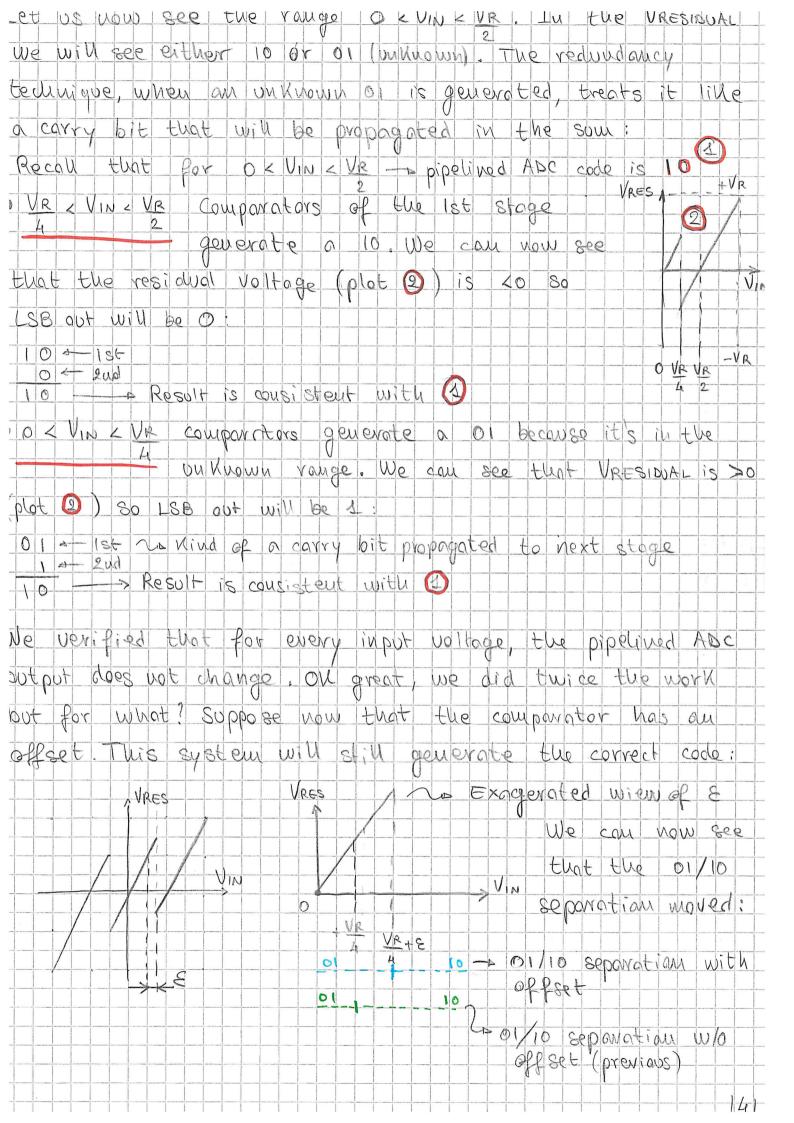

- 76. Redundancy technique explanation and its effect on offset

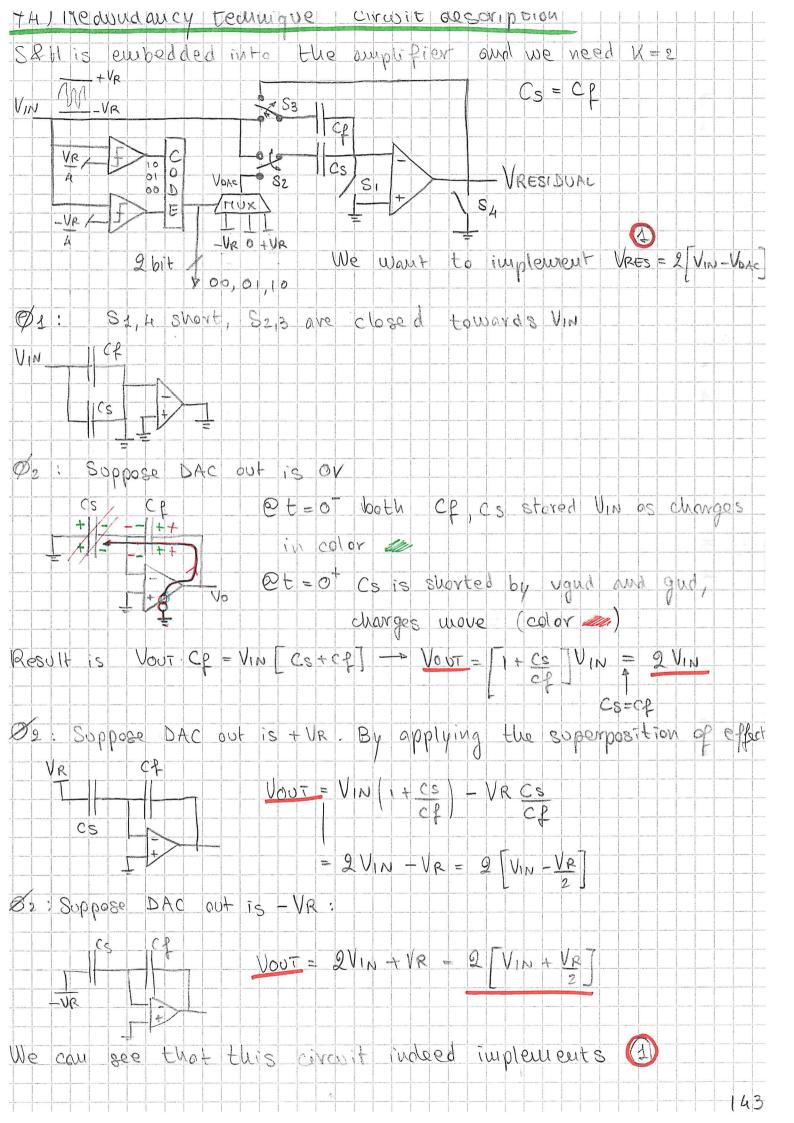

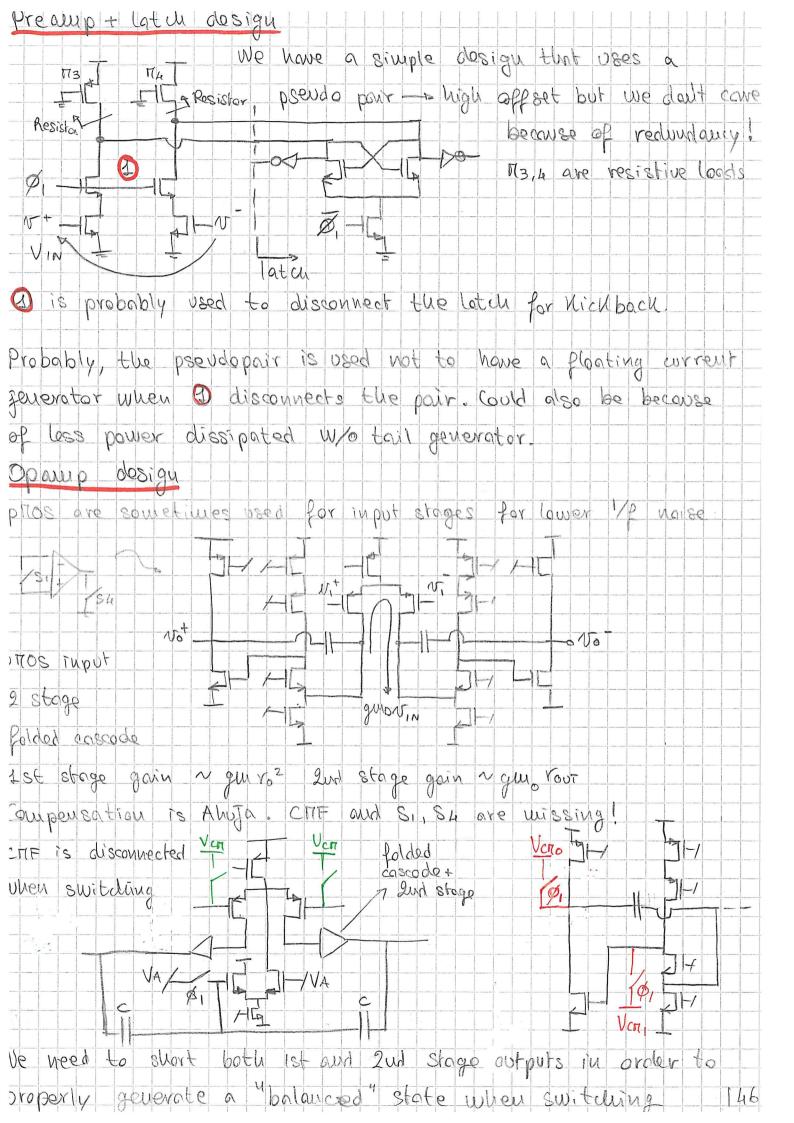

- 77. Redundancy technique circuit description: high level schematic, single blocks schematics

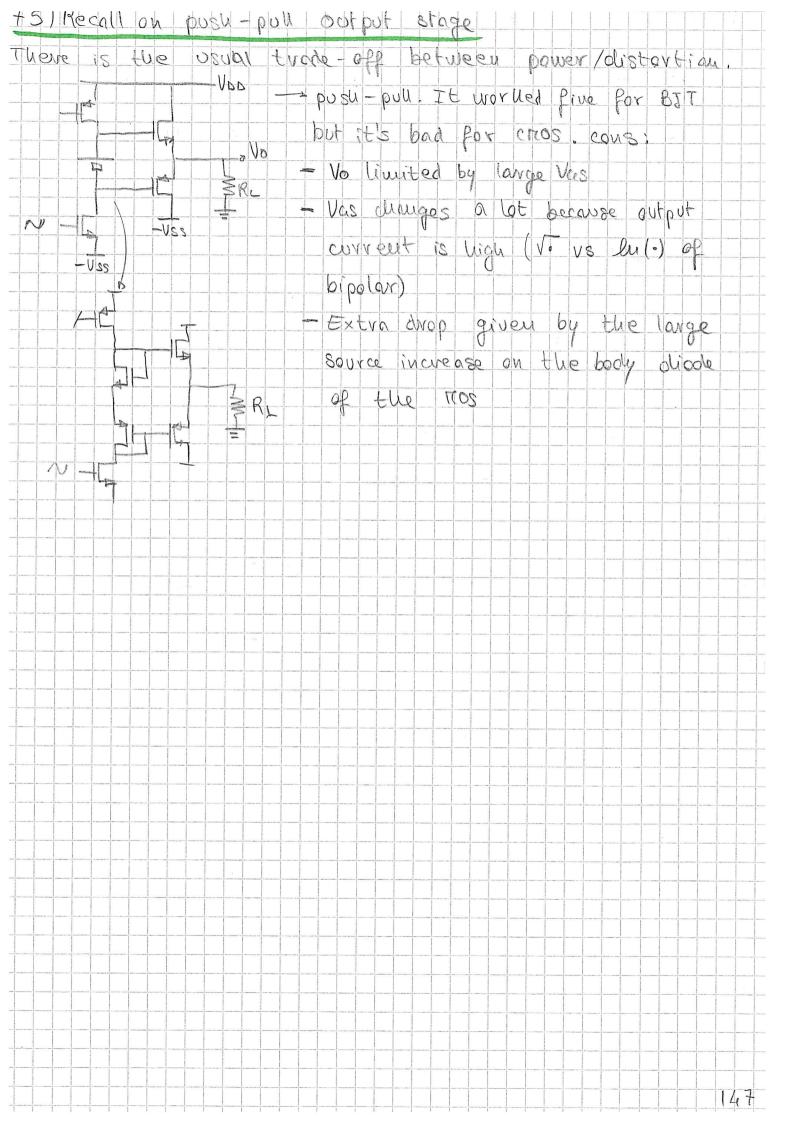

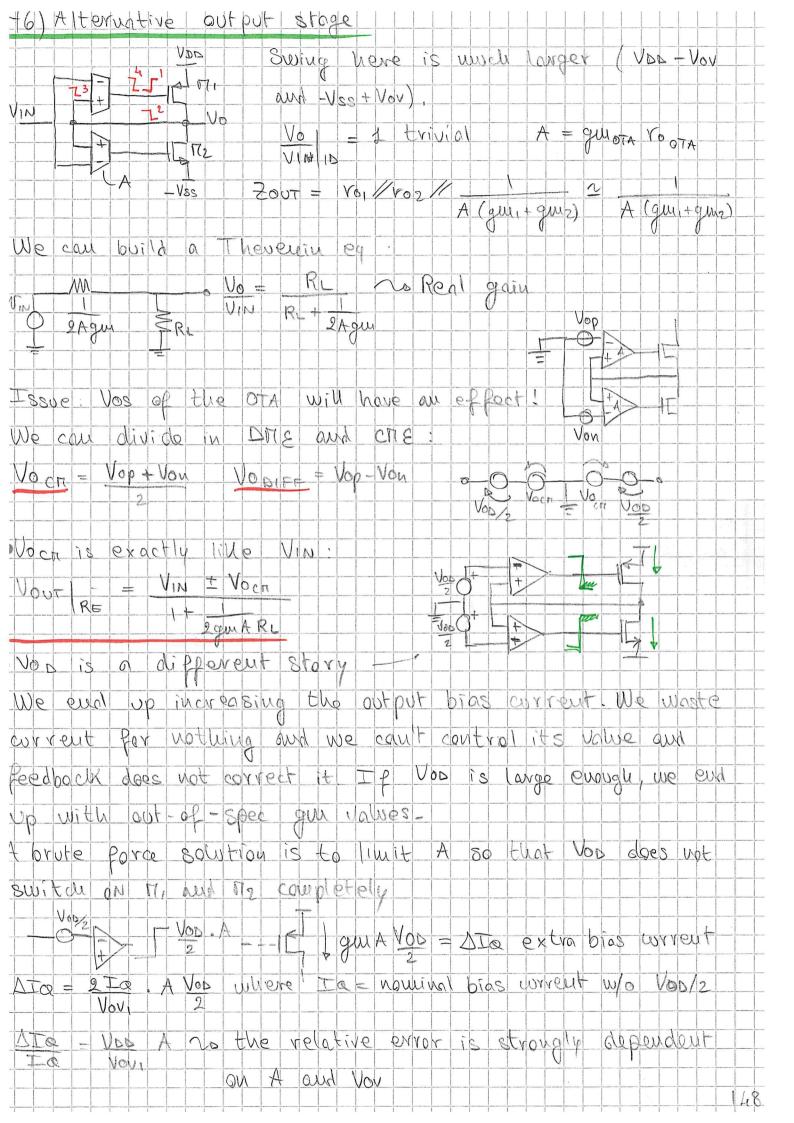

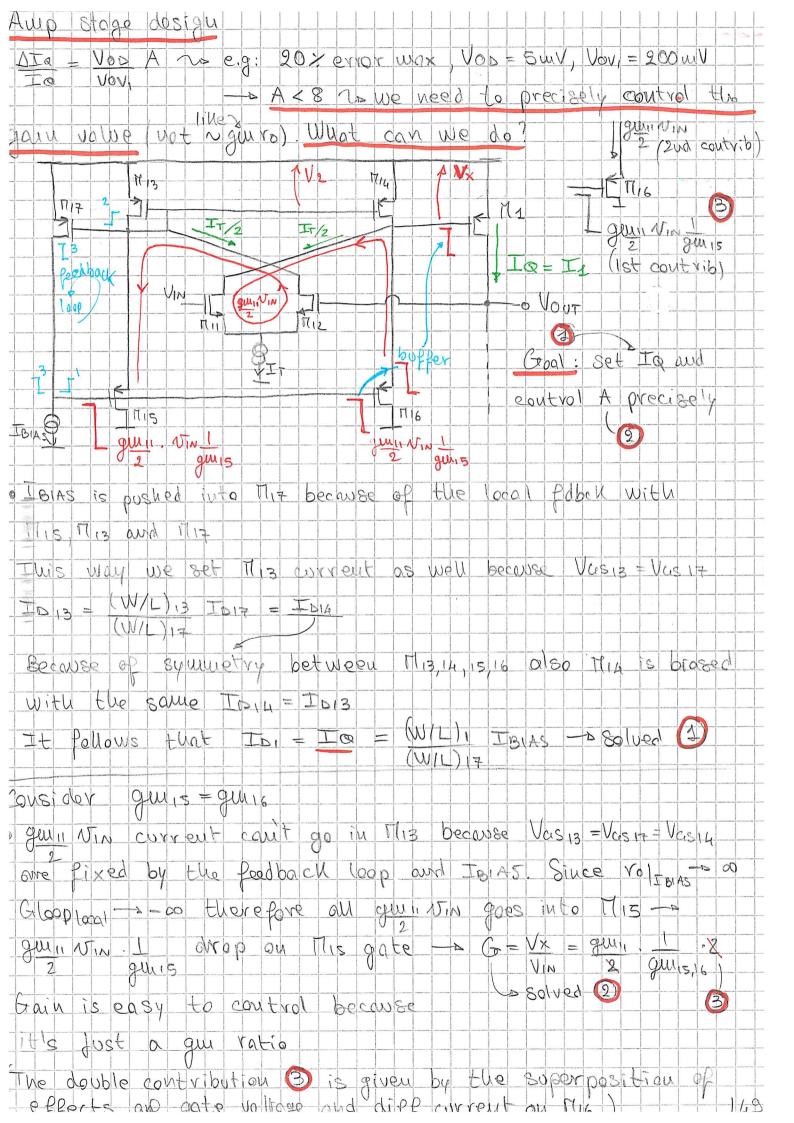

- 78. Recall on push-pull output stages

- 79. Alternative implementation for an output stage

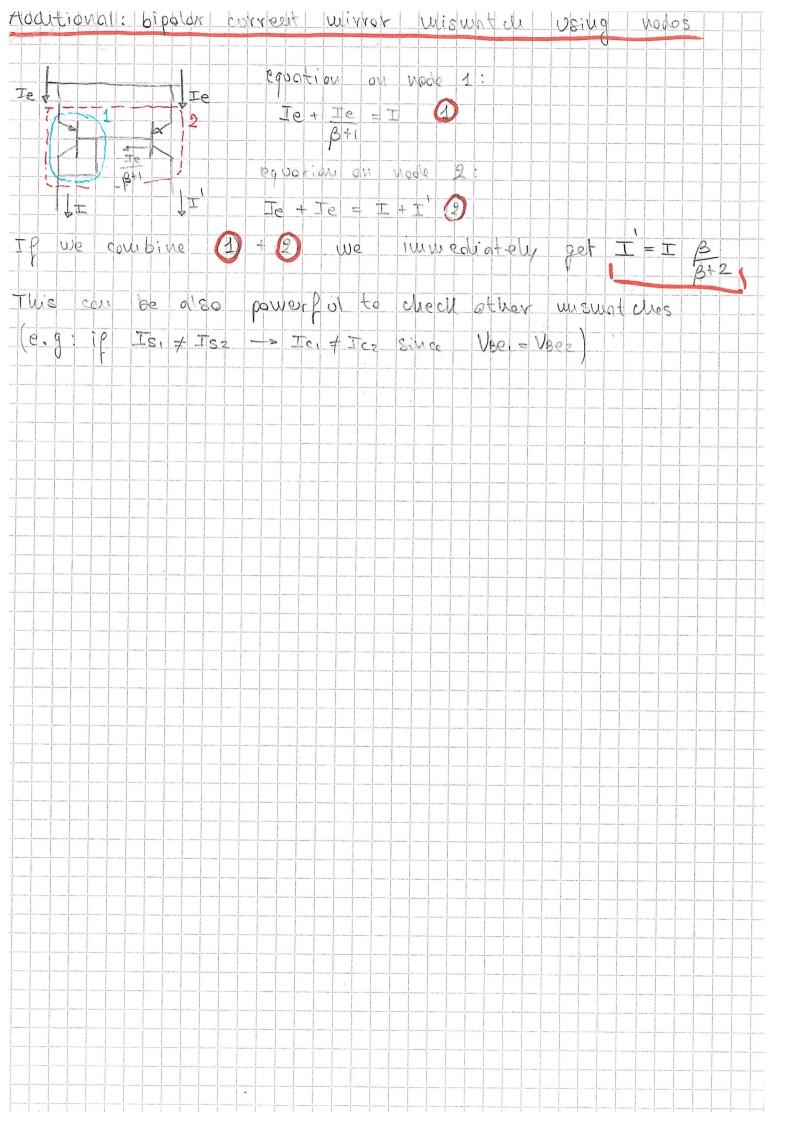

(source: Analysis and Design of Analog Integrated Circuits – P. Gray, P. Hurst, S. Lewis, R. Meyer, 5<sup>th</sup> Ed., John Wiley & Sons, 2009)

Source: IEEE Journal of Solid-State Circuits, vol. 33, no.12, Dec. 1998, pp. 1948-1958 (C. Lin, K. Bult)

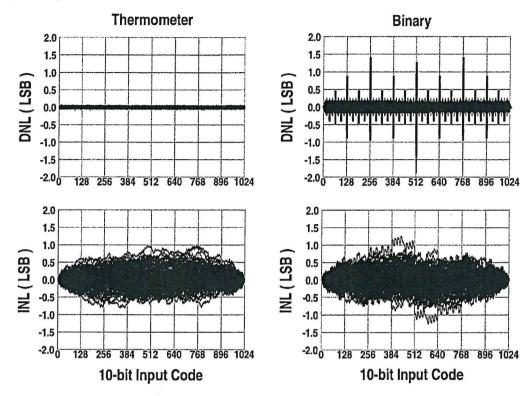

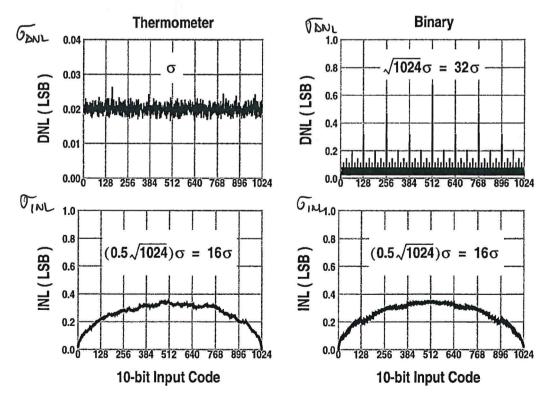

One hundred MATLAB simulation results for thermometer-coded versus binary-weighted DAC.

RMS of 100 MATLAB simulation results for thermometer-coded versus binary-weighted DAC.

Keep in mind that TSBs are the most critical stages in terms of noise/linearity/etc because they are the most important! It wouldn't make sense to have the same requirements of the DISB stage on the LSB ove LSB 7 least critical wrt offset/noise/ - 16 - P16 - P La highest performance linearity. This way, we can relax the power dissipation and watching requirements on the following stages Those pipelized 1 bit flash are typically osed in 10/12/16 bit and 10 MHz = 100s of MHz convertens

## Mixed Signal Circuits Design

## 8 Febbraio 2023

Giustificare tutti i risultati indicando tutti i passaggi. Indicare sempre a quale transistore ci si riferisce (e.g. la transconduttanza di Q1 è  $g_{m1}$ , la  $r_0$  di Q2 è  $r_{02}$  il  $\beta$  di Q3 è  $\beta_3$  etc...).

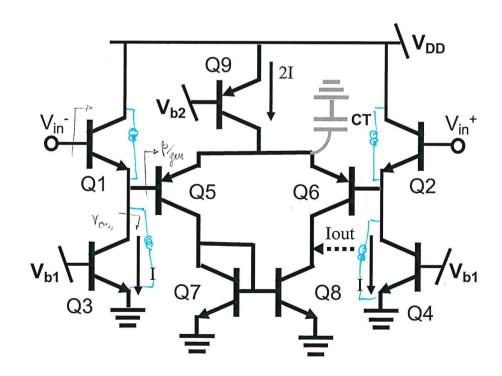

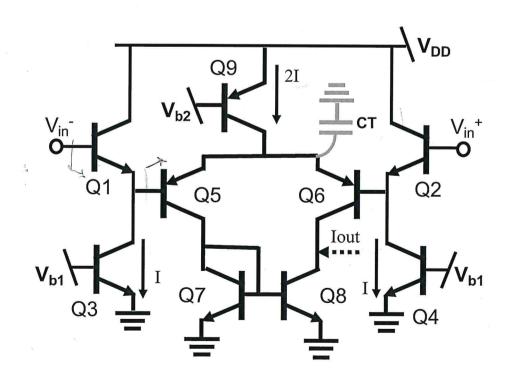

- i) Calcolare l'impedenza differenziale di ingresso. Calcolare quindi il guadagno di transconduttanza  $I_{out}/(V_{in}^+ V_{in}^-)$ . Si assuma  $\beta_n = 3\beta_p$ .

- ii) Calcolare il generatore serie (di tensione) di rumore in ingresso, considerando solo il contributo del rumore shot di collettore, di tutti i trasistori.

- iii) Ripetere il calcolo, considerando il contributo del rumore termico della resistenza di base (4kTr<sub>bb'</sub>) di tutti i trasistori. Assumere la stessa r<sub>bb'</sub> per tutti i transistori.

- iv) Ricavare la condizione riguardante la corrente I (una disuguaglianza) per cui questo secondo termine può essere trascurato rispetto al precedente, sapendo che  $r_{bb'} = 200 \Omega$  (assumere la temperatura ambiente).

- v) Calcolare l'offset di ingresso dovuto al mismatch delle correnti di saturazione della coppia Q1-Q2 (assumere  $+\Delta Is/2$  e  $-\Delta Is/2$ ). Ripetere lo stesso calcolo per la coppia Q7-Q8.

- vi) Calcolare il trasferimento tra un segnale di modo comune in ingresso e la corrente di segnale di uscita,  $2I_{out}/(V_{in}^+ + V_{in}^-)$ , in continua, dovuto solo all'errore di specchiamento (dovuto al  $\beta_n$  finito).

- vii) Ripetere il calcolo ad "alta" frequenza, ossia considerando l'effetto di C<sub>T</sub>. Tracciare i diagrammi di Bode (modulo e fase) quotati della funzione di trasferimento completa.

## **Mixed Signal Circuits Design**

## 8 Febbraio 2023

Always justify the results, indicating all the steps (do not provide only the results). Always indicate at what transistor you are referring to (e.g. the transconductance of Q1 is  $g_{m1}$ ,  $r_0$  of Q2 is  $r_{02}$ ,  $\beta$  of Q3 is  $\beta_3$  etc...).

- i) Evaluate the input differential impedance. Calculate the transconduttance gain, i.e.  $I_{out}/(V_{in}^+ V_{in}^-)$ . Assume  $\beta_n = 3\beta_p$ .

- ii) Evaluate the equivalent series (voltage) noise generator, considering only the contribution from the current collector shot noise sources for all the transistors.

- iii) Repeat the previous evaluation, considering only the thermal noise from the base resistance (4kTr<sub>bb</sub>) for all the transistors. Assume the same r<sub>bb</sub>, for all the transistors.

- iv) Derive the condition (an inequality) for the current I for which the second contribution is negligible with respect to the previous one, assuming  $r_{bb'} = 200 \Omega$  (assume room temperature).

- v) Calculate the input offset due to the mismatch of the saturation currents (assume  $+\Delta Is/2$  and  $-\Delta Is/2$ ). Repeat the same calculation for the couple Q7-Q8.

- vi) Evaluate the DC gain between an input common mode voltage signal, and the output current, i.e.  $2I_{out}/(V_{in}^+ + V_{in}^-)$ , due to the error in the mirror (due to the finite  $\beta_n$ ).

- vii) Repeat the same evaluation at "high" frequency, that is considering the effect of C<sub>T</sub>. Plot the Bode diagrams (magnitude and phase) of the entire transfer function.