## Topics for the orals 2025

- 1. Basic MOSFET operation: the charge sheet model, ohmic and saturation regime. Channel modulation and finite output resistance. Modulation voltage and dependence on channel length. Resistive coupling between source and drain terminals.

- 2. Subthreshold operation. Diffusion regime. Limit to the maximum voltage gain. Moderate inversion. Inversion coefficient. EKV model.

- 3. MOSFET's figures of merit: maximum voltage gain and cut-off frequency. Dependences on bias (strong, moderate and weak inversion).

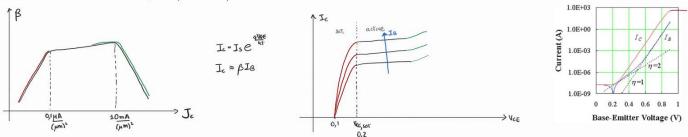

- 4. BJT basics: The planar npn structure. Current gain and transconductance. Early effect, maximum current gain. Gummel plot and beta dependence on current. High injection-low injection effects. Optimal bias. Options for pnp devices (lateral and substrate devices).

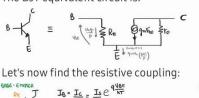

- 5. BJT equivalent circuit. Resistance values at the BJT terminals accounting for the resistive coupling between emitter and collector. Cut-off frequency in BJTs: diffusion capacitance and dependence on current density.

- 6. Independent/interacting capacitors and poles. Extension of the time constant method. Middlebrook's theorem. Examples with RC networks.

- 7. Quantitative description of noise: noise variance and noise power spectral density.

- 8. Noise transfer in circuits. Input referred noise sources of a two-port network. Definitions and derivation.

- 9. Noise models: Thermal noise of resistors. The Nyquist argument for the thermal noise power spectral density.

- 10. Noise models: Shot noise model. Application to p-n junctions, BJTs and MOSFETs in weak inversion.

- 11. Trapping noise: trapping noise in a resistor

- 12. McWorther model of the 1/f noise in MOSFETs. Tvidis formula.

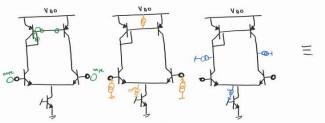

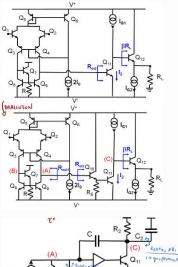

- 13. The prototypical differential stage: from resistive to active loads. Common mode feedback and single ended option.

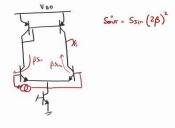

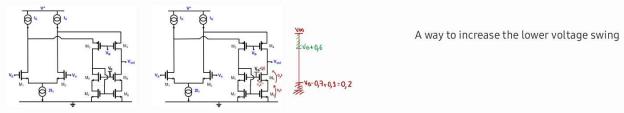

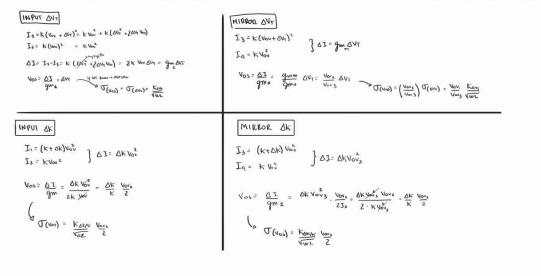

- 14. Single ended differential stage with mirror: Bias, input and output voltage swings, differential gain, Common mode gain.

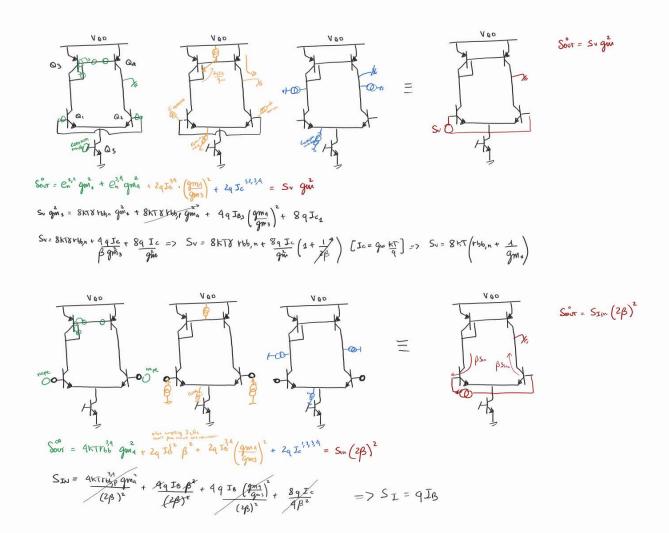

- 15. Input referred noise sources of a differential stage with MOSFETs and BJTs. Power-noise trade-off.

- 16. Two-stage CMOS OTA: topology, frequency response using the time constant method, Miller compensation. Pole splitting vs. compensation capacitance value. The RHP zero and the high frequency pole. OTA compensation and FoM.

- 17. Two-stage CMOS OTA: frequency compensation with the nulling resistor. Implementing the nulling resistor.

- 18. Two-stage CMOS OTA: frequency compensation with ideal voltage and current buffers. Impact of the buffer finite resistance.

- 19. Two stage bipolar amplifier: input resistance, input referred voltage and current noise, sizing example and compensation.

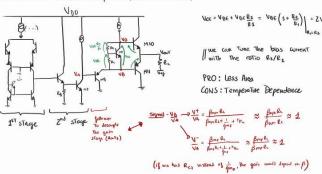

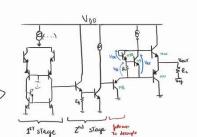

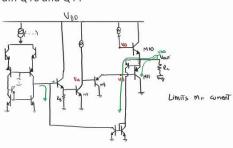

- 20. uA741 first stage, bias and common mode feedback, output resistance, differential gain. Mirror with emitter follower and bleeding resistor. Wilson's mirror.

- 21. uA741 second stage. Setting the bias: trade-off between gain and input impedance. Frequency response.

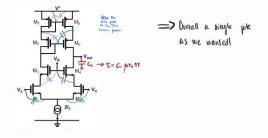

- 22. Single-stage CMOS OTAs: telescopic cascode topology, differential gain, input and output voltage swing, power dissipation, frequency response.

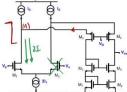

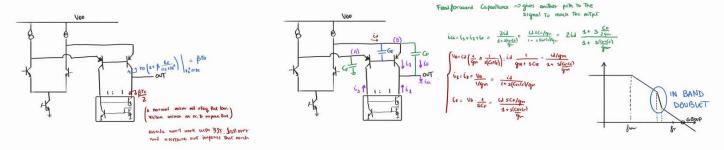

- 23. Folded cascode topology, enhanced mirrors, voltage dynamics, power dissipation. Folded cascode with bipolar transistors. Feed-forward compensation.

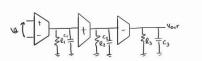

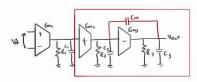

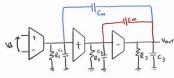

- 24. Three-stage CMOS OTA: Nested Miller Compensation

- 25. OTA Linear response. In-band zero-pole doublets and features of the settling response.

- 26. The slew rate limit. Impact on settling time. CMOS-OTA: Internal and external slew rate limits. Improving SR with class AB output stages.

- 27. Output stages: Emitter follower as output stage. Emitter follower efficiency. Push-pull. Efficiency. Cross-over distortion. Class A-B stage. Total harmonic distortion. Distortion reduction by feedback.

- 28. Output stages in bipolar technology (uA741). Short-circuit protections.

- 29. Variability and matching: Relative matching of threshold voltage values. Common centroid. Pelgrom's formula

- 30. Variability and matching: Relative matching of resistors. Common centroid. Pelgrom's formula

- 31. OTA: Offset. Deterministic and statistical contributions to input referred offset. Input referred offset in bipolar differential stages. Temperature effects.

- 32. OTA: Common-mode rejection ratio. Deterministic and statistical limits to CMRR

I DO NOT GUARANTEE THE ACCURACY OF THE ANSWERS, NOR MY ENGLISH

Given the structure of a mosfet, we can write the Ohm Law and in particular, the voltage across a section of the channel. 30 - 150 JR We know that the resistance from the second Ohm Law is given by:  $30 - 100 \text{ JR} = \frac{1}{100} \text{ JR}$

V<sub>1</sub> V<sub>2</sub> V<sub>3</sub> V<sub>4</sub> V<sub>5</sub>

The mobility indicates how easily carriers move under an electric field and n indicates the number of carriers per unit volume.

We can rewrite the voltage drop across a section as:

| Voc = Instruction |

Now we adopt the approximation of the <u>charge sheet model</u>: we assume that the charge carriers in the channel are concentrates in very thin layer, "sheet", near the oxide. Given this model, the charge can be expressed by:  $\begin{cases} Q_{n}^{*}(k) = C_{n}^{*}(\sqrt{k_{0}-V_{0}}) \\ Q_{n}^{*}(k) = C_{n}^{*}(\sqrt{k_{0}-V_{0}}) \end{cases} \Rightarrow Q_{n}^{*}(k) = C_{n}^{*}(\sqrt{k_{0}-V_{0}})$ Now, doing some math...

Finding the classic relationship of a MOSFET in the ohmic region. Studing this function, we can see that the current has a parabolic dependence on Vds and reach a maximum when:  $\frac{\partial I_{NS}}{\partial V_{0S}} = \varnothing \implies \mu^{C_{OS}} \underbrace{\mathbb{E}} \left[ (V_{0S} - V_1) - V_{0S} \right] = \varnothing \implies \underbrace{V_{0S} = V_{0S} - V_1}{2} \implies I_{0S} = \mu^{C_{OS}} \underbrace{\mathbb{E}} \left[ (V_{0S} - V_1) - V_{0S} \right] = \varnothing \implies \underbrace{V_{0S} = V_{0S} - V_1}{2} \implies I_{0S} = \frac{1}{2} \mu^{C_{OS}} \underbrace{\mathbb{E}} \left[ (V_{0S} - V_1) - V_{0S} \right] = \varnothing \implies \underbrace{V_{0S} = V_{0S} - V_1}{2} \implies I_{0S} = \underbrace{V_{0S} - V_1}{2}$

After the vertix of the parabola, the ohmic expression is no longer valid, in fact it makes no sense that increasing Vds makes the electron density to decrease. To understand better what happens, we should remember that a current continuity should always remain: all the carriers leaving the source per unit time has to be equal to the electrons reaching the drain. Given that, as the carriers density decrease along the channel, there's a need of increasing the electric field (so the velocity of the carriers) to keep the carriers per unit time constant.

When we reach the saturation of the electric field, we reach the so called "pinch-off", where the charge at the drain is "zero" (not true, given by charge sheet approx).

However, increasing Vds even more, we notice that the current increase a bit. This can be explained by taking to account that the pinch-off moves back to the source by a small amount. Calling L' the new channel length, and knowing that it depends on the voltage across Vds, we can describe L'

back to the source by a small amount. Calling L' the new channel length, and knowing that it depends on the voltage across Vds, we can des with a first order approximation:

$$L'(v_{0S}) = L'(v_{0S}) \Big|_{v_{0S} = v_{0S,ext}} + \frac{\partial L'(v_{0S})}{\partial v_{0S}} \Big|_{v_{0S} = v_{0S,ext}} + \frac{\partial L'(v_{0S})}{\partial v_{0S}} \Big|_{v_{0S} = v_{0S,ext}} + \frac{\partial L'(v_{0S})}{\partial v_{0S}} \Big|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S})}{\partial v_{0S}} \right|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S})}{\partial v_{0S}} \right|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S})}{\partial v_{0S}} \right|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S})}{\partial v_{0S}} \right|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S})}{\partial v_{0S}} \right|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S})}{\partial v_{0S}} \right|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S})}{\partial v_{0S}} \right|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S})}{\partial v_{0S}} \right|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S})}{\partial v_{0S}} \right|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S})}{\partial v_{0S}} \right|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S})}{\partial v_{0S}} \right|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S})}{\partial v_{0S}} \right|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S})}{\partial v_{0S}} \right|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S})}{\partial v_{0S}} \right|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S})}{\partial v_{0S}} \right|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S})}{\partial v_{0S}} \right|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S})}{\partial v_{0S}} \right|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S})}{\partial v_{0S}} \right|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S})}{\partial v_{0S}} \right|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S})}{\partial v_{0S}} \right|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S})}{\partial v_{0S}} \right|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S})}{\partial v_{0S}} \right|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S})}{\partial v_{0S}} \right|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S})}{\partial v_{0S}} \right|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S})}{\partial v_{0S}} \right|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S})}{\partial v_{0S}} \right|_{v_{0S} = v_{0S,ext}} \Big| = L - \left| \frac{\partial L'(v_{0S$$

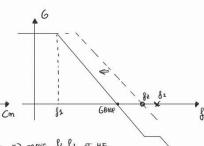

So, we can model a MOSFET in saturation as an ideal current generator with a finite output resistance, leading to a maximum gain of :

Resistive coupling: source resistance

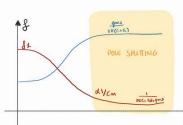

#### 2. Subthreshold operation. Diffusion regime. Limit to the maximum voltage gain. Moderate inversion. Inversion coefficient. EKV model. (L01\_24) 鱳

We have found before that the maximum gain for a mosfet is given by: Grows of the found before that the maximum gain for a mosfet is given by: Grows of the found before that the maximum gain for a mosfet is given by: Grows of the found before that the maximum gain for a mosfet is given by: Grows of the found before that the maximum gain for a mosfet is given by: Grows of the found before that the maximum gain for a mosfet is given by: Grows of the found before that the maximum gain for a mosfet is given by: Grows of the found before that the maximum gain for a mosfet is given by: Grows of the found before that the maximum gain for a mosfet is given by: Grows of the found before that the maximum gain for a mosfet is given by: Grows of the found before that the maximum gain for a mosfet is given by: Grows of the found before that the maximum gain for a mosfet is given by: Grows of the found before the found befor

We always said that Vgs>Vt was needed to be on, but actually it is just the invertion condition at the source to create a channel. Actually, even if Vg=0, there's a  $\Phi_{ws}$  given by the metal junction (because of Fermi). Part of this voltage will drop on the "fake" channel, making the majors carriers to move down and create a deplited region where the current may flows.  $\Delta N_S = \Delta N_G \frac{Cox}{Cox + Cox}$

In the deplited regime, the mosfet is made by a npn junction, like a bjt! We can now study the carriers profile according to Boltzman:

In the moderate inversion regime, the current is both given by a drift and a diffusion, so we can adopt a model, called EKV model (Enz-Krummenacher-Vittoz model) to describe the behaviour of a mosfet both by a drift contribution and a diffusion one. We introduce an inversion coefficient IC that mesure the level of inversion:

$$I_{D} = I_{S} e^{\frac{N(S)^{-1/4}}{N(N)^{3}}}$$

$$I_{S} = 4n k' \frac{W}{L} (Vn)^{3}$$

$$I_{C} = I_{D} \longrightarrow 01cICc(0) \text{ moderative}$$

$$I_{C} > 10 \text{ strong}$$

$$g_{m} = \frac{I_D}{n \text{ With }} \left( \frac{2}{1 + \sqrt{4IC + 1}} \right)$$

|     | BJT        | 45          | MOSFET   |

|-----|------------|-------------|----------|

| G   | VA/VIL     |             | VA/n VTh |

| gni | I/VIL-     |             | I/n VTh  |

| VA  | ~ 100 Just |             | oc L     |

| ro  | Va/T       | 0.000-10000 | VALT     |

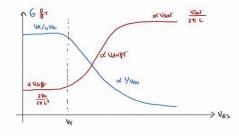

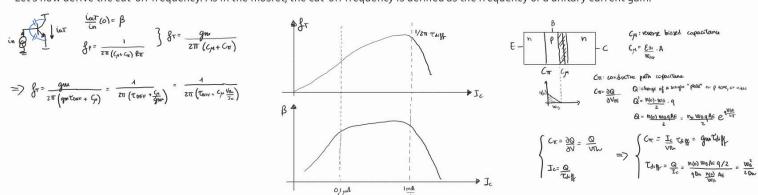

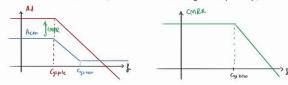

There are three key points that define the effecency of a transistor: gain, bandwidth and noise. Let's dive deep into the trade off between the gain and the bandwidth. As we saw before, the gain goes like 1/Vov and reach a max gain of Va/n Vth (check answer 2). Now we want to see if and how the bandwith has a dependence on bias in weak, moderate and strong inversion regime.

In a mosfet we can define two intrinsic capacitances: Cgs, between gate and source, due to the charge accumulated in the channel, and a Cgd, between gate and drain, maily because there's a overlap between gain and drain.

The cut-off frequency is the frequency for a unit current gain, so we can derive:

Now that we have derived the value of the cut-off frequency, we have to evaluate it under different bias. In strong inversion, tau =  $t_d$ rift, increasing when Vov increase, until the velocity reach the saturation value. In weak inversion tau =  $t_d$ iff.

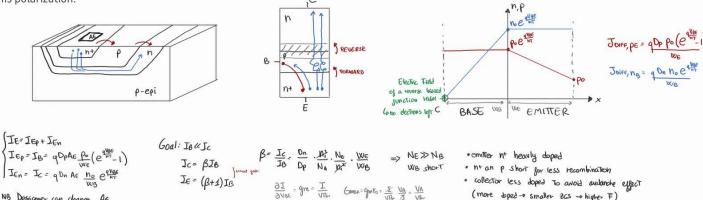

Let's start with the physics of the npn bjt transistor. Our goal is to inject from the base and collect electrons from the collector. To do so, we need

this polarization:

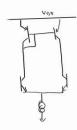

Now that we derived the current, let's plot its dependence with Vce:

Let's frist comment the beta plot. We can distinguish three zones: the red one, for low values of Ic, the ricombination of carriers in the base zone is relevant, a flat zone where the device works properly and a green zone where the kirk effect (base modulation effect) takes place: when the ZCS starts increasing (we are increasing the reverse bias voltage), at first the main relevant effect is the decreasing of Wb, leading to less ricombination, increasing the current. After a certain value, the beta drops down (max electric field?)

We can see the same effect in the Current x Vce plot. An important details is that the Ic plot may not start from (0,0)! This is due to the fact that:  $I_{c} = \emptyset \Rightarrow \text{Notes m } E \stackrel{\text{\tiny $z$}}{=} \text{Notes m } E \stackrel{\text{\tiny $z$}}$

Then we enter the saturation region in red, where the np junction isn't reverse biased yet and holes both flow in E and C. As soon as it is reverse biased, we enter the active region very similar to the saturation region of a MOSFET, and then when the kirk effect kicks in, we have an increasing current and then drops down.

The third graph, is the well-known Gummel Plot, where Ic and Ib are plot in logaritm (so the beta is the difference) and the x axis is Vbe. Between 0.5 and 0.8 we have that their values are in the correct regime and everything is fine. As Vbe becomes less, the recombination of carriers in the base becomes more relevant (because the ZCS of the base-emitter junction becomes a relevant site of recombination). For high Vbe, Ic reach a sort of saturation because we arrive of a certain saturation of the reversed biased junction (?) (Not required)

Since we've studied that we cannot rely on beta, it is better not to bias the BJT with the base current! Let's see how to correctly bias it:

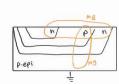

Let's now discuss about pnp BJT. Since the price of a device depends on the number of steps, industries usually adapt the same steps of a npn fabrication to do pnp. This means that also the doping is the same!

Let's first focus on lateral pnp. We start from a p-epi and then we build a device similar to a MOSFET. Since we have the same dopants, we do not have Nc<<Nb as we should, so the ZCS will extend into the collector and not the base -> large Wb -> lot od recombination!!

A vertical pnp is an upgrade version, but not always possible. In this case we use the substrate to have Nc<<Nb and have less ricombination.

NB: since we are using the substrate, we do not have an isolation layer, so we should keep the collector connected to the ground!!!

Even if we have the correct doping, since the working principle is linked to the holes and not electrons, the beta will be lower than npn device (the mobility of holes is always less than the mobility of electrons)

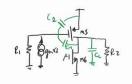

The BJT equivalent circuit is:

EMITTER RESISTANCE

Let's now derive the cut-off frequency. As in the mosfet, the cut-off frequency is defined as the frequency of a unitary current gain.

In conclusion, we know that to guarantee a low power dissipation, we prefer a low bias, but it means also that the cut-off frequency (the speed of the device) decrease!! (and we should also remember that the noise also depends on Ic, but that is a story for another time)

It is known that a transfer function in Laplace Domain is written as:  $T(s) = A_0 \frac{b_m S^m + b_{m-1} S^{m-1} + \dots + b_1 s + 1}{a_m S^m + a_m S^{m-1} + \dots + a_1 s + 1}$

For an electronic circuit, Ao is the DC gain, the roots of the numerator (so when T(s)=0) are called zeros and the roots of the denominator (T(s)->inf) are called poles. Our goal is to find an algorithm to find all the coefficients.

First of all, we should define what's a indipendent or interactive capacitor. We define two or more capacitors as indipendent when they can be analyse seperatly because they are isolated to each other (ex: there's a gate in between or a buffer), while we call two or more capacitors interactive when they influence each other.

The cofficient n is given by the number of indipendent capacitors of the circuit, while the coefficient m is always less or equal to n.

Let's start with a single capacitor network to set the basics to find the coefficients b and a. Since the network is linear, we can write:

$$V_{\text{eff}} = \frac{1}{R^{\text{fic}}} - \frac{1}{R^{\text{fic}}}$$

So, the DC gain, is the gain between vin and vout when C1 is open, the pole is given by the resistance seen across C1 terminals when vin is a short and the zero is the resistance seen across C1 terminals when vout is zero.

In a two capacitors network, if the two capacitors are indipendent, we can derive some other rules. Let's take this circuit:

Let's now derive a general rule to find coefficients (also known as Middlebrook theorem): Given a three capacitor network:

$$T(s) = A_0 \frac{a_3 s^3 + a_2 s^4 + a_3 s + 4}{b_3 s^3 + b_1 s^4 + b_2 s + 2}$$

$$b_1 = C_4 C_4 R_1^2 R_2^4 + C_3 C_5 R_2^6 R_3^4 + C_4 C_5 R_3^6 R_3^4 + C_$$

An easy example of a RC network with a single capacitor can be:

The early example of a RC fletwork with a single capacitor cambe:

$$\sqrt{\frac{C_1}{R_2}} \sqrt{\frac{C_3}{R_3}} = A_0 \quad \frac{1 + 5C_3R_{03}}{1 + 5C_3R_2} \quad \begin{cases}

A_0 = \frac{Rb}{R_0 + Rb} \\

R_{04} = R_0 & R_0

\end{cases}$$

(an be added also the calculation of  $\frac{C_1}{R_0}$  for interactive capacitors)

$$\frac{1}{R_0} \sqrt{\frac{R_0}{R_0}} \sqrt{\frac{R_0}{R_0}} = \frac{R_0}{R_0} \sqrt{\frac{R_0}{R_0}} \sqrt{\frac{R_0}{R_$$

Actually, you should do ...

$$\Rightarrow T(s) = To \frac{s^{2} \alpha_{2} + s \alpha_{3} + 1}{s^{2} b_{2} + s b_{3} + 2} = To \frac{s^{2} (GC_{2} d_{1}) + s (Gd_{1} + Gd_{2}) + \Delta}{s^{2} (GC_{1} \beta_{11}) + s (G\beta_{1} + G\beta_{2}) + \Delta}$$

$$C_{2} = \emptyset \implies \frac{SC_{2}d_{1}+1}{SC_{2}\beta_{1}+1} \longrightarrow \emptyset \xrightarrow{d_{1}} \frac{g_{0}^{(1)}}{\beta_{1}} = R_{2}^{(0)}$$

$$C_{1} \to \emptyset \implies \frac{S^{2}C_{1}C_{1}}{S^{3}C_{1}C_{2}} \xrightarrow{d_{1}} \frac{SC_{1}d_{1}}{S^{3}C_{1}C_{2}} = \frac{SC_{1}d_{1}}{SC_{1}\beta_{1}} \xrightarrow{(1+SC_{2}\frac{d_{1}^{(1)}}{d_{1}})} \longrightarrow \frac{d_{1}u}{d_{1}} \times R_{02}^{(1)} \longrightarrow d_{1}u \times R_{02}^{(1)} = R_{01}^{(1)}R_{04}^{(0)}$$

$$C_{1} \to \emptyset \implies \frac{S^{2}C_{1}C_{1}}{S^{3}C_{1}C_{2}} \xrightarrow{g_{1}} \frac{SC_{1}d_{1}}{SC_{2}\beta_{1}} \xrightarrow{(1+SC_{2}\frac{d_{1}^{(1)}}{d_{1}})} \longrightarrow \frac{d_{1}u}{d_{1}} \times R_{02}^{(1)} \longrightarrow d_{1}u \times R_{02}^{(1)} = R_{01}^{(1)}R_{04}^{(1)}$$

$$C_{1} \to \emptyset \implies \frac{S^{2}C_{1}C_{1}}{S^{3}C_{1}C_{2}} \xrightarrow{g_{1}} \frac{SC_{1}d_{1}}{SC_{2}\beta_{1}} \xrightarrow{g_{1}^{(1)}} \frac{d_{1}u}{d_{1}} \times R_{02}^{(1)} \longrightarrow d_{1}u \times R_{02}^{(1)} \longrightarrow d_{1}u \times R_{02}^{(1)}$$

$$C_{1} \to \emptyset \implies \frac{S^{2}C_{1}C_{1}}{S^{3}C_{1}C_{2}} \xrightarrow{g_{1}^{(1)}} \frac{SC_{1}d_{1}}{SC_{2}\beta_{1}} \xrightarrow{g_{1}^{(1)}} \frac{d_{1}u}{d_{1}} \times R_{02}^{(1)} \longrightarrow d_{1}u \times R_{02}^{(1)} \longrightarrow d_{$$

#### 7. Quantitative description of noise: noise variance and noise power spectral density. (L02\_16) 14.

In a electronic circuit, we do not only have our signal that propagates but also a contribution of electronic noise and disturb.

Disturb is given by external sources and can be filtered by taking appropriate actions while we cannot separate the noise from our signal, so we should quantify the average value of the noise, so that derive the minimum signal that we should apply.

Since a noise is a flactuation in time, it can be considered as a gaussian with zero mean value and with parameters not depending on time. To have a quantitative measure, we can take  $\sigma$ , so where 68% of samples fall.

By definition, σ = Ε(x 'm) - (ε α m)' but keeping in mind that in our case, the mean value is zero!

Since the noise can be described as a superposition of orthogonal armonics:

x(T) = A sen (W, T + Y, ) + Bsen (W2T+ Y)

$\langle x(\tau) \rangle = \langle A^2 S \omega^t \left( \omega_t \tau_t \phi_t \right) + B^2 S \omega^2 \left( \omega_t \tau_t \phi_t \right) + 2AB S \omega_t \left( \omega_t \tau_t \phi_t \right) S \omega_t \left( \omega_t \tau_t \phi_t \right) \rangle = \frac{A^2}{2} + \frac{B^2}{2} + \frac{B^2}$

So, we can derived that the variance is equal to the sum of variance values of single component. More in general, we can say:  $\sigma^2 \not\subseteq \sigma^2 \subseteq S_{n}$  So, we can derived that the variance is equal to the sum of variance values of single component. More in general, we can say:  $\sigma^2 \not\subseteq \sigma^2 \subseteq S_{n}$  So, we can derived that the variance is equal to the sum of variance values of single component. More in general, we can say:  $\sigma^2 \not\subseteq S_{n}$  So, we can derived that the variance is equal to the sum of variance values of single component. More in general, we can say:  $\sigma^2 \not\subseteq S_{n}$  So, we can derived that the variance is equal to the sum of variance values of single component. More in general, we can say:  $\sigma^2 \not\subseteq S_{n}$  So, we can derived that the variance is equal to the sum of variance values of single component.

#### Conclusions

- 1) Knowing the noise (voltage or current) power spectral density in a node of a circuit, we can know the noise in another node of the circuit (input, output, etc) just by multiply by the transfer function squered and sum with the other variance square of the other noise in that node.

- 2) Knowing that the variance comes from the integral in frequency, if we know that a signal has a limited bandwidth, we should ALWAYS filter the signal + noise around the bandwisth of our interest in order to reduce the noise.

#### 8. Noise transfer in circuits. Input referred noise sources of a two-port network. Definitions and derivation. ()

Noise in electrical circuits propagates through components and systems, influencing performance. A **two-port network** is a convenient model to analyze how noise sources within a circuit contribute to the overall noise at the output or are referred back to the input.

This model consist on replacing the circuit with an ideal, noiseless circuit with equivalent noise sources at the input terminals.

Deriving the equivalent noise source is a simple algorithm of few steps: to derive the input-referred voltage noise, we short both input and output and finds icc at the output and devide it by the square of the gain Gm (voltage->current)

$$S_{s_{0}(\xi)} = S_{s_{0}(\xi)}$$

Instead to derive the input-referred current noise, we keep short the output and keep the input open. This time we divide Sout by the square of the current gain (current -> current) or simply Zin \* Gm

Let's use the two port network theorem for a mosfet:

$$S_{out}^{s} = S_{out} S_{out}^{s} = S_{out}^{s} S_{out}^{s} S_{out}^{s} = S_{out}^{s} S_{out}^{s} S_{out}^{s} = S_{out}^{s} S_{out}^{s} S_{out}^{s} S_{out}^{s} = S_{out}^{s} S_{out}^{s} S_{out}^{s} S_{out}^{s} = S_{out}^{s} S_{out}^{s} S_{out}^{s} S_{out}^{s} S_{out}^{s} S_{out}^{s} = S_{out}^{s} S_{out$$

Let's have a confirm that the two port theorem is valid for every input resistance:

Overall, the input resistance will shift the pole, so where the current or the voltage input referred noise is dominant.

#### 9. Noise models: Thermal noise of resistors. The Nyquist argument for the thermal noise power spectral density. (L02\_17) 🚦

Since noise is given by random walk of carriers that may invert their direction due to scattering with ions (<1ps), we can consider their contributions as spike, so their spectrum is expected to be constant (at least in our range of frequencies). This type of noise is called White Noise because of it's spectrum. Considering a simple network with a capactior, we try to exploit the variance:

$$\sqrt{n} \int_{0}^{\infty} \frac{1}{1} \int_{0}^{\infty} \int_{0}^{\infty} dt = \frac{1}{1 + 3 + 2} \int_{0}^{\infty} dt = \frac{1}{1 + 3$$

Now we should derive the value W based on thermodynamic argument. In a single capacitor network, the energy can be stored only there and the only variable that set it is the voltage across the capacitor. Since the system has a single degree of freedom, we can say:

$$\frac{1}{2} C \left( v_c^2 \right) = \frac{1}{2} k_B T \quad \Rightarrow \quad \left( v_c^2 \right) = \frac{k_B T}{C} \quad \Rightarrow \quad \frac{w}{4 t} \cdot \frac{k_B T}{C} \quad \Rightarrow \quad w_c \cdot 4 k_B T R \quad \Rightarrow \quad S_v \left( \frac{a}{b} \right) = \frac{4 k_B T}{e} R$$

In a mosfet in ohmic regime, we can use the same result, considering that the resistance seen is the resistive channel:  $\frac{1}{R_{ch}} = \frac{\partial L}{\partial V_{bs}} \Big|_{vac, \neq f} = \frac{\partial L}{\partial V_{bs}} \Big|_{vac, \neq$

$$\frac{1}{R_{ch}} = G_{ch} = \frac{\partial I}{\partial V_{so}} \Big|_{con} = \mu C_{cx}' \left( \frac{w}{L} \right) (V_{6s} - V_{7}) = g_{uu} \qquad \qquad S_{v}(g) = 4 k_{6} T_{R_{ch}} = \frac{4 k_{6} T}{g_{uu}}$$

In the saturation region, since the channel is not uniform anymore, we can consider a correction factor:  $S_{\text{var}} = \frac{4 \text{KT} S}{qw}$

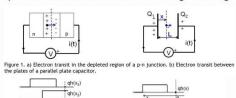

Now we analyse the carriers in a pn junction. The bias current is defined as the average number of carriers crossing the junction per unit time, but since it can be affected by statistical flactuations, it is also a source of noise, called "shot noise". To describe it, we want to find the variance (in current):  $\sigma_{1}^{2} = \langle i^{2} \rangle - \langle i \rangle^{2}$

Our first goal is to determinate the current. Let's start considering the pn junction as a parallel plate capacitor where each carrier is a charge moving

between the plates. An electron at distance x from the first plate gives a contribuition of charge of Q1 for the first plate and Q2 for the second one, with Q1+Q2=q always.  $Q_2 = \frac{q^2}{L}$ The current is given by: i(t)= 10 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 | = 0 |

We find that the current is proportional to the instantaneous carrier speed. In vacuum, the carrier over time will give a triangular pulse contribution, instead, in our case, we imagine that the velocity has saturated and the pulse has a rectangular shape with i(t)=qh(t).

Overall the shot noise is given by all these pulse that occur at a certain time.

We denote  $\lambda$  as the average rate of carriers across the junction per unit time, so we have that the number of pulses starting from t and t+dt is given by  $\lambda \lambda \tau$

The current measured at an instant t will be given by the superposition of all the pulses before t.

We know from the basics that the Fourier Transform of a rect is a sinc. Since a sinc is zero at 1/T (in our case around 100GHz), for our range of frequency, we can consider the noise constant of 2ql.

The shot noise can be seen in three device that we have studied: the diode, the mosfet in weak inversion and in a bit because each of them has a pn junction where the current should flow. For each of them, we should define which current takes place. For a diode, we have the shot noise both if forward and reverse biased junction.

For a mosfet in weak inversion we have the current noise at the source-drain terminals:  $S_{3z} = 2q_{3b} = > \left[q_{3m} = \frac{T_{3b}}{\pi \sqrt{3}}\right] = > 2q_{3m} = \frac{N_{3b}}{\sqrt{3}} \Rightarrow \sqrt{4kT} \sqrt{3}q_{3m} = \sqrt{3} + \sqrt{3}q_{3m} = \sqrt{3}q_{3m} =$

For a bit, we have a current from base to emitter and one from collector to emitter. In addition, since there's an ohmic path in the base, we can define a "spreading resistance" (around 250 ohm) that contribuites to the noise with its resistance. Overall, in a bit transistor, we can define three noise contributions. As we have done with a mosfet, we can use the two port theorem to find two single generators that rapresent the noise.

$$S_{OUT} = 2q JQ |\beta|_{+}^{2} 2q Jc = S_{J} |\beta|_{2}^{2}$$

=>  $S_{J} = 2q JQ \left(1 + \frac{1}{\beta}\right) \approx 2q JB$

$$\frac{1}{2} \int_{-\infty}^{\infty} \frac{1}{2} \int_{$$

#### 11. Trapping noise: trapping noise in a resistor (L13C\_24)

In our technology we use doped silicon. This means that we will likely have defects, expecially at the interface, that acts as a centre of recombination and generation. Since the current is proportional to the number of free carriers in a resistor, we can say that 욮 여

When a capture event occur, we register a - AI in the current, while when a emission event occur, we register a - AI. After a while, the defect will emit again (or capture again) the carrier. Since the emission (capture) can take place afer a different amout of time, it can be shown that we can describe it with an exponential function:

Since the current of the noise is a superposition of pulses, we can use what we have derived in the shot noise:

Find the current of the noise is a superposition of pulses, we can use what we have derived in the shot noise:

$$S_{x}(x) = 2\lambda Q^{2} |H(x)|^{2}$$

$$\begin{cases}

\lambda = \beta \frac{NT}{T} & \text{Il Tripping Pole} \\

Q^{2} = (\omega_{x}x)^{2}

\end{cases} = S_{x}(x) = 4\beta N_{x}(\frac{1}{N})^{2} \frac{C}{1+\omega_{x}x} = \sum_{x = 1}^{NT} \frac{\Delta T}{N} \frac{\Delta T}{1+\omega_{x}x} = \sum_{x = 1}^{NT} \frac{\Delta T}{N} \frac{C}{N} \frac{\Delta T}{1+\omega_{x}x} = \sum_{x = 1}^{NT} \frac{\Delta T}{N} \frac{C}{N} \frac{C}{1+\omega_{x}x} = \sum_{x = 1}^{NT} \frac{\Delta T}{N} \frac{\Delta T}{N} \frac{C}{1+\omega_{x}x} = \sum_{x = 1}^{NT} \frac{\Delta T}{N} \frac{\Delta T}{N} \frac{\Delta T}{N} = \sum_{x = 1}^{NT} \frac{\Delta T}{N} \frac{\Delta T}{N} \frac{\Delta T}{N} = \sum_{x = 1}^{NT} \frac{\Delta T}{N} \frac{\Delta T}{N} \frac{\Delta T}{N} = \sum_{x = 1}^{NT} \frac{\Delta T}{N} \frac{\Delta T}{N} \frac{\Delta T}{N} = \sum_{x = 1}^{NT} \frac{\Delta T}{N} \frac{\Delta T}{N} \frac{\Delta T}{N} = \sum_{x = 1}^{NT} \frac{\Delta T}{N} \frac{\Delta T}{N} \frac{\Delta T}{N} = \sum_{x = 1}^{NT} \frac{\Delta T}{N} \frac{\Delta T}{N} \frac{\Delta T}{N} = \sum_{x = 1}^{NT} \frac{\Delta T}{N} \frac{\Delta T}{N} \frac{\Delta T}{N} = \sum_{x = 1}^{NT} \frac{\Delta T}{N} \frac{\Delta T}{N} \frac{\Delta T}{N} = \sum_{x = 1}^{NT} \frac{\Delta T}{N} \frac{\Delta$$

NB: The base current of a bjt is very sensitive to traps because it has to cross the centre of recombination!

PRE; In a resistor V=RI =>

$$I=\frac{V}{R}$$

$\left[ e=\frac{1}{g\mu N} \frac{L}{W\Delta} \right] \Rightarrow> I \ll N$  !

#### 12. McWorther model of the 1/f noise in MOSFETs. Tvidis formula. (L13\_24)

We have found that the power spectral density of the noise caused by defects is  $S_{\Sigma}(g) = N_{T}(\frac{\tau}{N})^{2} \frac{\tau}{1+\omega^{2}\tau^{2}}$ But tau is not a single value! tau depends on where's the energy level of the traps!

We can introduce an additional function g(tau) to rapresent the link between tau and Nt:

$$=>S_{\frac{1}{2}}\int_{t}^{t}\frac{1}{t^{2}}\int_{t^{2}+t^{2}}^{t^{2}}\frac{dN_{T}\left(\frac{\tau}{N}\right)^{2}}{t^{2}}\frac{\frac{\tau}{t^{2}}}{t^{2}}=N_{T}\left(\frac{\tau}{N}\right)^{2}\int_{t^{2}-t^{2}}^{t^{2}}\frac{4(\tau)d\tau}{t^{2}}$$

Now, our goal is to find out what's g(tau).

McWhorther pointed out that in a mosfet, the carriers that travet in the channel can be trapped by defects both at the interface channel-oxide and by tunneling inside the oxide. The average tunneling time is  $(\tau, \kappa e^{x_k})$  where  $\kappa$  depends on the height of the barrier and  $\kappa$  is the capture time for the same energy level of traps.

same energy level of traps.

We can approximate that the traps along the oxide are uniformily distributed, so that  $3N = \frac{NT}{ToX} dX$

The Tsvidis formula help us to use the result of McWhorther in a easier way:

$$N = \frac{C_{ON} V_{OU}}{q} = \frac{C_{ON} V_{OU} \left(V_{OS} - V_{O}\right)}{q} = \frac{K_{A}^{V_{OU}}}{q} =$$

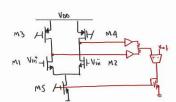

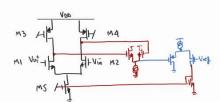

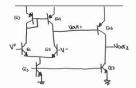

#### 13. The prototypical differential stage: from resistive to active loads. Common mode feedback and single ended option. (L03\_17) 🛟

Our goal is to design a differential amplifier that has an high differential gain and an high Common Mode Rejection Ratio (Gd>>Gcm). To do so, our first step is to design a differential input stage. The easiest circuit we can think is a differential stage with resistive loads:

First of all, we should understand how to set the bias of this circuit: we decide the current that flows in the tail and the overdrive of the two input mosfet (Vov=0.1, the lower the overdrive, the higher gm and so the gain). After that, we may set Vg=Vdd/2 and then we also find the value of Re=(Vg-Vgs)/2I.

Let's now derive the Gd and Gcm to see if this circuit is appropriate.

The differential gain of this stage is given by Gd= gmRL/2. We should underline that we cannot rise RL too

much to amplify the gain, because increasing RL means increasing the voltage drop across it and risk that the mosfet enter the ohmic region. Now we derive the Gcm. In common mode, the input transistors act like source followers, so the current that flows in RE is Vcm/RE. This current will split in half, giving Gcm= RL/2Re. Overall we have:

$$C_{d-mo\cdot x} \leftarrow \frac{q_m}{2} \; R_L : \quad \frac{2\, \text{I}}{\text{Vov}} \quad \frac{\rho_L}{2} : \quad \frac{V_{RL-mox}}{\text{Vov}_{-min}} = \quad \frac{V_{d,\text{New}} \cdot V_T - V_{\text{ORL},\text{bins}}}{\text{Vov}_{-min}}$$

$$Gcm = \frac{R_L}{2R_E} = \frac{IR_L}{2IR_E} = \frac{V_{R_L max}}{V_E} \qquad CMR_E = \frac{G\delta}{Gom} = \frac{V_E}{Vol}$$

NB BOTH Gam, Gd & VL-max

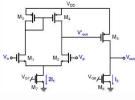

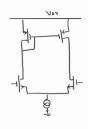

Our main limitation is due to the voltage drop across RL. We should replace them with a device that provides a high impedence indipendent on the voltage drop across it. To do so, we should replace all the resistors with current sources: Let's analyse the differential stage with active loads.

In this case Gd=gm ro/2, that can be set changing the length of the transistor! While Gcm=r0/2rg, giving CMRR=gm\*rg. We have quite good results! But the problem of this stage is setting the bias considering possible mismatch!

We know consider a possible mismatch of M3-M4.

To solve this issue, we introduce a common mode feedback:

Artholly in This way we change Gd, so we should be ...

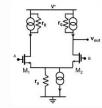

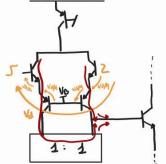

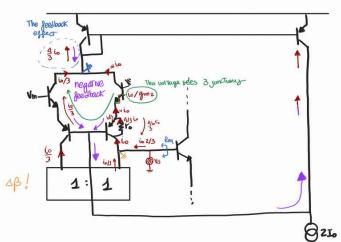

Another way to guarantee that a mismatch between the pair of transistor won't influence the differential gain, is using a differential stage with a mirror, also called single ended configuration (because having the other node at low impedence means that we cannot have a double ended

Let's first show that the mismatch won't cause trubles and then we derive how to set the bias, the voltage swing and gains. Our goal is to demonstrate that Vx (drain of M3) and Vout follow each other. We use a proof by contradiction first and then the math proof.

We suppose that only float if at stealy condition

$$I_{1} < I_{3} = I_{1} < I_{2} \Rightarrow I_{4} < I_{3} \Rightarrow I_{4} < I_{4} \Rightarrow I_{4} \Rightarrow I_{4} < I_{4} \Rightarrow I_{4} \Rightarrow I_{4} < I_{4} \Rightarrow I_{4} \Rightarrow I_{4} \Rightarrow I_{4} < I_{4} \Rightarrow I$$

For the bias we set the current of the tail (according to noise requirements) and we decide mosfet overdrives (both based on dynamics and noise). Some values may be I\_tail=50um, Vov\_1=0.1V, Vov\_3=0.2V, Vov\_5=0.2.

Now let's study the dynamics considering Vcm=1.5V and Vout=2.2V(Vdd-Vgs3):

To derive the differential gain, we use Norton Theorem. This theorem says that G = icc \* Rout Finally, we derive Gcm, still given by icc \* Rout

#### 15. Input referred noise sources of a differential stage with MOSFETs and BJTs. Power-noise trade-off. () 🍖

In theory, an OTA is not a two port network because Vout(vd,vcm), but under the assumption of CMRR->inf, we can consider it a two port network and derive the input referred noise. We will use the split theorem to analyse all the noises.

Overall, the noise set a minimum current for the bias!

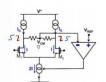

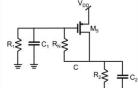

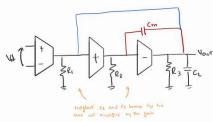

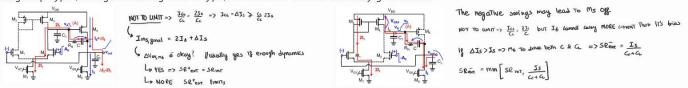

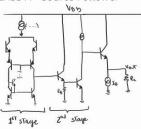

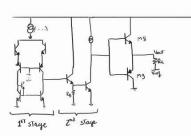

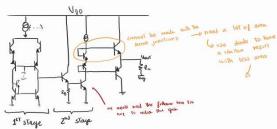

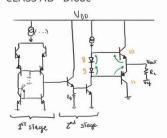

First of all, we derive the overall circuit and how to set the bias. We saw that increasing the channel lenght (to increase the gain) both influence the area needed and the cut-off frequency decrease. Not to limit the speed of the circuit, we decide to use an additional stage, a common source to gain what we need.

Since the circuit has two high impedence nodes, at the output of the frist and second stage, there's a risk to have two poles before the GBWP! Because of that, we need a proper compensation. Let's first analyse the Miller Compensation:

$$\Gamma(s) = gm_1 Rout_1, gm_2 Rout_2 = \frac{a_1 s + 1}{b_1 s^2 + b_2 s + 1}$$

$$\frac{Vs}{\tilde{c}s} = \frac{1}{qm}$$

\bs=CR\(\frac{0}{0}\) + CoR\(\frac{0}{0}\) + CoR\(\frac{0}{0}\) = COR\(\frac{0}{0}\) + CoR\(\frac{0}\) + CoR\(\frac{0}{0}\) + CoR\(\frac{0}\) + CoR

$$\begin{cases} \frac{1}{2\pi} = \frac{1}{2\pi (cm^2 L(1+qm_5 E_2))} \\ \frac{1}{2} = \frac{qm_5}{2\pi (cm_5)} \end{cases} = \Rightarrow GBWP < \frac{1}{2} = \Rightarrow Cm > \frac{qm_5}{qm_5} (G_1+C_L) \\ \frac{1}{2} = \frac{qm_5}{2\pi (cm_5)} (4) \\ \frac{1}{2} = \frac{qm_5}{2\pi (cm_5)} (4) = \frac{qm_5}{2\pi (cm_5)} = \frac{qm_5}{2\pi (cm_5)$$

Having Is> Iz => move fe, ft at HF Increasing Cm => move fz,60WP down

#### 17. Two-stage CMOS OTA: frequency compensation with the nulling resistor. Implementing the nulling resistor. (L06\_19) 2.

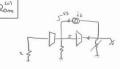

The Miller compensation solves the compensation problem but in some cases the power penalty is not acceptable. The main problem is due to the positive zero that contribuites like a pole in the phase margin. The first and intuitive way to make the zero negative, is to add a resistance in series to the Miller capacitance. Let's study again where the zero and the poles are:

$$\frac{2ero}{R\omega + \frac{1}{SC_{m}}} = Vs \ qms \Rightarrow S^{\pm} - \frac{1}{C(R\omega - \frac{1}{qms})} \Rightarrow g_{2} = \frac{1}{2\pi Cm(R\omega - \frac{1}{qms})}$$

There are two ways of implamentation of Rn: the first is to bring fz to infinite (do not do that, there's variability in fabrication), or to use it to make a zero-pole cancellation with the second pole. (THE DOUBLES ALWAYS AFTER THE GBWP if possible).

$$g_{m_1} v_d = \begin{cases} R_1 & C_1 \\ R_2 & C_3 \end{cases}$$

Now there are three poles since the capacitors are indipendent and interactive. Since the pole due to the miller capacitor is way lower than the others, we can consider Cm as short when computing the other two.

$$\frac{1}{\tau_{\text{true}_{1},5}} = \frac{1}{2} \frac{1}{\tau_{\text{true}_{1},5}} = \frac{1}{2} \frac{1}{\tau_{\text{true}_{1},5}} + \frac{1}{\tau_{\text{true}_{1},5}} + \frac{1}{\tau_{\text{true}_{1},5}} + \frac{1}{\tau_{\text{true}_{1},5}} + \frac{1}{\tau_{\text{true}_{1},5}} = \frac{1}{\tau_{\text{true}_{1},5}} + \frac{1}{\tau_{\text{true}_{1},5}} +$$

Note that Rn is often implemented with a MOS transistor in ohmic regime

#### 18. Two-stage CMOS OTA: frequency compensation with ideal voltage and current buffers. Impact of the buffer finite resistance. (L06\_19) 🛸

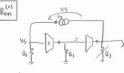

Another way to remove the zero in the Miller Compensation is to stop the current in the Cm brench. There are two ways: using a voltage buffer or a current buffer. We first analyse the two ways considering them ideal. (Ideal case -> interactive and not independent)

Now we discuss the impact of a buffer finite resistance. The capacitors, because of the source resistance, become indipendent and interactive and the zero re-appears!

Let's assume that what we derive from MOSFET works with BJT. We use at first the same configuration of the MOSFET OTA and see its parameters:

$\mathcal{E} = \frac{\Lambda}{qm_3r_{03}} + \frac{1}{qm_3r_{02}} + \frac{2}{\beta} \approx \frac{2}{\beta}$  (need to improve million) => CMRR =  $\frac{2qm_1r_{02}}{\mathcal{E}}$

#### RE SISTANCE

Rd= ZFT = ZBAPA

Ram = 2 rog Bripn

### NOISE

### SIZN6

In a bipolar OTA, we could start with the same input differential MOSFET stage, but then we will occur in a trade-off. The input resistance (that a MOSFET has infinite because of the gate) is finite, of 2Rpi. Since Rpi is proportional to beta, we would like to have a npn as an input stage. In trade off with this requirement, there's the CMRR that, in this case, is the mirror error, since the current bias needed is 2/beta. So, also in this case, we would like to have a npn mirror to decrease the error. Having input bjt and mirror as npn, keeping the output node with an high impedence, means that we should add a current buffer in between.

Now we encounter another problem: A bjt should have a base current to be biased, not a voltage. We then have to build a feedback network to bias it properly. (if we bias with voltage, the current will change as e^Vb)

If we decide to bias with a normal current generator, we have a problem that beta is found after the fabrication and the current won't be decided by us but by variability fabrication. We build a feedback in order to have a stable current in our brench with a small error:

$$\begin{cases} 2I_{L}(1-\xi)+2I_{0}=2I_{0} \\ 2I_{L}=2I_{0}\left(\beta_{f}+1\right)\frac{\beta_{n}}{d_{n}} & \Rightarrow 2I_{0}\left(1+\left(\beta_{f}+1\right)d_{n}\left(1-\xi_{f}\right)\right)=2I_{0} \\ \downarrow_{J_{0}}=\frac{I_{L}}{d_{n}} & \Rightarrow 2I_{0}=\frac{2I_{0}}{1+\left(\beta_{f}+1\right)d_{n}\left(1-\xi_{f}\right)} & \Rightarrow I_{L}=\frac{\left(\beta_{f}+1\right)d_{n}}{1+\left(\beta_{f}+1\right)d_{n}\left(1-\xi_{f}\right)} & \Rightarrow I_{L}=\frac{A}{1+AF} \end{cases}$$

$$\Rightarrow \frac{I_{L}}{\left(\beta_{f}+1\right)d_{n}}=\frac{I_{0}}{\left(\beta_{f}+1\right)d_{n}\left(1-\xi_{f}\right)} \Rightarrow I_{L}=\frac{A}{1+AF} \end{cases}$$

$$\Rightarrow \frac{I_{L}}{\left(\beta_{f}+1\right)d_{n}}=\frac{I_{0}}{\left(\beta_{f}+1\right)d_{n}\left(1-\xi_{f}\right)} \Rightarrow I_{L}=\frac{A}{1+AF} \end{cases}$$

$$G = \frac{A}{1+AF}$$

$$= \begin{cases}

dG = \frac{dG}{dA} & A + \frac{dG}{dF} & A = \frac{dG}{dF} & A = \frac{A^{2}}{(1+AF)^{2}} & A^{2} & A^{$$

The same issue can be also solved with a Darlinton stage using pnp as input stage, without the need of this feedback brench. The drowback of the Darlinton is the input noise amplified by B^2.

Once we set the current buffer, we may decide to improve also the CMRR because the mirror error is still degrading it. To improve it, we have at least two solutions: using a mirror with an emitter follower or a Wilson's mirror. Let's analyse the first solution.

dince The current of the bleeding restations. Now, Thor's a risk of \$11 The bleeding restations.

Offer an alternative path and help to montain the Jessus current (NO Veb is gixed 0,7V) (We gix Bo in order to have the right ammount of current)

Let's now analyse a Wilson's Mirror:

$$Rin = \frac{\frac{2\beta}{m}hr_0}{1 - 6loop} = \frac{\frac{2\beta}{m}}{\beta} = \frac{2}{guw}$$

$$\widehat{\text{Rev}} = \frac{\beta t_0}{2} \left( \text{with Unegar} \right)$$

$$\widehat{\text{Otherwise}} \left( t_0 + \frac{1}{6p_0} \right) \left( 1 + \beta \right) \approx t_0 \beta \left( \text{appex} \right)$$

Now, let's derive the differential gain and the output resistance:

#### 21. uA741 second stage. Setting the bias: trade-off between gain and input impedance. Frequency response. (L068 15) 🐛

After the single differential stage, we need to add a second stage that gain. The uA741 is designed to have a resistive load, so after a gain transistor, we place an emitter follower as a buffer, in order to have a low resistance output.

The second gain is given by gm11\*Rout11

Since the gain depends on the load resistance, we should ask for a minimum one that the user should use.

$$G_2 = q_{m_{2.5}} \cdot \beta_{mp} \cdot \beta_{L_m in} \implies q_{m_{2.5}} \gg \frac{G_2}{\beta_{mp} \cdot \beta_{L_m in}} \qquad q_{m_{2.5}} \uparrow \longleftrightarrow R_{1n_2} \downarrow \qquad R_{1n_2} = \frac{\beta_{m_{ph}}}{q_{m_{11}}}$$

As we see, we end up with a minimum gm required, that may degrade Rin2. We should remember that in order not

As we see, we end up with a minimum gm required, that may degrade Rin2. We should remember that in order not to degrade the gain of the first stage, we need to have Rin2>Rout1. Then we should add an emitter follower.

NB: We should also add a "bleeding resistance" in order to have bias properly Q11 and avoid Q10 operating in low injection regime. We also achive an important result: we reach the symmetry of (B) and (A)!

Placing an emitter follower degrades the gain a little bit (0.9) but it's needed for the input resistance.

Now we check the frequency response of the circuit. Since we have two high impedence nodes (A) and (C), we expect to have two main pole in the transfer function. Ca = Ccoll-sub(4-9) (not Q10 because follower and the voltage across the capacitor is constant) and Cc = Cmu(11). Since both the capacitors and the resistances they see are in the same order of magnitude, a compensation is needed.

We place the compensation capacitance C between node (A) and (C). In this case the Miller compensation is fine because we had to increase the current of the second stage to fulfill the gain.

## 22. Single-stage CMOS OTAs: telescopic cascode topology, differential gain, input and output voltage swing, power dissipation, frequency response. (LEZ 20, LO7\_19, ESE 14)

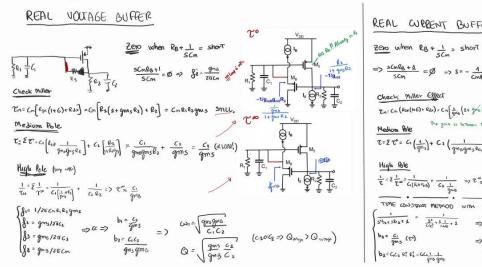

The main problem of a two stage amplifier, even if it has beautiful performance, is the need for compensation. We try now to find a way to elaborate a single stage amplifier so that we have just a single dominant pole and the speed of it is increasing, in trade off, maybe, with other performances. The first configuration we finds, comes from the natural flow of implementing the first stage of the two stage amplifier.

Our major issue, is to reach the proper gain, and to do so, we implement Rout with two cascode stage, one on top of the mirror, with an additional mirror, and one with a common gate on the bottom. (We need two cascodes because Rout is given by Rtop//Rbottom and we need to improve both in order to see the result on the output). This improvement gives birth to the <u>Telescopic cascode amplifier</u>.

Let's caluculate the overall Rout and then we will try to catch the CONS of this config:

As we saw, the gain is large enough, but the real "issue" is the input and output swing (that is caused but he series of many transistors), since the upper voltage input and the lower voltage output both depends on Vb. This configuration works quite well in an inverting configuration with feedback, but for buffers or other, the performance are very poor.

Let's now look at the frequency response:

## 23. Folded cascode topology, enhanced mirrors, voltage dynamics, power dissipation. Folded cascode with bipolar transistors. Feed-forward compensation. (LEZ 20, LO7\_19, ESE 14)

Since the telescopic cascode has a poor dynamics, we now look for a config with a larger swing. We change the configuration using pmos, giving birth to the Folded Cascode Amplifier.

Let's see if it still has an high gain and how the voltage swing changed:

As we can see, the voltage range improved a lot, but we payed for power consumption: now we have two different brenches that dissipate!! We can easily evaluate that the power consumption is at least twice as the telescopic (2\*2I Vdd) because the second brench needs at least the same current of the first one, here's why: considering the case where Vcm>> and all the current of the first stage flows in M1, we would first switch off M3 and then require current from it in opposite direction! Since this case is not possible, M1 enters in ohmic region to let less current and the node (A) will go down. In case we change the input again, in order to have a functional circuit, we have to wait a certain

amount of time to let M1 re-enter in the saturation region and to fix the potential of (A) to have a proper output. Not to have this, we want that Ig + I2 >= 2I1, so I2 is at least equal to I1.

Apart from this lost in performance in power dissipation, this folded stage works well, but we can improve the voltage swing even more!

We can add an additional reference voltage so that M7 and M8 works with the minimum Vds and the source potential od M5 and M6 is even lower.

We call this configuration Folded Stage with Enanched Mirror or simply the Enanched Mirror Stage:

For both these two configurations, we can study the frequency response. Taking to account a capacitive load CL, we can evaluate the poles in DC given by all the capacitors.

From this fast deduction, we can expect that these configurations have just a single pole due to the load capacitor and the other Cgs capacitors, once the load is short circuited, give a pole contribution very far away. We will see that this won't happen in the bjt configurations.

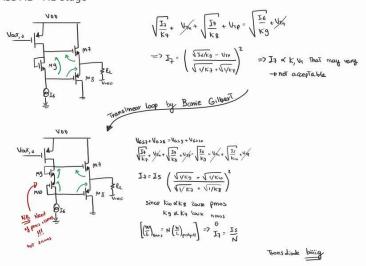

Let's now derive the Folded Cascode with BJT.

The output resistance can be derived easily, but now we encounter a big problem! Since the cut frequency of pnp is quite low, it may happen that ft<GBWP and in that case, our amplifier won't work anymore. That's why we need to introduce the Feedforward Compensation

#### 24. Three-stage CMOS OTA: Nested Miller Compensation (L08\_23)

For some application we need very high gain (120dB) and as the supply voltage decrease (tech scales down), we cannot use cascode structure because of the limited voltage rage. The other solution is to add another stage to gain. Three stages means three node with high impedence ad a required compensation. As we will see later, the first stage has to be differential, the second one non inverting and the third one inverting.

We start from the usual Miller Compensation only considering the second and third stage:

Now we use another Miller compensation between Cm and C1:

$$\begin{array}{lll} \text{SIBING EX:} & & & \\ \text{GBMQP=SMAQ} & = & & \frac{Gma}{2\pi G} = & \text{40 GBMPP} = & & Gm_b = 1,6 \text{ m} \text{ A/V} \\ \text{CL=SpF} & & & & \\ \text{Gm_2} = & & Gm_b/S = & 0,5 \text{ m A/V} \\ & & & & & \\ \text{GPMQP} = & & & & \\ \frac{Gm_b}{2\pi G_{\text{CM}}} = & & & \\ \text{GPMQP} = & & & & \\ \frac{Gm_b}{2\pi G_{\text{CM}}} = & & & \\ \text{GPMQP} = & & & \\ \frac{Gm_b}{2\pi G_{\text{CM}}} = & & & \\ \text{GPMQP} = & & & \\ \frac{Gm_b}{2\pi G_{\text{CM}}} = & & & \\ \text{GPMQP} = & & & \\ \frac{Gm_b}{2\pi G_{\text{CM}}} = & & & \\ \text{GPMQP} = & & \\ \frac{Gm_b}{2\pi G_{\text{CM}}} = & & \\ \text{GPMQP} = & & \\ \frac{Gm_b}{2\pi G_{\text{CM}}} = & & \\ \text{GPMQP} = & & \\ \frac{Gm_b}{2\pi G_{\text{CM}}} = & & \\ \text{GPMQP} = & & \\ \frac{Gm_b}{2\pi G_{\text{CM}}} = & & \\ \text{GPMQP} = & & \\ \frac{Gm_b}{2\pi G_{\text{CM}}} = & & \\ \frac{Gm_b}{2\pi G_{$$

Now we derive the whole transfer function with the time constant method:

$$T(s) = T(o) \frac{s^{4} \delta_{24} + s \delta_{14}}{(2+s^{4} \zeta_{1})(s^{4} \delta_{24} + s \delta_{14})}$$

$$b_{4} = C_{mn} R_{m}^{(o)} + C_{1} Q_{1}^{(o)} = C_{m} \frac{G_{my} C_{mx}}{G_{my} G_{mx}} + C_{1} \frac{1}{G_{my} G_{my}} \frac{C_{m} G_{my} - G_{mx}}{G_{my} G_{mx}}$$

$$b_{2} = C_{mn} C_{1} R_{m}^{(o)} R_{1}^{(o)} = C_{1} C_{1} \frac{G_{my} G_{mx}}{G_{my} G_{mx}} \frac{1}{G_{my} G_{mx}} = \frac{C_{m} C_{1}}{G_{my} G_{my}} \frac{C_{m} G_{my} - G_{mx}}{G_{my} G_{mx}}$$

$$= 7 \left( \frac{C_{1} C_{1} C_{1} C_{1} C_{1} C_{2} C_$$

$$E_{t}^{(a)} = \frac{V_{3}}{\hat{C}_{3}} \otimes \frac{1}{\hat{E}_{1} \otimes \hat{E}_{1}} \times \frac{V_{3}}{\hat{E}_{3}} + \frac{V_{4}}{\hat{E}_{1}}$$

$$E_{t}^{(a)} = \frac{V_{3}}{\hat{C}_{3}} \otimes \frac{1}{\hat{E}_{1} \otimes \hat{E}_{1} \otimes \hat{E}_{1}}$$

$$V_{5} = V_{5} - V_{5} + U_{5} + \frac{1}{6m_{5}} = \frac{4}{6m_{5}} = \frac{V_{5}}{C_{5}} = \frac{1}{6m_{1}} \frac{1}{6m_{1}} \frac{1}{6m_{3}} \frac{6m_{1} - 6m_{1}}{6m_{3} - 6m_{2}} = \frac{1}{6m_{2} - 6m_{3}} \frac{1}{6m_{3} - 6m_{2}} \frac{1}{6m_{3} - 6m_{2}} \frac{1}{6m_{3} - 6m_{2}} \frac{1}{6m_{3} - 6m_{2}} \frac{1}{6m_{3} - 6m_{3}} \frac{1}{6m_{3}} \frac{1}{6m_{3} - 6m_{3}} \frac{1}{6m_{3}} \frac{1}{$$

$$L_{A} = C_{an} R_{onn}^{(a)} + C_{M} R_{on}^{(a)} = C_{m} \frac{1}{G_{mi} g_{mi} g_{k}} + C_{M} \frac{1}{G_{mi}} \approx \frac{-C_{M}}{G_{mi} g_{k}}$$

#### 25. OTA Linear response. In-band zero-pole doublets and features of the settling response. (LEZ 21, LO9 21) 🍆

In Analog Circuit Design, in-band zero-pole doublets refer to a pair of closely located zeros and poles in the frequency response of our interest (before GBWP). These can derive from an error in a slightly different value of C\_laod that can lead to a split of a perfect zero-pole cancellation or from a feed-forward compensation. We can devide the study in two cases: the zero comes before of after the pole of the doublet. At first impact we may say that, since they are very close, their effect nearly cancel out in the magnitude response and the gain has a minimal alteration, not giving any issues, but it actually degrades the transient response of the circuit.

Let's first study the case of pole-zero-pole:

The transfer function of an amplifier with two poles and a zero can be written as (a), with a closed loop transfer function as (b), and as we know, the zero of the open and closed loop are the same, but the poles will vary and we need to calculate them.

A(s) = Ao (1+ ST2) (1+5To) (1+5Tp)

The root locus will help us to see the relative position of the new poles. As the Gloop increase, the low frequency pole will approch the zero, while the high frequency one will moves approching GBWP. From this we can see that if the doublets is at low frequency, with the right gain, we will have a pole of the close loop at the frequency of the zero. We have to figure out whenever we prefer the doublet at low or high frequency and its relative

effect on the transient.

Let's now study the response of this stage to a step function E. In Laplace domain we can write:

Now we want to estimate the two poles:

W WE WANT TO ESTIMATE THE TWO POLES:

$$\frac{A(s)}{1+A(s)} = \frac{A(s)}{1+A(s)} = \frac{A(s)}{$$

At first, we may say that we want fz<<GBWP so that A is high and the fast pole covers the majority of the exponential, but if we think twice, we notice that the slow pole has a proportional dependency with fz, so if we try to increase the velocity of the fast pole, we slow down the slow one! Overall we will have a worse solution! (also because due to fab errors, A may appear bigger than expected and the slow pole not be so marginal) We find out that it's actually better to have an high frequency zero pole so that the fast pole covers a small portion of the exponential (but still quite fast) and the slow pole, overall, not so slow.

Let's now study the case of pole-pole-zero:

5: Per Tmin At e atta Sovieelongazione, puó esp scupe il sistemo

Now as Ao increase, the poles become complex conjugate. For large values of Ao, the poles become real again. The response of the sistem has an overshoot whose amplitude depends on the distance between the pole and the zero of the doublet (since the position is not so precise, you should avoid this config). The system will settle down with the slow pole, so, once again, we want the slow pole to be faster as possible, with a fz at high frequency

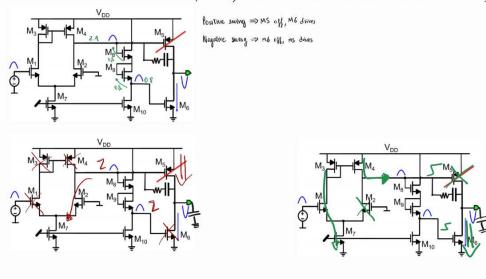

For what concern the time response of a real amlplifier, we should take into account, in adddition to doublets, the slew rate. The slew rate describes how quickly the output node can vary in response to a rapid change of the input. Let's study the SR of a CMOS-OTA, considering first the internal slew rate and then how the external slew rate should be in order not to limit the circuit performance.

The internal slew rate is related to the first stage and the maximum current it can provides to charge the capacitors. We can study seperatly the upper and lower SR (even if they are the same for a standard OTA due to the symmetry of the differential stage). Imaging a large positive input, the situation is the one in figure:

The external slew rate upper and bottom are very different. Let's focus on the one that doesn't give problems first: positive swing when the second stage is p-type (or negative swing with n-type). On the side the one that may give issues.

If we want to have a better external SR, we may build an AB circuit that raise the current of M6 only on negative swings (power consumption!):

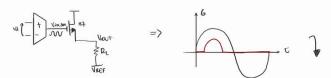

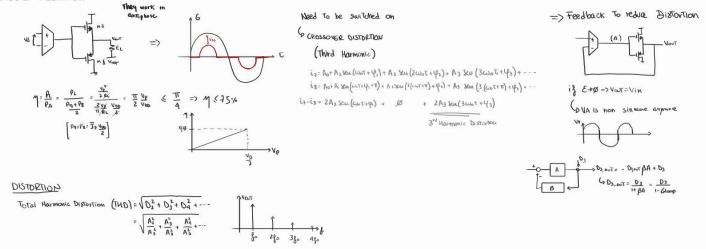

## 27. Output stages: Emitter follower as output stage. Emitter follower efficiency. Push-pull. Efficiency. Cross-over distortion. Class A-B stage. Total harmonic distortion. Distortion reduction by feedback. (L11\_21)

When we have a resistive load, our OTA cannot be used! This is due to the fact that the OTA has an high impedence not ad connecting it to a low resistive load will degrade the gain. We should add an additional stage to decouple the gain and the output. The first configuration we can think about is a simple source follower.

CLASS A - Source Follower

Thinking a way to reduce the static power to improve power efficiency is to use a ideal source follower. CLASS B - Ideal Source Follower

We noticed that we need to add a transistor switching on for negative swing:

CLASS B - Push Pull

The crossover distortion is due to the fact that the mosfet are not biased yet. We can implement the circuit in order to have a almost on mosfet. CLASS AB - AB stage

Let's start with the same idea of MOSFET:

### CLASS A - Source Follower

Being a Class A, we already saw that the power consumption is way too much, giving a low power efficiency. We adopt the second idea with push-pull CLASS B - Push Pull

#### CLASS AB - Transdiode

### CLASS AB - Diode

$$\begin{cases} V_{08} + V_{09} = V_{0E_{11}} + V_{0E_{10}} \\ I_{z} I_{z} & \mathcal{C}^{\frac{1}{9}\frac{6}{12}} = V_{0E_{1}} & \frac{k_{1}}{q} I_{u} I_{z} \\ I_{z} I_{z} & \mathcal{C}^{\frac{1}{19}\frac{6}{12}} = V_{0E_{1}} & \frac{k_{1}}{q} I_{u} I_{z} \\ I_{z} I_{$$

is=J,A

We compensale Temperature shift! Good!,

§ \$(5) and 11(10) make

We compensale Temperature shift! Good!,

January 12 some prece

January 13 som

One and Qn are already big to correy large cigard.

If we want to reble the bids current of sain-we would

#### CLASS AB - Vbe multiplier (to save area)

Vice ≈ 2VGE (5 Tuning R, we can have lige « lig => Vice, ge < Vice,

More strong against Temperature shift

#### CIRCUIT PROTECTION

Since the output node and the load is connected outside, we should consider some protection not to ruin Q10 and Q11

#### 29. Variability and matching: Relative matching of threshold voltage values. Common centroid. Pelgrom's formula (L10\_16)

In our circuits we have always taking in to account that pair of transistors (input, mirror) are idential. The truth is that there may be have some systematic errors and statistical errors.

Systematic error are caused by a gradient along a direction, for example, an hot spot of a circuit may cause a temperature gradient, a process production non uniformity may cause a gradien in tox,...

These systematic errors are solved with the common centroid technique: the gradient can be splitted in a gradient along x and a gradient along y. We can rearrange our devices in order to derive a mean value.

Statistical errors are caused by the flactuations of some parameters in time and the fact that we cannot precisely calculate some parameters in each point, such as dopants. We have to use a statistical approch to study them and find its variance.

Taking a MOSFET, the statistical parameters that can flactuate are the number of carriers (dopants) that cause a variation in the threshold and the mobility (and so k).

Let's study the statistical variation of the threshold first.

As we derived for Vt, the same calculation can be derived for k, finding an analog Pelgrom coefficient for it.

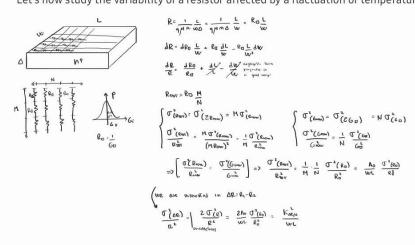

#### 30. Variability and matching: Relative matching of resistors. Common centroid. Pelgrom's formula (L10\_16) 🚜

In our circuits we have always taking in to account that pair of transistors (input, mirror) are identical. The truth is that there may be have some systematic errors and statistical errors.

Systematic error are caused by a gradient along a direction, for example, an hot spot of a circuit may cause a temperature gradient, a process production non uniformity may cause a gradien in tox,...

These systematic errors are solved with the common centroid technique: the gradient can be splitted in a gradient along x and a gradient along y. We can rearrange our devices in order to derive a mean value.

Statistical errors are caused by the flactuations of some parameters in time and the fact that we cannot precisely calculate some parameters in each point, such as dopants. We have to use a statistical approch to study them and find its variance. Let's now study the variability of a resistor affected by a flactuation of temperature or dopants.

# 31. OTA: Offset. Deterministic and statistical contributions to input referred offset. Input referred offset in bipolar differential stages. Temperature effects. (L09B\_19)

Let's analyse the differential input stage with MOSFET and derive how a mismatch of Vt,k of input (mirror) pair of mosfet:

In BJT

$$I = J_{S}e^{q_{NR}}e^{q_{NR}} = q \frac{o_{N} n_{s}^{2} A_{F}}{(v_{0}v_{0})}e^{q_{NR}}e^{q_{NR}}$$

$\Rightarrow$  Temperature. Shift balanced with common centroid so the system work with The "same" Temperature.

$$\begin{cases} I_{4} = (I_{3} + \Delta I_{3}) e^{\frac{q^{1} dgc}{rr}} \\ I_{Lz} = I_{5} e^{\frac{q^{1} dgc}{rr}} \end{cases} \Rightarrow \Delta I = \Delta I_{5} e^{\frac{q^{1} dgc}{rr}}$$

$$\begin{cases} I_{5} = n \\ I_{4} = n \end{cases} \Rightarrow \Delta I = \Delta I_{5} e^{\frac{q^{1} dgc}{rr}}$$

$$\begin{cases} I_{5} = n \\ I_{4} = n \end{cases} \Rightarrow \Delta I = \Delta I_{5} e^{\frac{q^{1} dgc}{rr}}$$

$$\begin{cases} V_{05} = \frac{\Delta I_{5}}{I_{5}} e^{\frac{q^{1} dgc}{rr}} \\ V_{05} = \frac{\Delta I_{5}}{I_{5}} e^{\frac{q^{1} dgc}{rr}} \end{cases}$$

$$V_{05} = \frac{\Delta I_{5}}{I_{5}} e^{\frac{q^{1} dgc}{rr}}$$

$$V_{05} = \frac{\Delta I_{5}}{I_{5}} e^{\frac{q^{1} dgc}{rr}}$$

$$V_{05} = \frac{\Delta I_{5}}{I_{5}} e^{\frac{q^{1} dgc}{rr}}$$

We have already derived (in DC) the value of an important parameter in our circuit: the CMRR. The Common Mode Rejection Ratio is the ratio between the the differential and the commmon mode gain and it's important because an high CMRR means a good signal accuracy and a rejection of DC noise. Until know we have taken into account the DC value, but we should take into account that the common mode gain has a zero that the differential doesn't have, so at medium-high frequency, the CMRR drops down and may cause errors!

CMRR can be devided in the deterministic one and the statistical one.

The deterministic CMRR is due to the mirroring error and the difference of load seen by the input:

The statistical CMRR is due to the mismatch of mirrors and mismatch of inputs mosfet (gm):

Since the variation of gm is statistical, we should study it's variance:

$$\frac{\partial g_{1}}{\partial V_{1}} = \frac{\partial G_{1}}{\partial V_{1}} \Delta V_{1} + \frac{\partial g_{1}}{\partial V_{2}} \Delta K = 2K\Delta V_{1} + 2V_{0}V \Delta K$$

$$\frac{\partial g_{1}}{\partial V_{2}} = \frac{2K\Delta V_{1}}{2KV_{0}} + \frac{2\Delta KV_{0}}{2KV_{0}} = \frac{\Delta V_{1}}{V_{0}} + \frac{\Delta K}{K}$$

$$\frac{\partial g_{1}}{\partial V_{2}} = \frac{2K\Delta V_{1}}{2KV_{0}} + \frac{2\Delta KV_{0}}{2KV_{0}} = \frac{\Delta V_{1}}{V_{0}} + \frac{\Delta K}{K}$$

$$\frac{\partial g_{1}}{\partial V_{2}} = \frac{2K\Delta V_{1}}{2KV_{0}} + \frac{2\Delta KV_{0}}{V_{0}} + \frac{\Delta V_{1}}{K}$$

$$\frac{\partial g_{1}}{\partial V_{2}} = \frac{\Delta g_{1}}{V_{0}} + \frac$$